本博文主要交流设计思路,在本博客已给出相关博文约110篇,希望对初学者有用。注意这里只是抛砖引玉,切莫认为参考这就可以完成商用IP设计。

(a)请求状态机

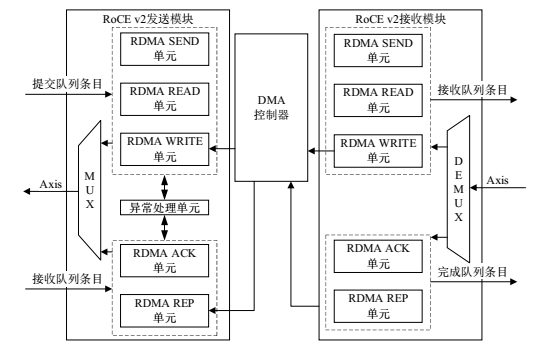

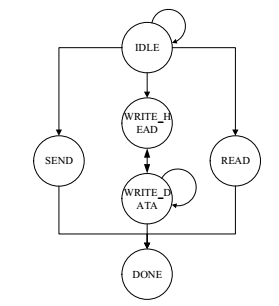

当 RoCE v2 发送模块检测到发送队列非空时,则从发送队列中读取一个发送队列条目,并判断请求类型。根据不同的请求类型和请求长度进入不同的包生成流程,这一过程由请求状态机实现。请求状态机的状态转移图如图 1 所示,对于各个状态的详细说明如下。

图1 请求状态机状态转移图

IDLE:空闲状态,系统复位后请求状态机将进入 IDLE 状态。当检测到发送队列非空时,从发送队列中读取出一个发送队列条目并分析其请求类型,并根据不同的请求类型跳转到不同的后续状态。对于 SEND 指令,跳转至 SEND 状态;对于 READ指令,跳转至 READ 状态;对于 WRITE 指令,跳转至 WRITE_HEAD 状态。如果请求类型不合规,则保持在 IDLE 状态并返回错误信息。如果发送队列为空,则保持在IDLE 状态等待指令。

SEND:SEND 指令发送状态。在该状态下将调用 SEND 单元根据系统中提前预设好的信息发送 SEND 数据包,数据包内容包括本机 IP 地址、本机 MAC 地址、本机内存起始地址、本机内存大小和本机远程访问密钥。发送完毕后跳转至 DONE 状态。

READ:READ 指令发送状态。在该状态下状态机将调用 READ 单元根据用户指令中的请求远程地址、请求数据长度及远程主机访问密钥来组装 READ 包头部,READ 请求包中并不携带数据信息。发送完毕后跳转至 DONE 状态。

WRITE_HEAD:WRITE 指令头发送状态。在该状态下状态机将调用 WRITE 单元根据用户指令中的远程请求地址、请求数据长度及远程主机访问密钥来组装WRITE 包头部。同时将请求数据长度与以太网单数据帧最大长度进行比较,如果请求长度超过单数据帧最大程度,则 WRITE 包头部中的操作类型被置为 FIRST/MIDDLE/LAST;反之 WRITE 包头部中的操作类型被置 ONLY。同时将用户指令中

的本地数据起始地址和请求数据长度通知给 DMA 控制器,而后跳转至 WRITE_DATA状态。

WRITE_DATA:WRITE 指令数据发送状态。在该状态下将持续等待 DMA 控制器返回用户需要发送的数据,在数据到来后,将数据组装进 WRITE 数据包中,直到达到以太网单数据帧最大长度。而后对数据长度进行判断。如果数据已发送完毕,则跳转至 DONE 状态;如果仍有数据未发送完毕,则跳转回 WRITE_HEAD 状态,重复 WRITE 数据包发送流程。若请求数据超时,则返回 IDLE 状态并返回异常完成条目。

DONE:请求完成状态。该状态下将发送寄存器中剩余的最后一帧数据并生成指令完成信号。在一个时钟周期后回到 IDLE 状态。

B站已给出相关性能的视频,如想进一步了解,请搜索B站用户:专注与守望

https://www.bilibili.com/video/BV1mPV5eCE8z/?spm_id_from=333.337.search-card.all.click&vd_source=c355545d27a44fe96188b7caefeda6e7

审核编辑 黄宇

-

CMAC

+关注

关注

0文章

11浏览量

11370 -

RDMA

+关注

关注

0文章

102浏览量

9666

发布评论请先 登录

RDMA设计46:RoCE v2原语功能:单边语义

RDMA设计44:RoCE v2原语功能验证与分析

RDMA设计37:RoCE v2 子系统模型设计

RDMA设计33:RoCE v2 接收模块

RDMA设计32:RoCE v2 发送模块4

RDMA设计29:RoCE v2 发送及接收模块设计2

RDMA设计28:RoCE v2 发送及接收模块设计

RDMA设计20:RoCE v2 发送及接收模块设计2

RDMA设计19:RoCE v2 发送及接收模块设计

RDMA设计5:RoCE V2 IP架构

RDMA over RoCE V2设计2:ip 整体设计考虑

RDMA over RoCE V2设计1:为什么要设计它?

RDMA设计30:RoCE v2 发送模块2

RDMA设计30:RoCE v2 发送模块2

评论