一、Efinity工程 io_memoryClk是与存储器接口共用的时钟,需要连接正确。 UART ....

TJ375已经支持PLL的动态配置。打开PLL在Advance Settings中的Dynamic ....

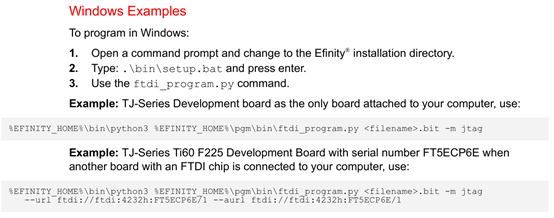

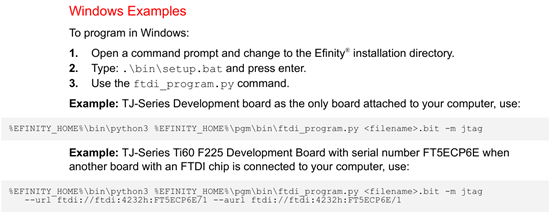

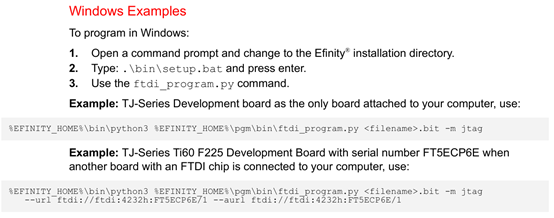

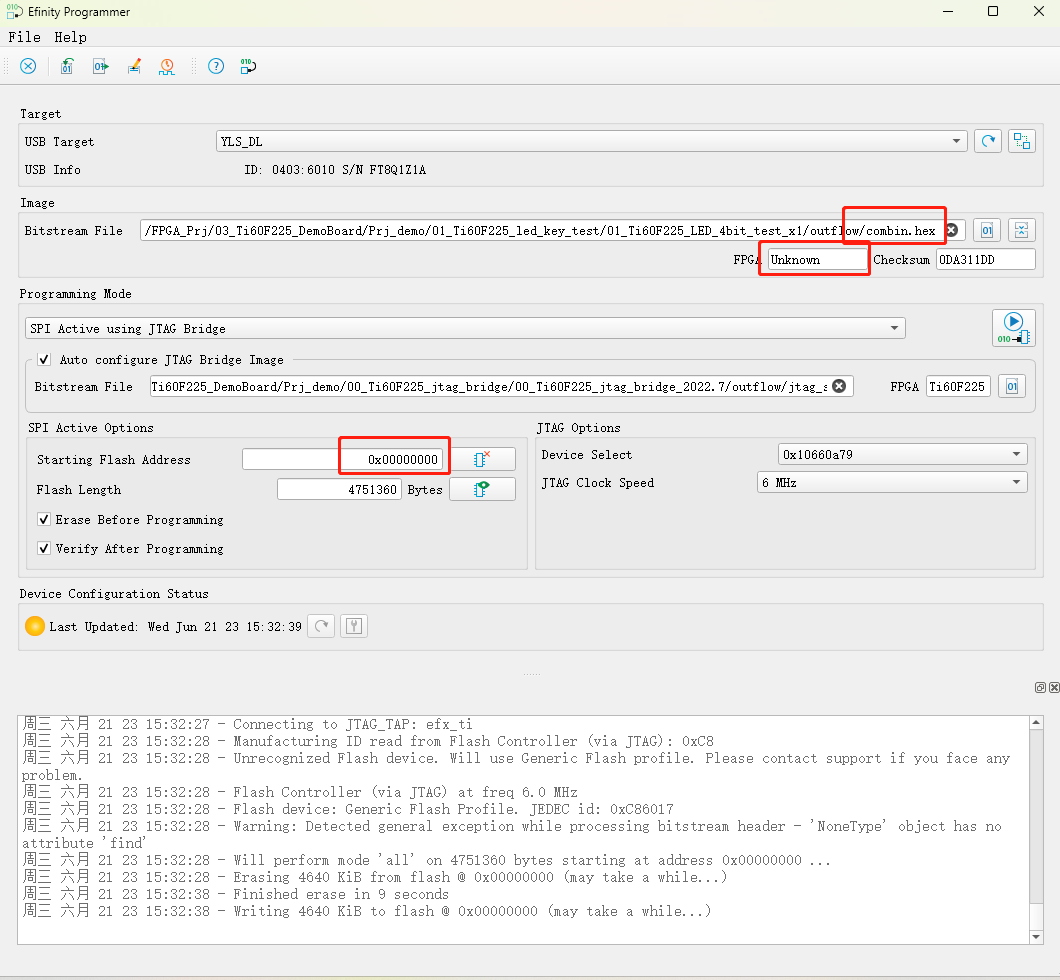

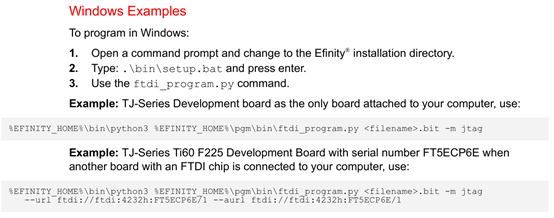

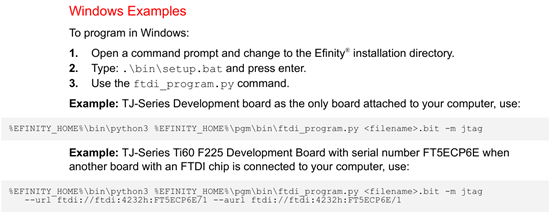

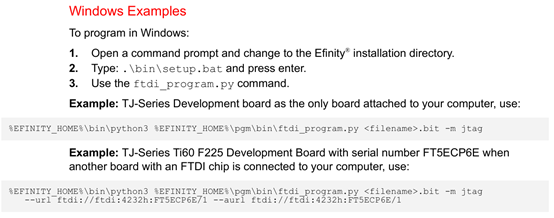

一、通过命令行烧写 参考文档Efinity Programmer User Guide部分,内容如下....

易灵思的PCIe的demo目前已经可以给客户去演示。暂时先把操作的注意事项记录下。 Ubuntu版本....

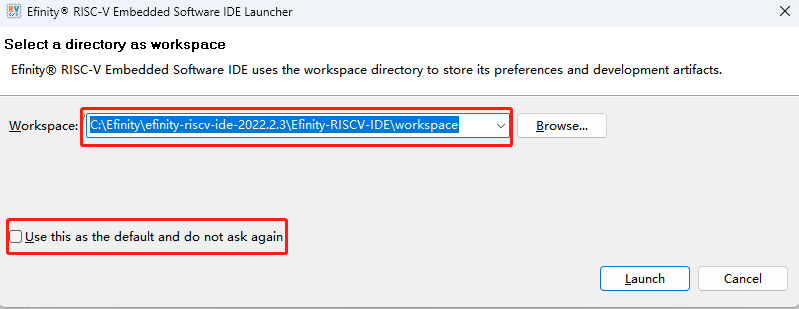

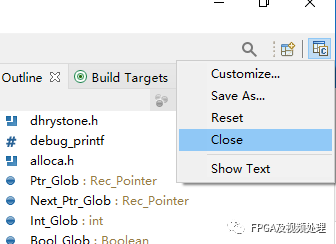

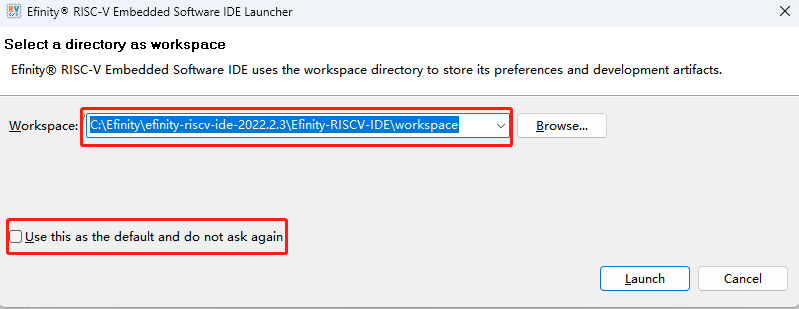

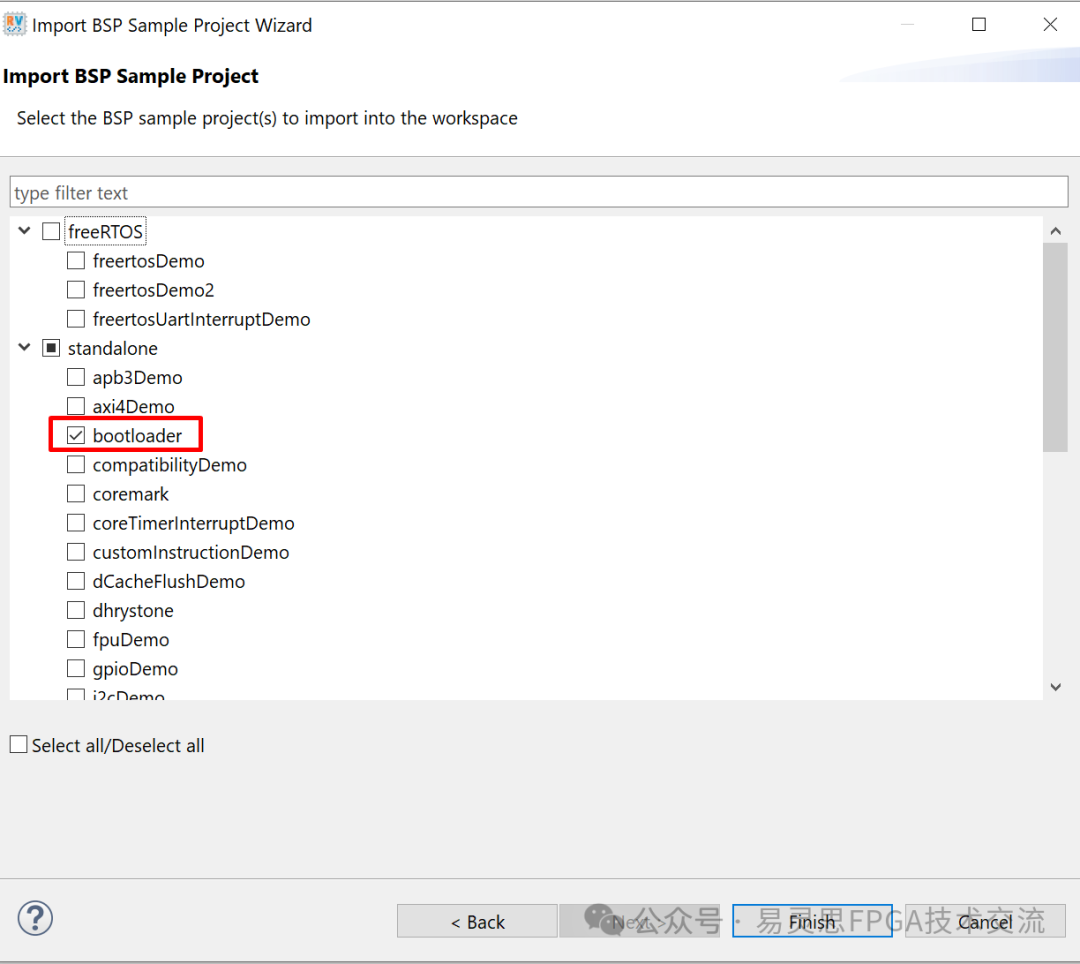

(1)如果工程直接复制另一个工程,路径一定要修改,建议重新eclipse工程。 (2)clean P....

一、通过命令行烧写 参考文档Efinity Programmer User Guide部分,内容如下....

一、通过命令行烧写 参考文档Efinity Programmer User Guide部分,内容如下....

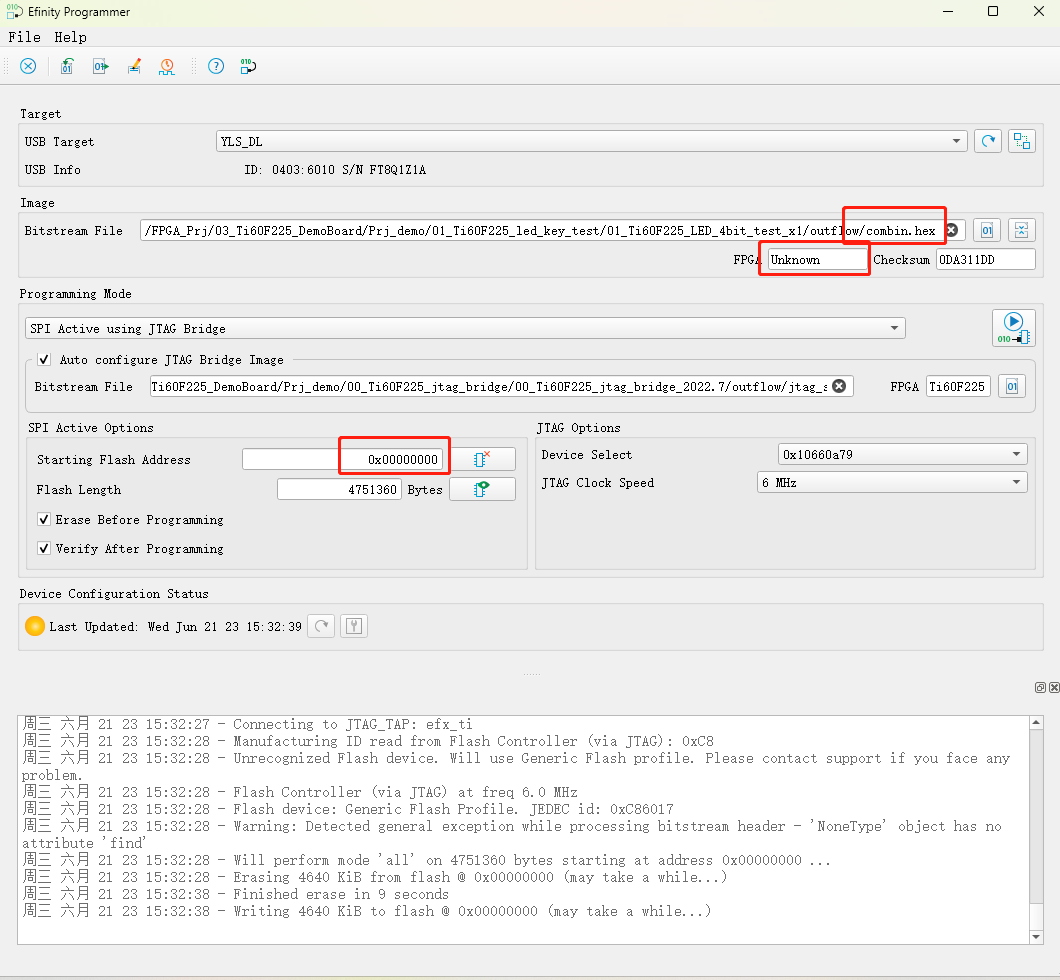

把烧写文件和json文件提供给他人进行调试 该方法是在不需要要提供源文件的情况下可以提供给别进行....

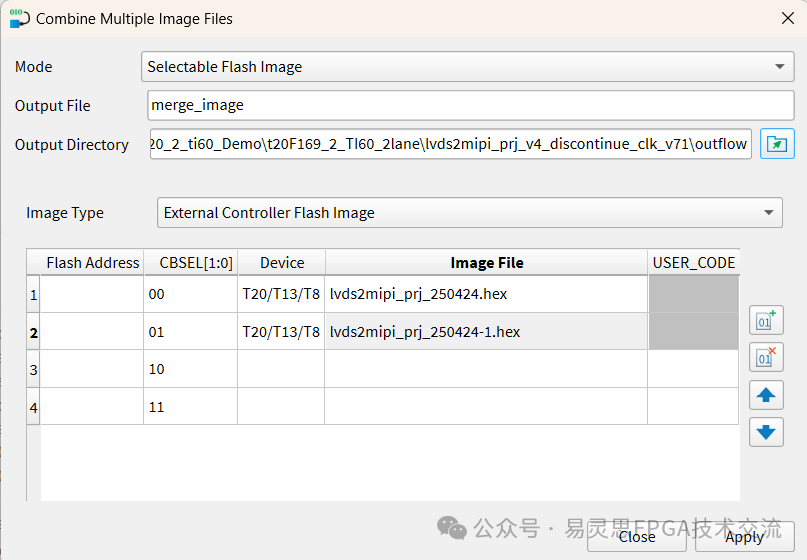

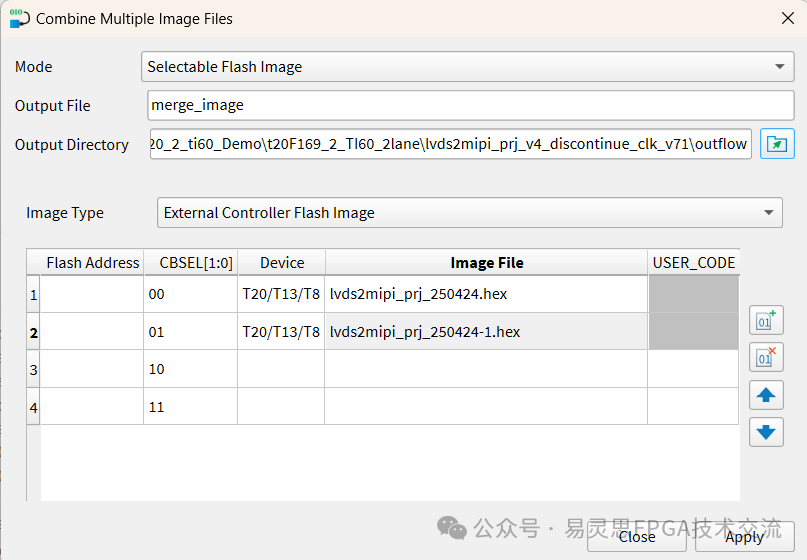

外部更新 外部更新通过CBSEL来选择,选择External Controller Flash Im....

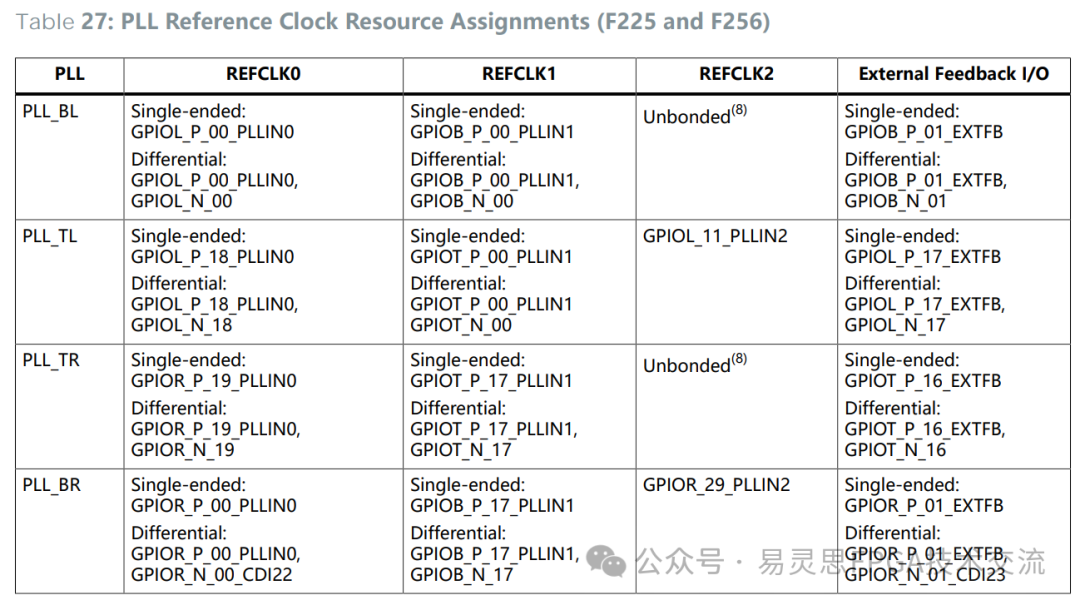

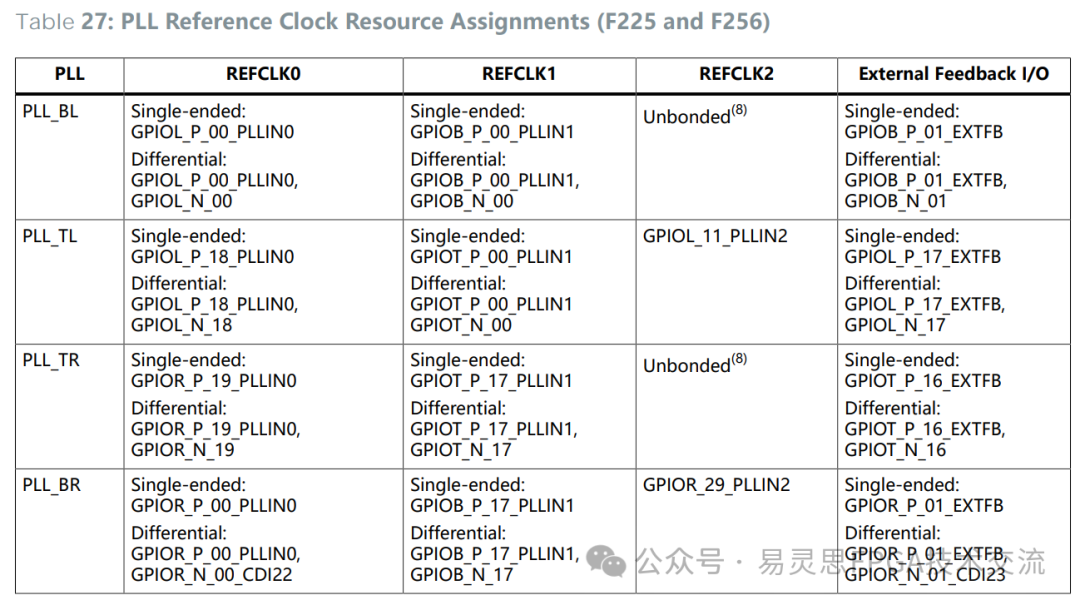

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对....

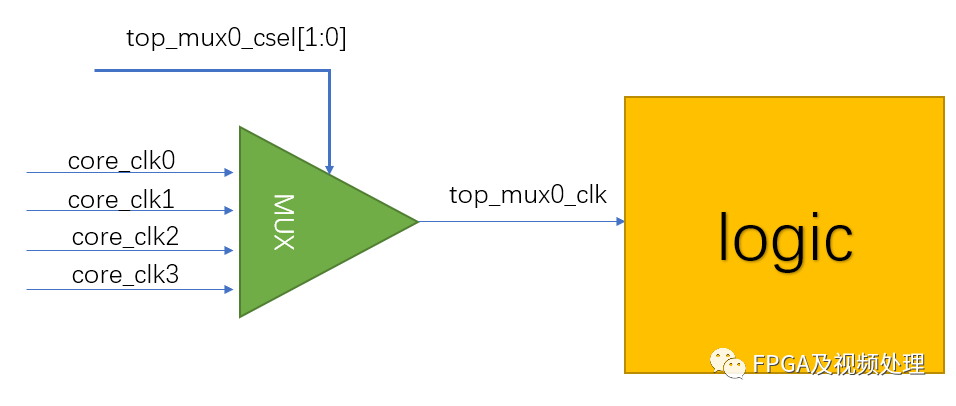

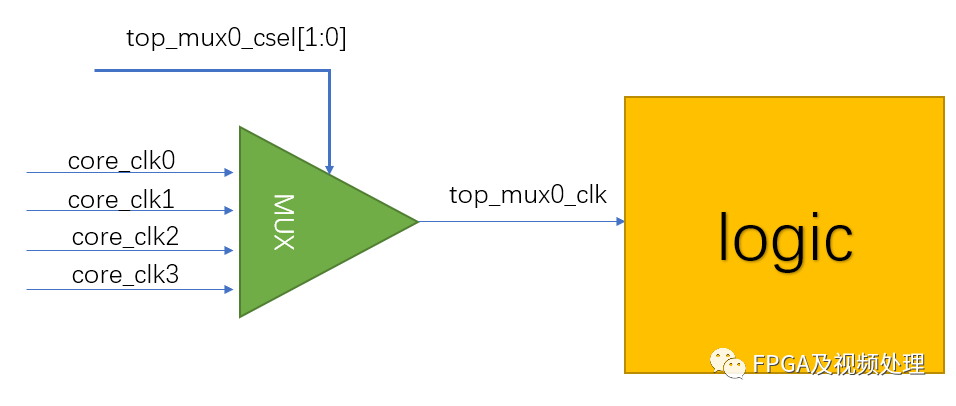

在trion要实现一个4选1时钟复用或许比较麻烦。但是在钛鑫上已经给出了解决方案。这里以Ti60F2....

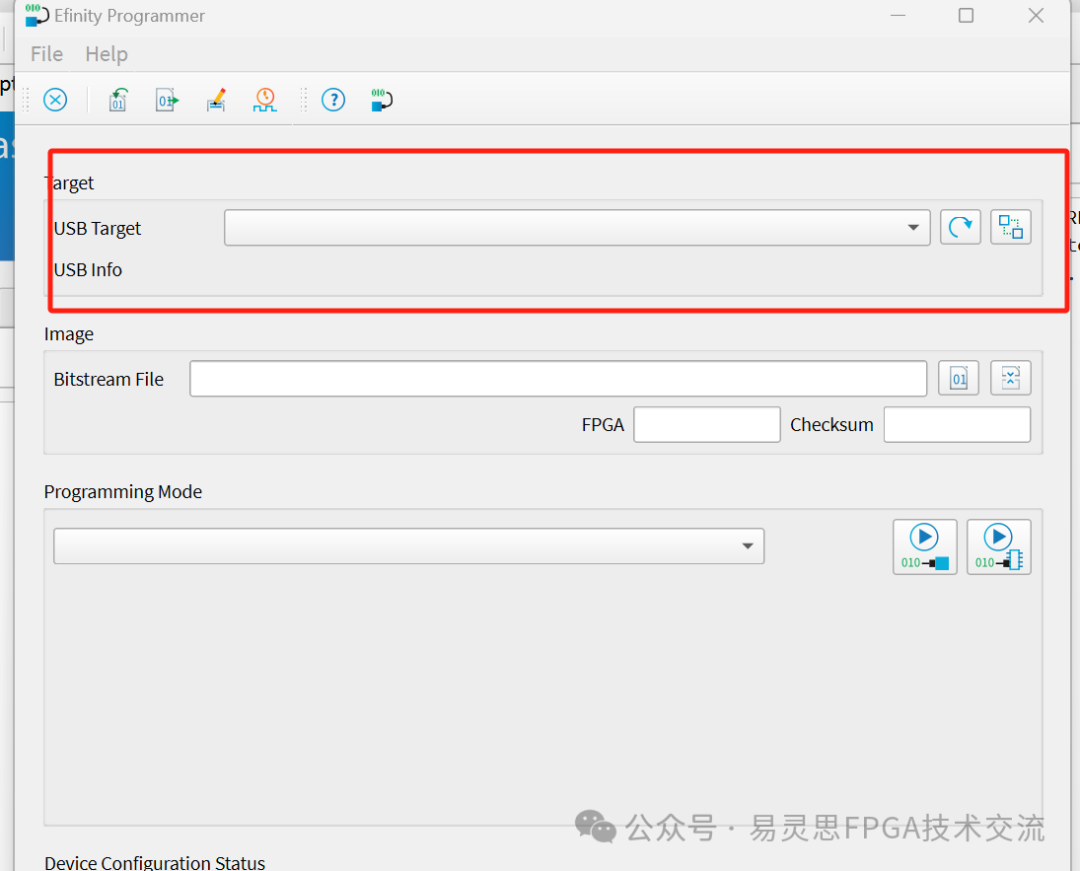

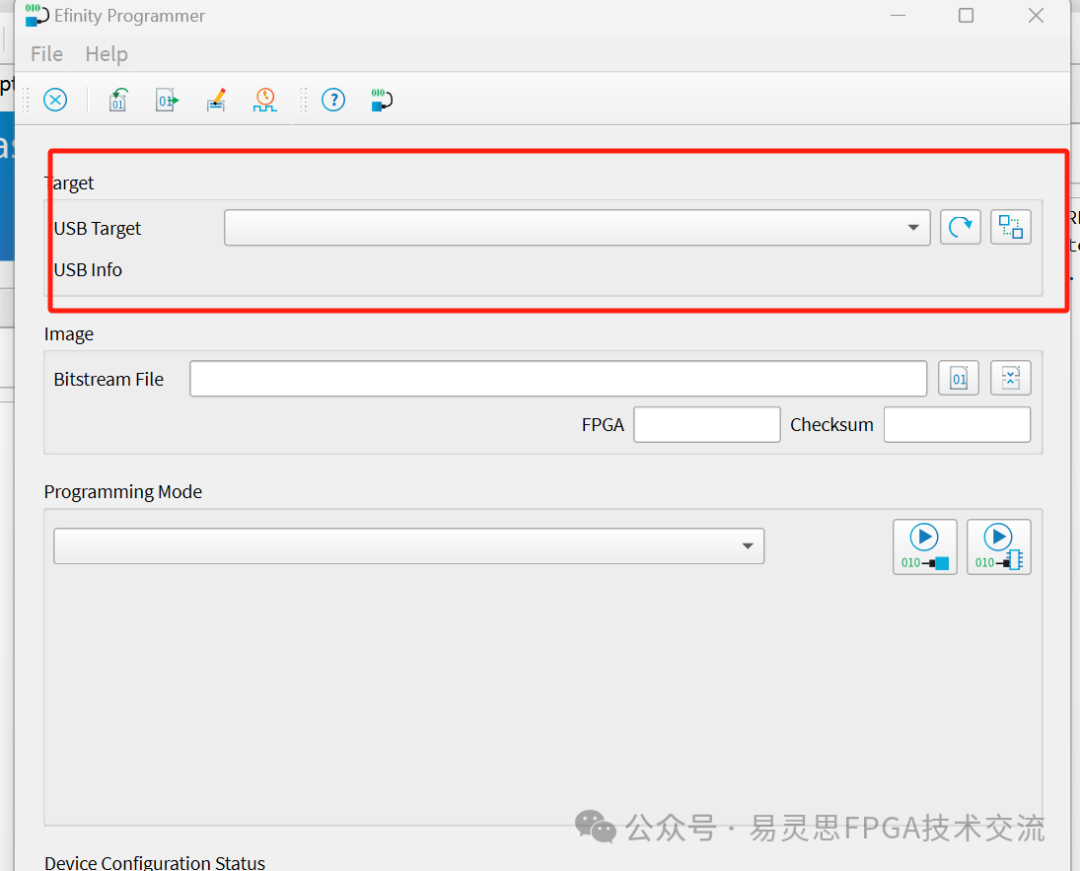

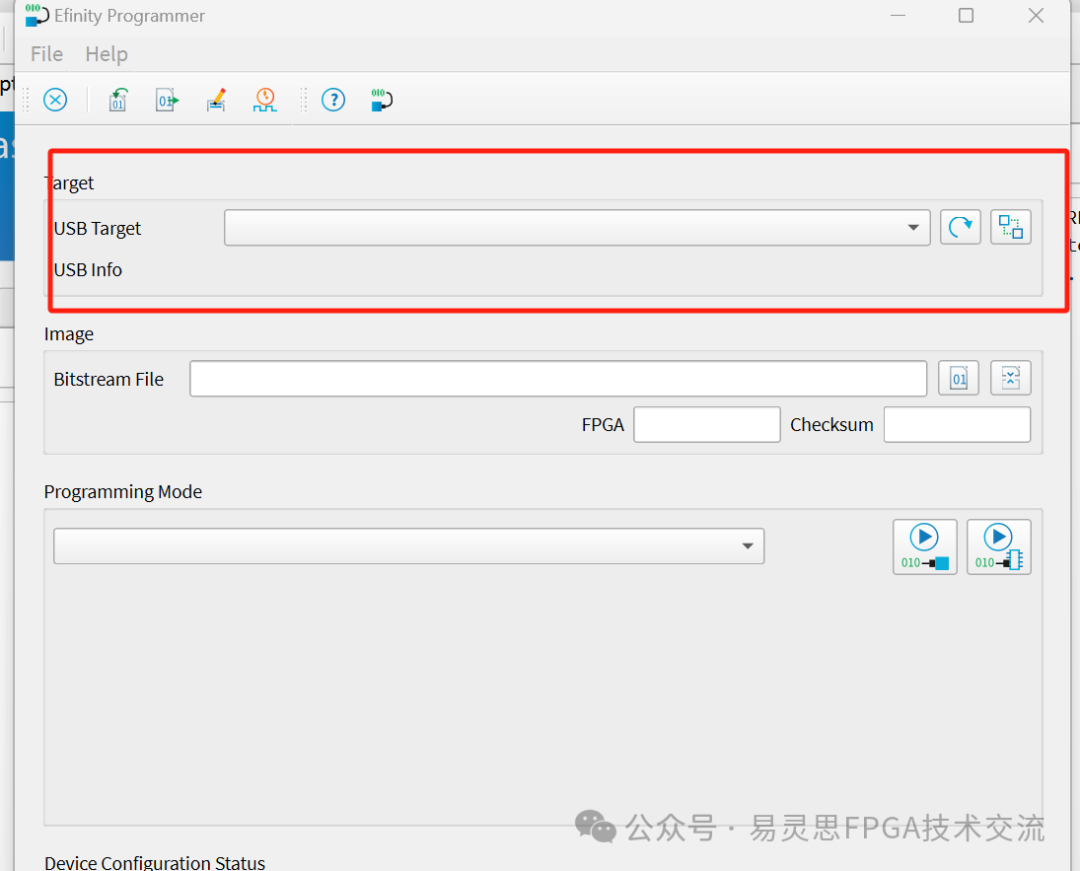

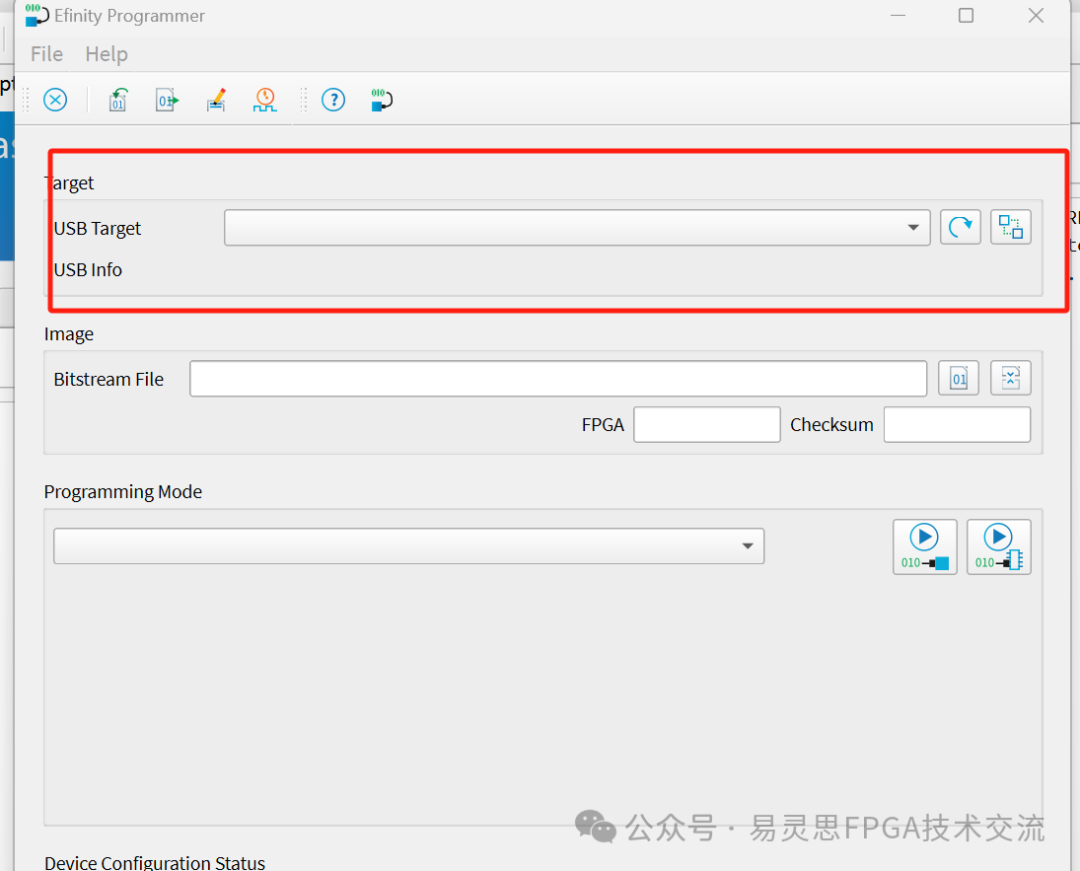

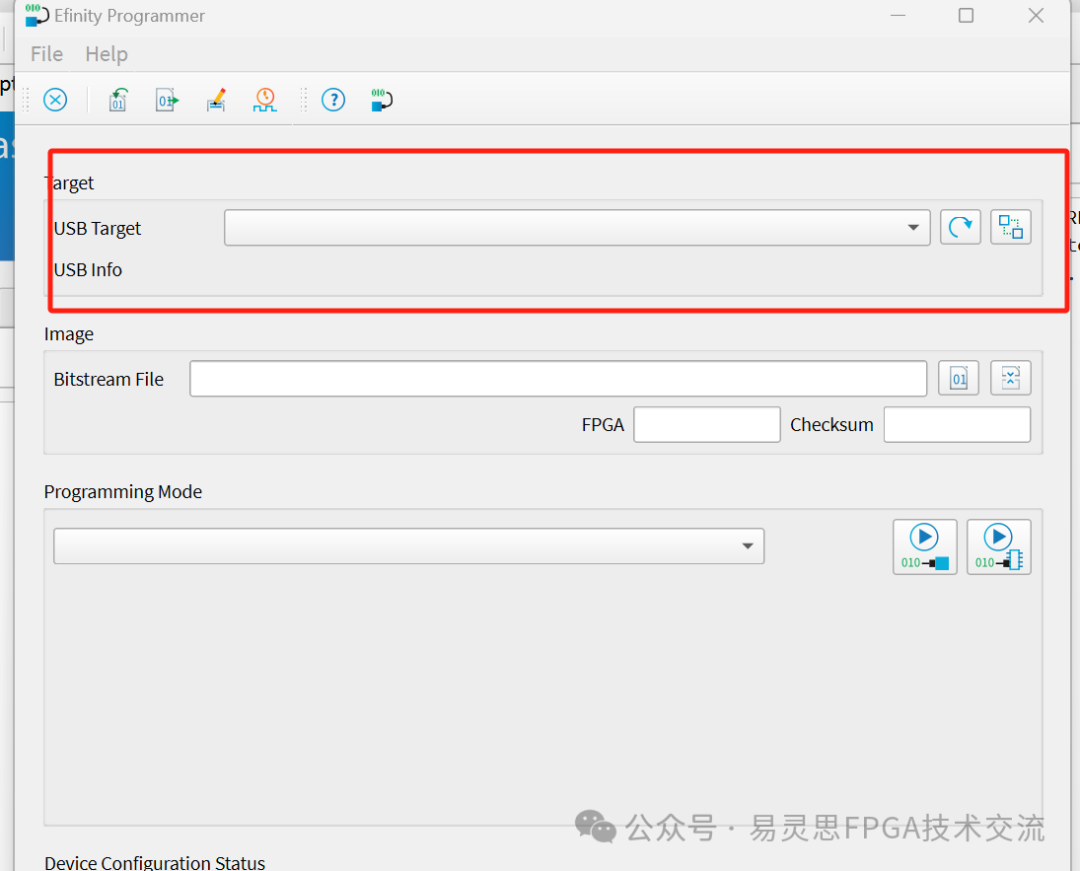

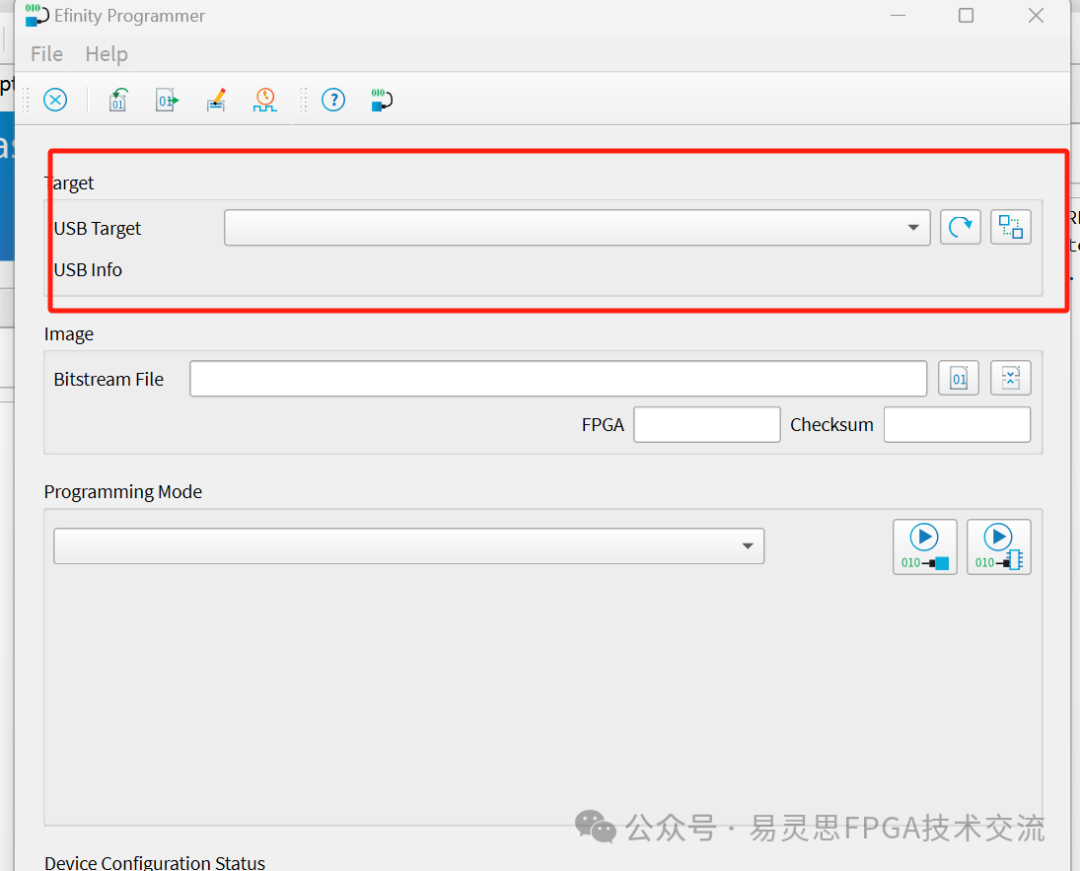

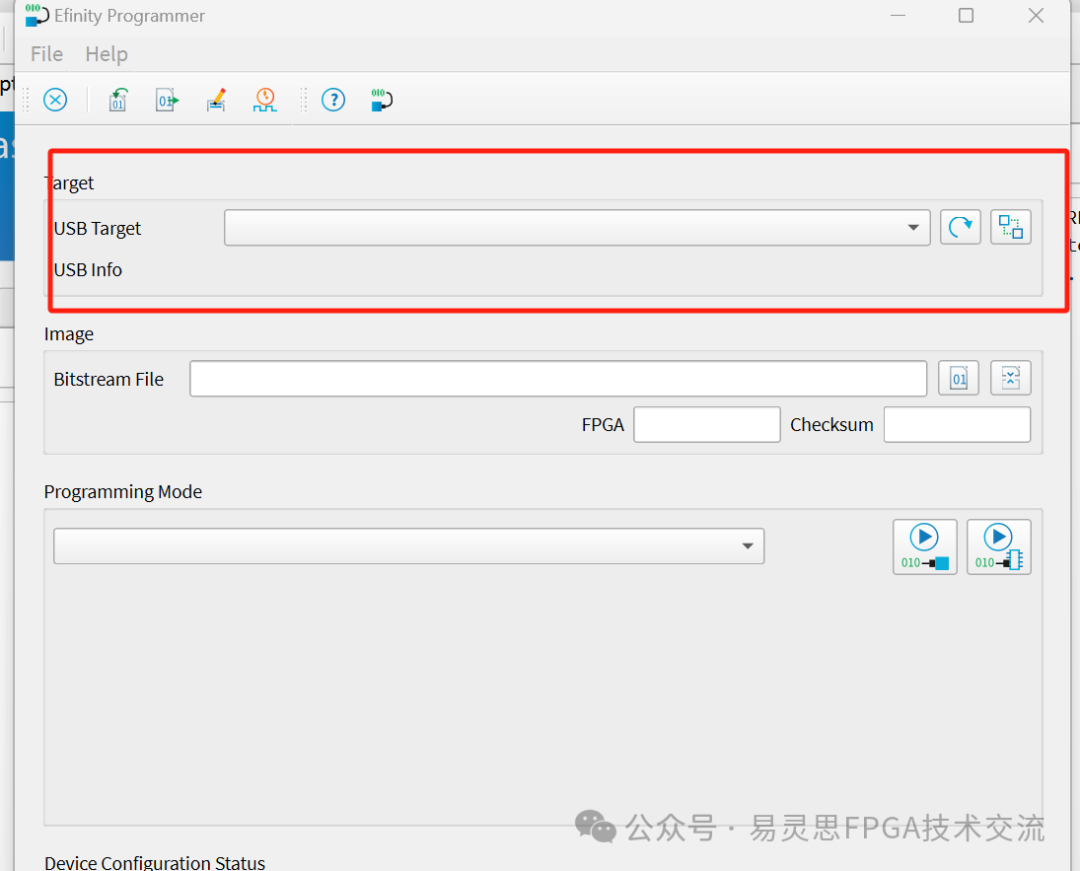

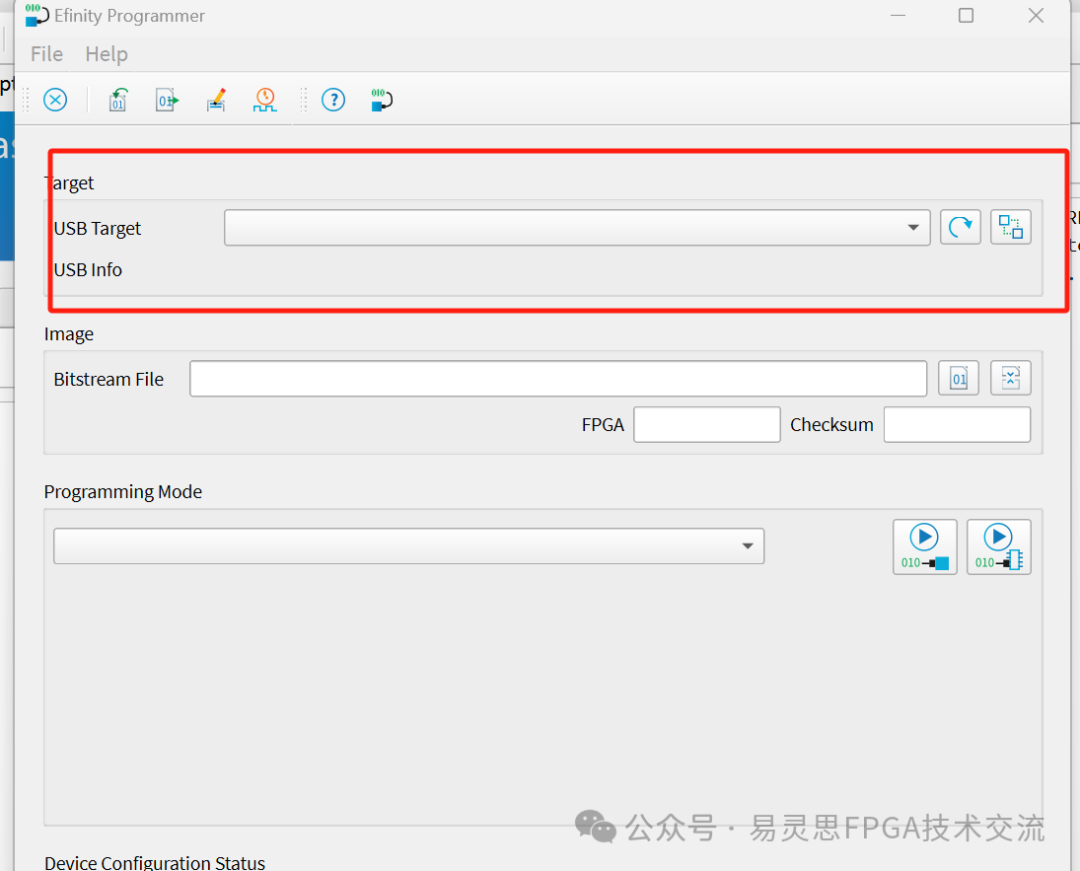

(0)连接下载器之后什么也读不出来 说明 :一般为驱动没有安装,在device manger里面....

(0)连接下载器之后什么也读不出来 说明 :一般为驱动没有安装,在device manger里面....

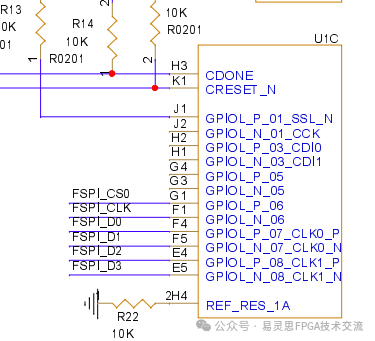

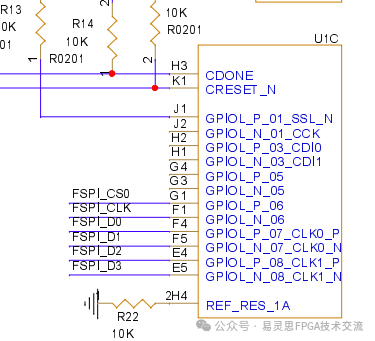

Ti60F100片上Flash为16Mb,容量相对较小,对于很多应用需要外扩flash,而且很多....

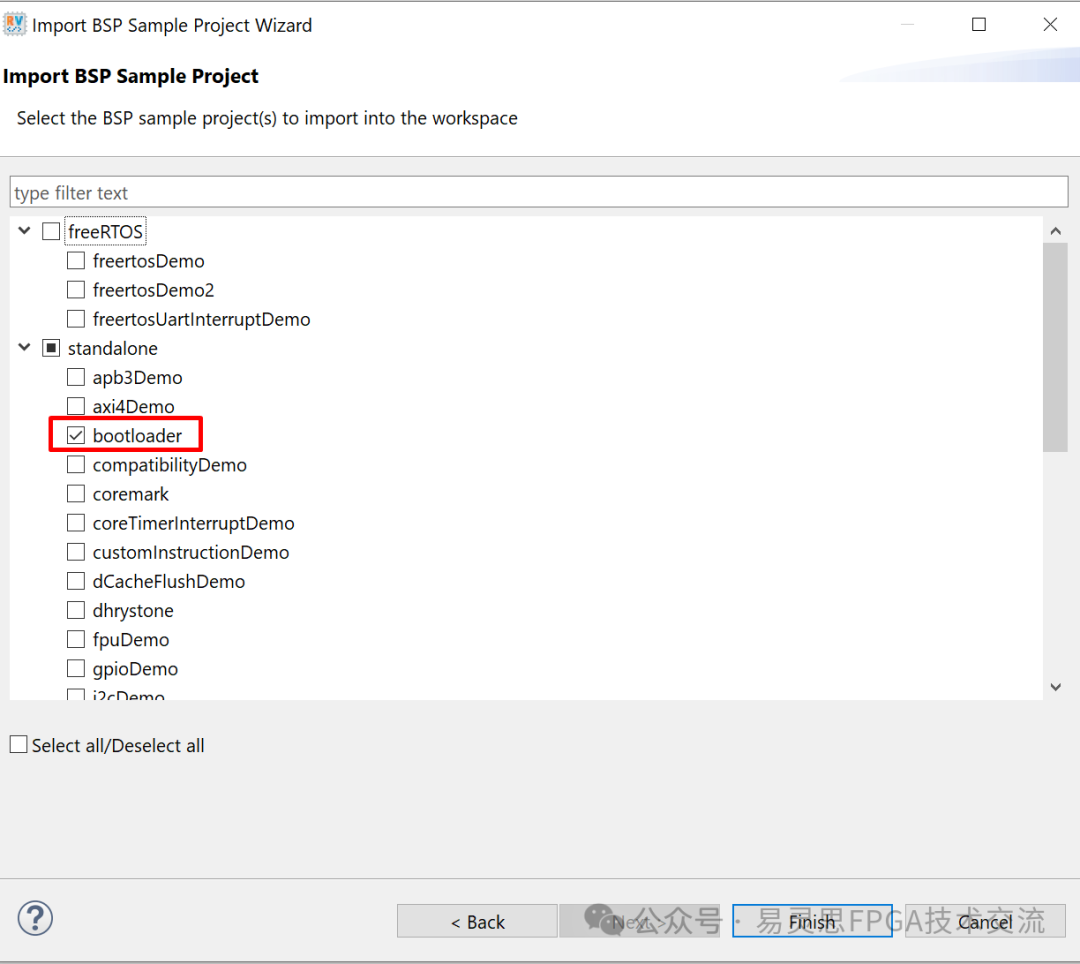

在生成SoC时,会生成一个预定义bootloader .bin文件,用于指定soc的工程运行的地址,....

该下载器把SPI与JTAG管脚进行了分开处理。鉴于JTAG使用较多,SPI使用较少,所以把JTAG放....

(0)连接下载器之后什么也读不出来 说明 :一般为驱动没有安装,在device manger里面查看....

易灵思的PCIe的demo目前已经可以给客户去演示。暂时先把操作的注意事项记录下。 Ubuntu版本....

简介 TI60F100-DK是一款采用易灵思Ti60F100开发的评估板。 采用底板和核心板....

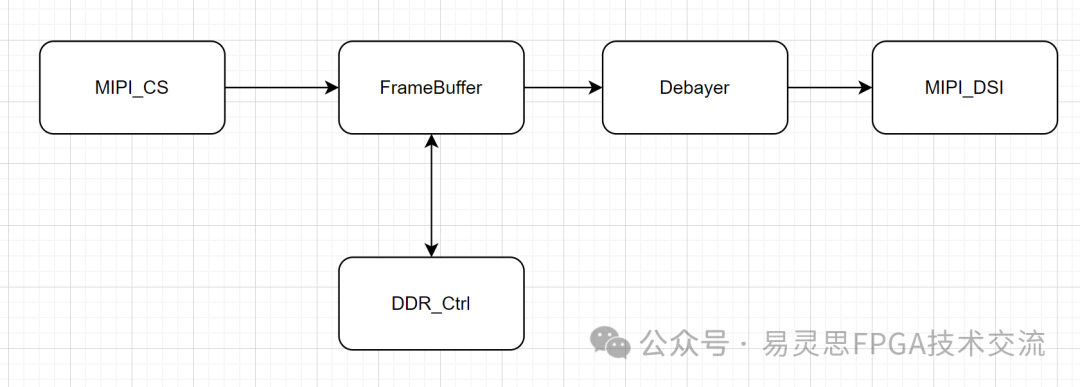

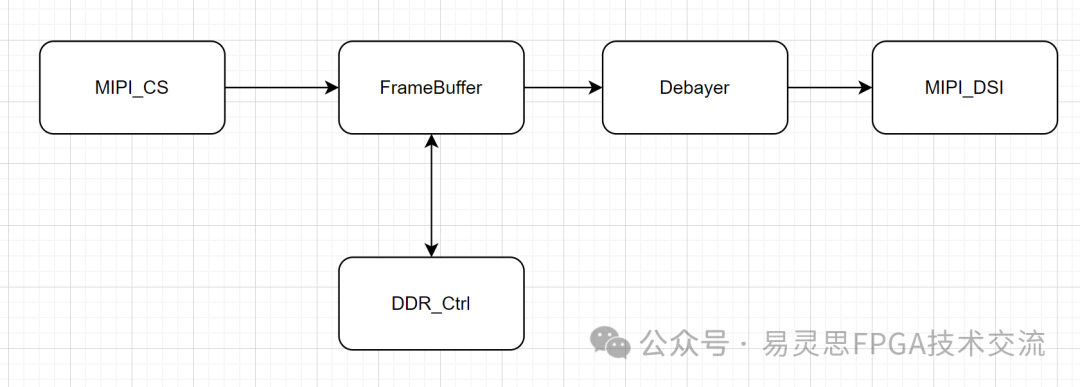

最近陆续有客户在评估易灵思的Ti180。Ti180的MIPI 2.5G是硬核。今天做一个简单的移植来....

(0)连接下载器之后什么也读不出来 说明 :一般为驱动没有安装,在device manger里面查看....

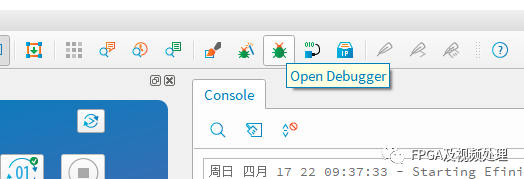

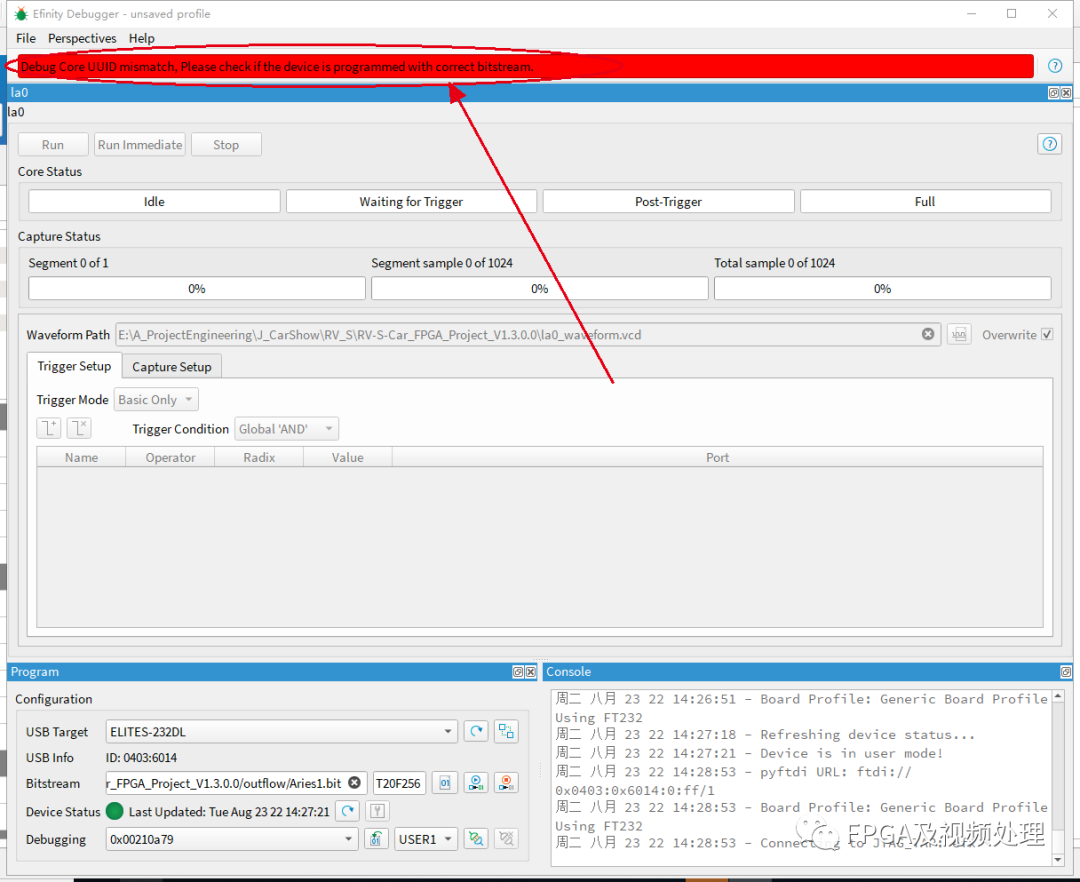

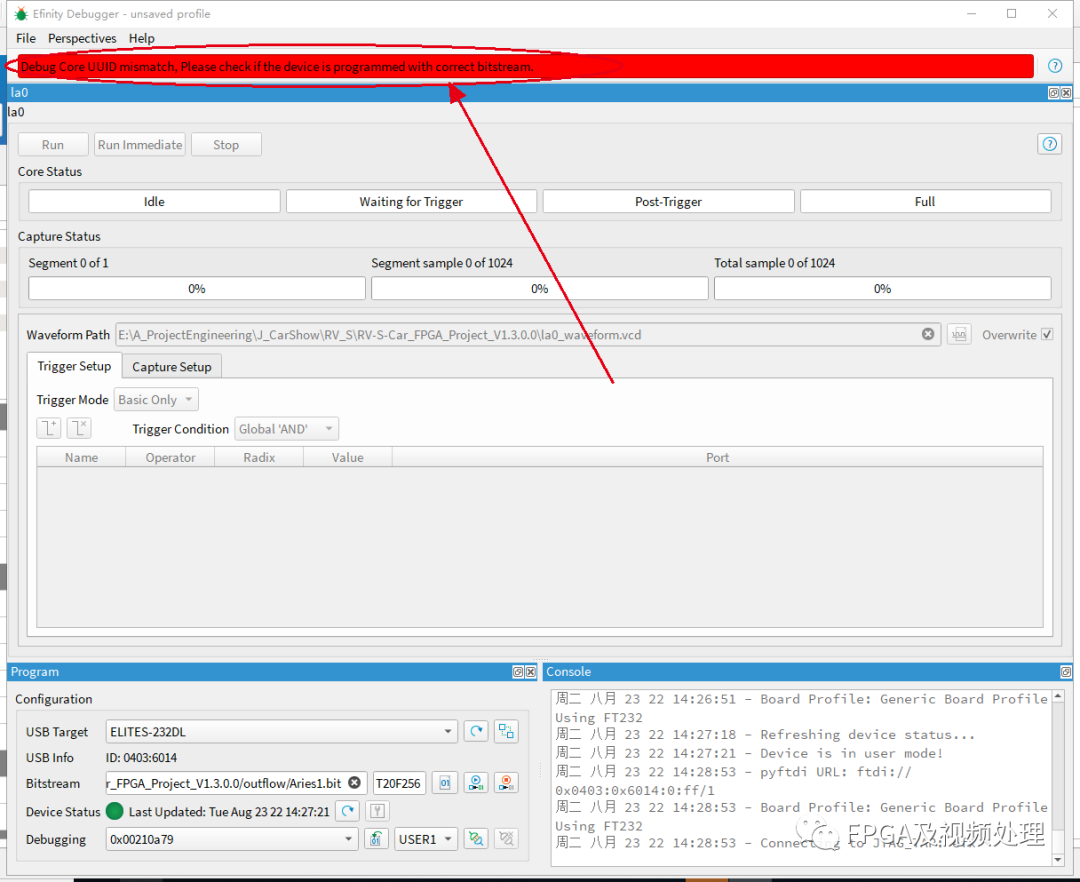

(1)UUID mismatch Efinity在Debug时会出现UUID mismatch错....

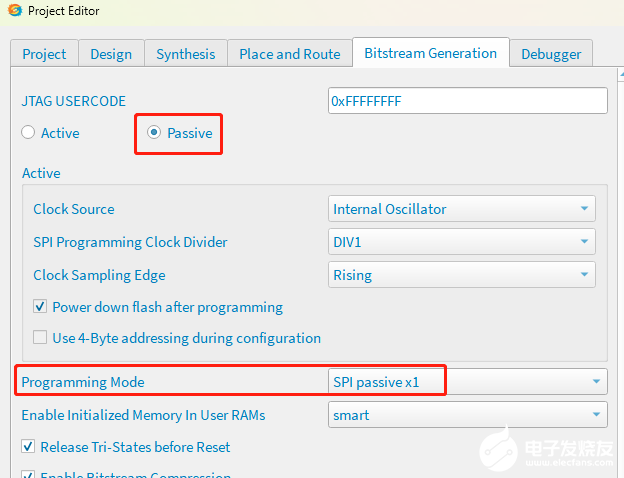

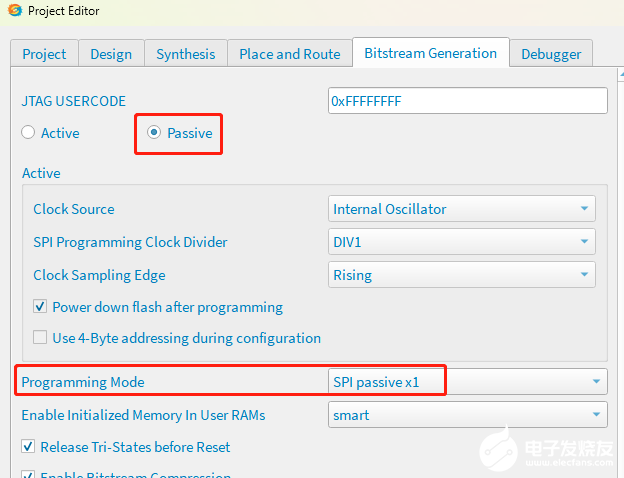

准备工作 PS模式首先要把Bitstream Generation中的 (1)JTAG模式选择为Pa....

这里以钛金的LVDS为例。 LVDS RX 时钟选择 LVDS时钟的接收要连接名字为GPIOx_P_....

今天有客户提出怎样把用户数据写入到flash的操作,本来以为写的programmer都不支持了,但是....

(1)如果工程直接复制另一个工程,路径一定要修改,建议重新eclipse工程。 (2)clean P....

1、 软件预设置2、新建工程3、添加源文件4、添加管脚约束5、添加GPIO6、PLL设置7、添加debug8、

一、 软件预设置二、新建工程三、添加源文件四、添加管脚约束五、添加GPIO六、PLL设置七、IPM添加IP八、

1、 软件预设置2、新建工程3、添加源文件4、添加管脚约束5、添加GPIO6、PLL设置7、添加debug8、

接口处理top接口output system_i2c_0_io_sda_writeEnable,ou

RISC V的I2C操作

RISC V的I2C操作