硬件平台 软件平台: 使用注意事项 MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的ex....

应客户要求做一个mult image的测试。 硬件平台: 软件版本 Golden image工程的设....

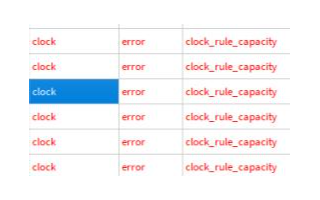

在T20中有16个全局时钟网络GCLK。在芯片的左右两侧各8个。全局时钟管脚或者PLL的输出时钟通过....

这里以钛金的LVDS为例。 LVDS RX 时钟选择 LVDS时钟的接收要连接名字为GPIOx_P_....

1.软件安装教程 step1: 安装Python,注意勾选“Add Python 3.7 to PA....

(1)UUID mismatch Efinity在Debug时会出现UUID mismatch错误。....

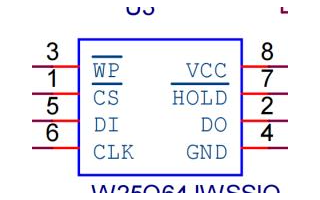

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了....

中断操作三个步骤:

1、中断初始化

2、trap处理

3、用户中断处理

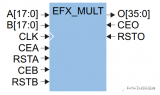

在使用Trion乘法器可能会遇到以下问题: (1)[EFX-0652 ERROR] 'EFX_M....

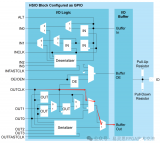

DDIO用法 对于输入输出IO很多时候会用到DDIO的用法。对于DDIO,就是时钟的双沿采集或者....

时钟输出 易灵思所有的GPIO都可以用作时钟输出。这里我们提供两种时钟输出方式。 方法一:把时钟设置....

在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。 在outflow下....

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx....

如果要分配的IO比较多,也可以通过TCL来添加 IO分配。在interface界面通过Export ....

今天有同事反馈出这样一个在使用RISCV 调试时的问题: Error: no device foun....

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径....

(1)打开Programmer异常 原因:(1)更换USB接口 。 (2)USB有限制,需要联系客户....

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xil....

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径....

今天有同事反馈出这样一个在使用RISCV 调试时的问题: Error: no device foun....

正在使得该elf文件,上次的JTAG链接没有断开。此时可以先关闭c/c++工作界面,再重新添加C/C....

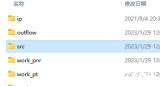

因为目前软件的限制,RISCV的逻辑不能同时共用JTAG,所以如果想要同时去调试逻辑和RISCV的话....

迄今为止,大家都在吐槽gtkwave debug每次弹窗都会覆盖上一次弹窗设置好的排序和参数。下面我....

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要....

DDR应用案例

(1)ERROR:Interface Designer constraint generatio....

感谢朋友提供的视频。 1.软件安装 step1: 安装Python,注意勾选“Add Python ....

通过get_port命令查看接口。 get_ports * 以LVDS的输入输出为例 怎样去查看ou....

因为目前软件的限制,RISCV的逻辑不能同时共用JTAG,所以如果想要同时去调试逻辑和RISCV的话....