| 选项 | 说明 |

| Usereditor | 一般软件自带的编辑器功能有限,而外部编辑器功能要强大很多。所以建议大家使用外部编辑器。在User editor中输入编辑器的路径。 |

| Use user editor as default editor for all files。 | 如果希望每次点击文件时是通过外部编辑器打开的,可以勾选Use user editor as default editor for all files。反之,如果希望使用自带编辑器打开则不用勾选。 |

| Top level project path | 指定新建工程目录。 |

| Enable flow data integrity check | |

| Open last project on startup | 如果勾选此选择,会打开上次关闭的工程 |

| openfile usingdefault system application | |

| Use lastwindow layoutsetting | 使用上次软件关闭时的窗口布局。 |

| Auto-correct Tcl command | 在tcl命令窗口中输入命令时可以自动修改存在的错误。 |

| Auto-loadPlace andRoute data | 打开软件是自动加载布局布线的数据。建议关闭。 |

| Migrate interfacedesign withdevicechange | 修改器件时,interface desiger中的配置也要修改。 |

| EnableIP upgrades prompt on project load | 用新版本打开老的软件建的工程时,打开该选项会提示IP需要更新,如果不想更新IP可以关闭这个选项。 |

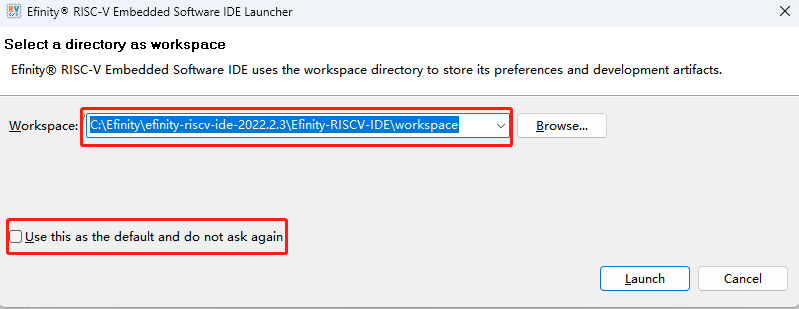

二、新建工程

Step1:点击设置

Step2:在Top level project path中输入路径

Step3:点击File -> Open Project,路径会指向step2中设置的路径

注意:易灵思的工程名为

把retiming和seq_opt设置为0

点击ok,新建工程完成。

三、添加源文件

四、管脚约束

这里我们以一个LED点灯为例,代码如下:

Efinty是通过interface designer工具来设置IO等和外设相关的接口及电气属性的。Interface designer操作界面的打开通过下面的Open Interface Desinger来实现。

Core 与interface的关系

Eifinty采用的把逻辑资源和硬核资源分开的架构,代码部分只针对逻辑资源,也就是我们这里提到的Core,而IO及其他硬核部分的配置在interface Designer工具中。下图是interface与Core的关系,它们之间通过被称作Siganl Interface的连线资源实现互联。

因为习惯问题,使用者在最初一定会存在一些问题,但是习惯之后它也是有不少优势存在的。比如说,在前期的硬件设计中,只需要在Interface Designer中添加已添加的IO及其他需要的硬件接口,并通过一键检测就可以很清楚的知道与外设的连接是否合理,不需要考虑内部因为没有完整的程序而可能被优化的风险。另外有些interface的选项在修改之后可以不需要先编译而直接生成数据流。

interface与core的关系

interface界面

告诉软件FPGA目前的bank电压,硬件电路的bank电压要和interface中的一致,如果电压设置不一致可能存在长时间运行致使芯片失效。设置位置在Device Setting -->I/O Banks

Step1:右键选择GPIO

Step2:根据选择的是单线还是多线来选择Create Block还是Create Bus

Step3:编辑IO属性,IO属性如下:

选项 | 选择 | 说明 |

Mode | Input, | Input:把FPGA管脚设置为输入; Output:把FPGA管脚设置为输出; Inout:把FPGA管脚设置为双向管脚; Clkout:把FPGA管脚设置为时钟输出 |

Connection Type | Normal,gclk,pll_clkin,VREF | gclk走全局时钟网线,可以驱动PLL也可以直接驱动内部逻辑 用于普通的GPIO; PLL_CLKIN表示这个IO是用于驱动PLL的; 用于存储器的参考管脚 |

Register Option | None,register | 是否添加IO寄存器,推荐添加。 |

I/O Standard | 3.3v,1.8v,1.2V,1.5v | 设置IO的电平 |

Double Data I/O Option | None,normal,resync | 是否设置IO为双延采样 |

Clock | 当打开IO寄存器时需要添加指定寄存器的时钟 | |

Drive Strength | 1,2,3,4 | 设置输出IO的驱动能力 |

Enable Slew Rate | Yes,no | 是否命名能slew rate |

检测Interface设计是否存在问题。

保存设置,点击Check Design,检查interface是否存在问题。

再点Generate Efinity Constraint Files,我们就可以在Result --> interface下面看到生成一些文件。通过xxx_template.v复制例化接口

| Instance Name | 用户定义 | |

| PLLResourec | ||

| Output ClockInversion | on,off | 翻转时钟输出 |

| ConnectionType | gclk, rclk | 时钟类型 |

| Clock Source | External, Dynamic,Core | External指时钟通过IO驱动;Dynamic:支持多路时钟选择;Core:时钟通参考通过core供给 |

Automated clock Calculation | 打开时钟计算和设置窗口 |

八 添加约束

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录),对于gclk时钟需要手动添加约束的时钟周期,对于PLL生成的时钟已经约束完整。

编译完成之后可以查看时序报告,也可以通过routing àxx.timing.rpt来查看路径详细延时信息,如果想查看更可以通过指令来打印或者通过print_critical_path来控制打印的路径数量 。

编译

点击dashboard中Toggle Automated Flow来设置是单步还是全程编译(暗色是单步),下面是综合,布局,布线,生成数据流,stop的相应按键。软件左下角会的编译进行提示编译进程。

八添加debug

8.1通过向导添加debug

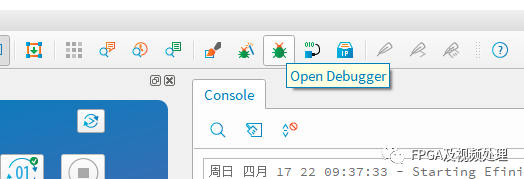

点击Open Debugger Wizard

(1)设置Buffer Depth

(2)Input Pipeline Stage

(3)Capture control

(4)JTAG USER TAP

(5)修改时钟域

(6)Probe Type

8.2手动debug

手动debug的方式就是自己一个个添加debug的信号 ,当然这种方式也可以添加 VIO,VIO可以通过JTAG产生一些控制信号。手动添加debug的方式如下。

step1:点击OpenDebugger打开Efinity Debugger页面,在Perpectives下面选择Profile Editor.

Step2:根据需要选择添加VIO或者LA.

Step3: 以添加LA为例,点击右侧的add_probe来添加需要的信号,然后在Name中修改信号名字,Width中指定信号位宽及Probe Trigger or Data中设置信号的触发属性。如果要删除信号就点击右侧的带“X"的remove Probe.

另外可以指定Data Depth,也就是数据采样深度,Input Pipeline Stage对可以数据打拍,用于优化时序。

step4 添加VIO。根据需要选择vio界面的add source和add probe 来添加自己需要的信号。如果要删除信号则选择remove source/probe.

step5:点击Generate,会在工程目录下就会生成一个debug_top.v,把该文件添加到工程并例化。效果如下。

step6.添加JTAG。打开interface Designer,右击选择JTAG User Tap,添加JTAG Block,并指定JTAG resource,如下图中选择JTAG user1.然后生成约束例化信号。

注意通过向导添加Debugger和通过手动添加debuger这两种方式不能共存。另外要注意在interface Designer中添加了User Tap之后,在添加向导时要选择不同的User Tap号,否则会提示接口有占用。如下图指示“ERROR: jtage resource = JTAG USER1 has been occupied"。

8.3 在线调试

该步骤需要在配置FPGA之后再能操作。

触发条件的设置

捕获设置:

•触发位置

•分段数量

•窗口尝试

| 主动模式(SPI Active)— AS模式 | 通过SPI专用插座在线烧写FLASH,FLASH离线烧写好了再焊接,FPGA自己主动通过从非易失性的SPI FLASH读取bit流进行加载,支持X1 X2 X4,x8(不同的FPGA支持的位宽有区别) |

| 被动模式(SPI Passive)— PS模式 | |

| JTAG模式 | 上位机通过JTAG口将bit流文件发送到FPGA,对FPGA进行加载 |

| SPI Active using JTAG bridge — Bridge模式 | 通过FPGA的JTAG口烧写和FPGA连接的SPI FLASH |

十 仿真

易灵思为所有IP提供了仿真模型

以FIFO为例,在工具栏中选择IP Catalog

另外 关于interfce Designer接口的仿真模型在路径C:\Efinity\2023.1\pt\sim_models\Verilog下。

原文标题:Efinity入门使用-v4

文章出处:【微信公众号:易灵思FPGA技术交流】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1664文章

22504浏览量

639347

发布评论请先 登录

华为昇腾超节点系列产品全面支持DeepSeek V4模型

软通华方超节点服务器产品全面适配DeepSeek V4模型

燧原科技L600 FP8原生适配DeepSeek-V4-Pro/Flash模型

国产AI换芯提速!DeepSeek V4和小米MiMo-2.5上线,主流国产芯片适配

国产AI算力:从DeepSeek V4与华为昇腾协同看全栈自主之路

长江计算G940K V2超节点服务器完成对DeepSeek V4模型极速适配

海光信息DCU平台完成对DeepSeek V4模型极速适配

昆仑万维天工AI大模型SkyReels V4登上Artificial Analysis榜单全球第一

PROFET™ +2 12V 演示板快速入门指南

Efinity RISC-V IDE入门使用-5

programmer下载常见问题总结-v14

programmer下载常见问题总结-v11

programmer下载常见问题总结-v13

Efinity debuger常见问题总结-v4

Efinity入门使用-v4

Efinity入门使用-v4

评论