(1)如果工程直接复制另一个工程,路径一定要修改,建议重新eclipse工程。

(2)clean Project时提示rm: can't remove 'build/dhrystone.elf': Permission denied

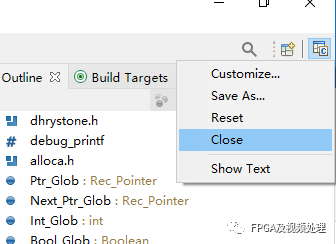

正在使得该elf文件,上次的JTAG链接没有断开。此时可以先关闭c/c++工作界面,再重新添加C/C++(default),然后在Console中关闭上次的链接。

(3)Debug session'default' already started。

先关闭c/c++工作界面,再重新添加C/C++(default),然后在Console中关闭上次的链接。

(3)Memory region Used Size Region Size %age Used

c:/efinity/sdk_windows/riscv-xpack-toolchain_8.3.0-2.3_windows/bin/../lib/gcc/riscv-none-embed/8.3.0/../../../../riscv-none-embed/bin/ld.exe: build/ti60f225_oob.elf section `.bss' will not fit in region `ram'

ram: 2363296 B 1 MB 225.38%

c:/efinity/sdk_windows/riscv-xpack-toolchain_8.3.0-2.3_windows/bin/../lib/gcc/riscv-none-embed/8.3.0/../../../../riscv-none-embed/bin/ld.exe: region `ram' overflowed by 1314720 bytes

collect2.exe: error: ld returned 1 exit status

make: *** [../common/standalone.mk build/ti60f225_oob.elf] Error 1

解决办法:Error的意思是外部存储器的存储空间不够,目前在分配了1MB的情况下使用了225.38%。所以把default.ld中的LENGTH 修改成4M.

重新编译后的结果。

(4)Error: libusb_get_string_descriptor_ascii() failed with LIBUSB_ERROR_PIPE

Error: no device found

Error: unable to open ftdi device with vid 0403, pid 6014, description 'ELITES-232DL', serial '*' at bus location '*'

原因:把embedded_swsoc_xxbspefinixEfxSapphireSocopenocdftdi.cfg(ftdi_ti.cfg)修改成下载器读出来的名字,比如这里我把ELTES-232DL修改成了Trion T120F324 Development Board。因为Programmer界面读到的USB target就是Trion T120F324 Development Board,当然也要注意ftdi_vid_pid和ftdi_channel是否正确,如果不正确也会引起别的问题。

(5)Error:cpuConfigFileD:testriscvefx_ti60f225_oob_v2.1embedded_swsapphire_soccpu0.yaml not found

Error: target 'fpga_spinal.cpu0' init failed

原因:debuger路径问题。在riscv和efx之间应该有个斜杠,如报错中的红色标注。

(6)No source available for "main() at 0x1114"

原因:没有打开debug环境变量。打开debug开关之后要重新编译。

(7)Error: timed out while waiting for target halted

原因:1)IP设置的是soft Jtag,实际却用hard Jtag在调试;

2)CPU没有跑起来;

3)debuger与JTAG冲突;

4)在interface 添加JTAG之后生成的信号与RISCV 连接不正确或者不完全。

5)AXI接口连接异常,也可能出现timed out指示。

(8)SOC烧写到flash启动不了

一般默认片上RAM选择了4K大小用于bootloader,但是如果手动修改了bootloader,比如添加了debug,可能存储空间不足。

(9)

Error:JTAG scan chain interrogation failed :all ones

Error: CheckJTAGinterface,timings,target power, etc.

Error: Trying to use configured scan chain anyway...

Error: fpga_spinal.bridge: IR capture error:saw ox0f not 0x01

workround:JTAG下载线连接不紧。

(10)soft Jtag与hard Jtag同时使用时,会出现第一次debug都需要重新插拔下载器问题

workround:查找两个下载线的连接位置,注意分开两个下载器的连接位置。

(10)soc IP生成不了,

workround可能是java 8没有安装

(11) No source available for "(gdbi2),proc[42000j,threadGroupi1],gdb(2),proc420001.0Sthread[1).thread(1j.framel0j'

说明:外部存储器没有运行起来

(12)错误:

mkdir: can't create directory 'build/xxx/embedded_sw/sapphire_soc/software/standalone/uartInterruptDemo/': No such file or directory

make: *** [../common/standalone.mk build/xxx/embedded_sw/sapphire_soc/software/standalone/uartInterruptDemo/src/main.o] Error 1

"make all" terminated with exit code 2. Build might be incomplete.

WorkWround : Eclipse路径太长。

在common文件夹下,找到standalone.mk文件。

把路径:

OBJS := $(realpath $(OBJS))

修改成:

OBJS := $(addprefix $(PROJ_NAME)/,$(OBJS))

如下图所示(感谢客户为我们提供解决方案)

(13)Debug时出Break at address"0xf90000000" with no debug information avalibale,oroutside of program code

(14)

Info : JTAG tap: fpga_spinal.bridge tap/device found: 0x10660a79 (mfg: 0x53c (Efinix Inc), part: 0x0660, ver: 0x1)

Error: fpga_spinal.bridge: IR capture error; saw 0x05 not 0x01

Warn : Bypassing JTAG setup events due to errors

Error: !!!

Error: Can't communicate with the CPU

Error: !!!

Warn : target fpga_spinal.cpu0 examination failed

Info : starting gdb server for fpga_spinal.cpu0 on 3333

Info : Listening on port 3333 for gdb connections

Warn : Target was in unknown state when halt was requested

Info : Halt timed out, wake up GDB.

Error: timed out while waiting for target halted

原因(1)RISCV中FPGA Top Port选择不对。

(2)确认下载线连接是否正常。

(13)

(1) 同一个下载器时softjtag与hardjtag的名字不能一样,比如一个是YLS_DL,另一个是YLS_DL1.也就是需要手动把另一个名字修改下。

(2)注意修改cfg文件时文件时的channel号要与下载器对应

(14)

(1)用2022的版本打开 2023版本的工程报这个错误 ,新版本已经不再使用c232hm_ddhsl.cfg文件,而是改用external.cfg文件 。

(15)[BUILDER_INVOKE_BUILD_COMMAND]stderr找不到或无法加载主类saxon.board.efinix.EfxSapphireSocBUILDER INVOKE BUILD COMMAND-DONE] Build Command Execution: FailureIPGenerateFilesetException: [GENERATE _IP-ERROR] Build script failed in build command, 错误找不到或无法加载主类 saxon. board. efinix.EfxSapphireSoc

(1)重新安装Efinity,可能某些文件丢失。

(16)Traceback (most recent call last):

File "F:/efinity/scripts/efx_run_pt.py", line 59, in

File "F:/efinity/pt/binlengine.py",line 24,in

ImportError: DLL load failed while importing Qtwidgets: 找不到指定的模块

周四月22 24 1117- E:/efinity/python38/bin/python.exe finished. Exit code = 1 Exit st.

ERROR: Interface Designer constraint generation was not successful, will not proceed to efx_pnr...

Running placement and routing flow fail, See exit code and exit status.

说明:需要安装VC

(17)RISCV IP生成报错

[BUILDER_INVOKE_BUILD_COMMAND] stderr: Traceback (most recent call last): File "C:Efinity2023.2ipmip/efx_soc/efx_soc/embedded_sw/sw_script.py", line 677, in main() File "C:Efinity2023.2ipmip/efx_soc/efx_soc/embedded_sw/sw_script.py", line 121, in main shutil.copytree(Path(src_dir, f), dst=Path(loc, f), dirs_exist_ok=True) File "C:Efinity2023.2python311Libshutil.py", line 561, in copytree return _copytree(entries=entries, src=src, dst=dst, symlinks=symlinks, ^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ File "C:Efinity2023.2python311Libshutil.py", line 515, in _copytree raise Error(errors) shutil.Error: [('C:\Efinity\2023.2\ipm\ip\efx_soc\efx_soc\embedded_sw\software\freeRTOS\freertosUartInterruptDemo\src\freertos_risc_v_chip_specific_extensions.h',

.......

[BUILDER_INVOKE_BUILD_COMMAND-DONE] Build Command Execution: Failure

IPGenerateFilesetException: [GENERATE_IP-ERROR] Build script failed in build_command, Traceback (most recent call last): File "C:Efinity2023.2ipmip/efx_soc/efx_soc/embedded_sw/sw_script.py", line 677, in main() File "C:Efinity2023.2ipmip/efx_soc/efx_soc/embedded_sw/sw_script.py", line 121, in main shutil.copytree(Path(src_dir, f), dst=Path(loc, f), dirs_exist_ok=True) File "C:Efinity2023.2python311Libshutil.py", line 561, in copytree return _copytree(entries=entries, src=src, dst=dst, symlinks=symlinks, ^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^^ File

说明:可能是工程的路径太深。

-

RISC-V

+关注

关注

49文章

2946浏览量

53534

发布评论请先 登录

arm11 指令集 (ARM V6(ARM11)内核的指令集

matlab常见问题集

Proteus常见问题集

RISCV 操作常见问题集 - v6

RISCV 操作常见问题集 - v6

评论