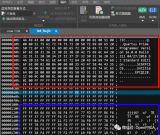

打开后的界面如下图所示,全英文显示。如果感觉自己的英文水平欠佳,可以使用谷歌浏览器打开该网页,并选择....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:33

•6371次阅读

在做在线远程升级的时候,一般需要两步:1、将数据写到外挂的flash中。2重新启动FPGA配置。 不....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:24

•2606次阅读

据《华尔街日报》最新报道,超微半导体(AMD)正就收购芯片制造商赛灵思(Xilinx)展开深入谈判,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-23 10:16

•2451次阅读

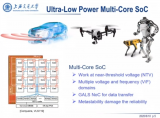

本文是一篇详细介绍ISSCC2020会议上一篇有关亚稳态解决方案的文章,该技术也使得FPGA在较高频....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-22 18:00

•5475次阅读

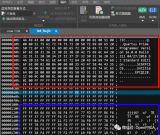

在基本的FPGA模块编写完成后,要使用仿真工具对设计的模块进行仿真,验证模块的基本功能是否符合设计。....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-21 09:44

•3213次阅读

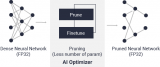

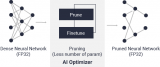

通过将 32 位浮点权值和激活量转换为 INT8 这样的定点,AI 量化器可在不影响预测精度的情况下....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-21 09:40

•5319次阅读

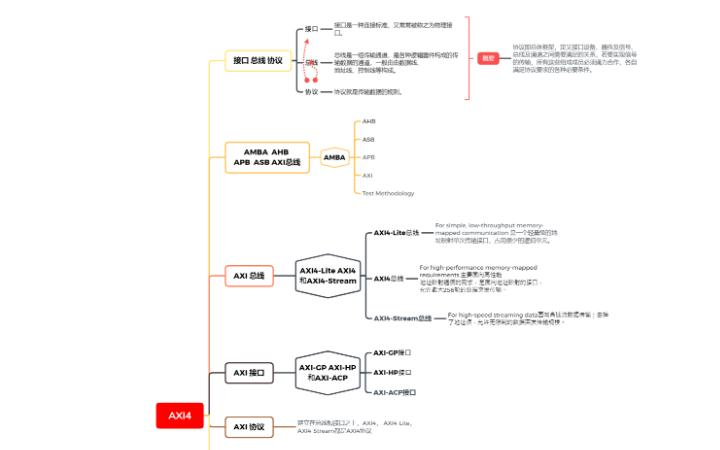

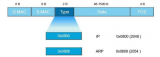

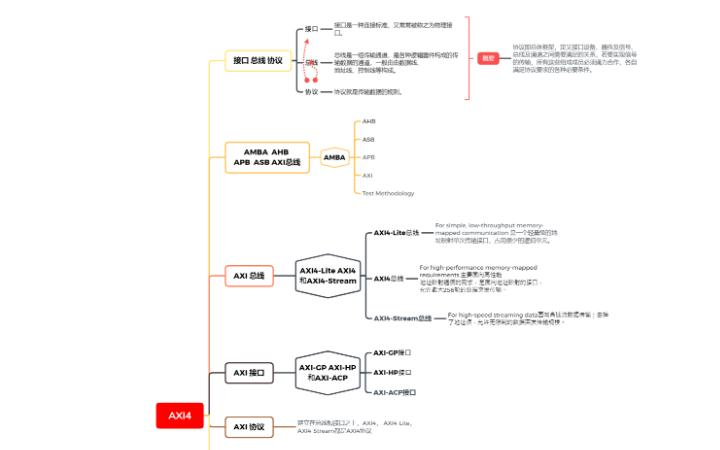

V1.0 ASB、APB是第一代AMBA协议的一部分。主要应用在低带宽的外设上,如UART、 I2C....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-10 17:19

•3793次阅读

很多工程师在使用Xilinx开发板时都注意到了一个问题,就是开发板中将LVDS的时钟输入(1.8V电....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 10-10 09:25

•13721次阅读

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。 总线是一组传输通道,是各....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-27 10:28

•7196次阅读

作为一名程序员,与计算机打交道的日子不计其数,不管你玩硬件还是做软件,你的世界自然都少不了计算机最核....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-27 10:10

•4102次阅读

描述 在《Zynq UltraScale+ MPSoC 数据手册》(DS925) 中,XAZU7EV....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-25 14:58

•7428次阅读

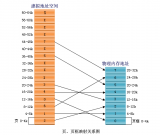

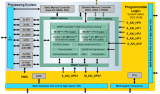

本文主要介绍CPLD和FPGA的基本结构。 CPLD是复杂可编程逻辑器件(Complex Progr....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-25 14:56

•14733次阅读

从在2010年夏天,RISC-V项目启动到今天已经整整十周年了。紧随RISC-V十岁生日,让我们来简....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-25 14:52

•3432次阅读

3线SPI的时钟产生方式和上一篇的4线SPI相同,这里不在叙述。两者的不同点在于:三线SPI模式需要....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:17

•7847次阅读

无论实现读还是写功能,都先要提供SCLK。假如FPGA系统工作时钟40MHz,我们可以利用计数器产生....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:15

•4422次阅读

3线SPI与4线SPI配置的主要不同之处在传输的数据格式以及I/O转换上。其读写数据格式由控制命令+....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:12

•7907次阅读

从ads52j90的数据手册我们不难发现,其SPI控制模块主要包含4根信号线SEN,SCLK,SDI....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:09

•7809次阅读

SDIO—当进行读操作时,SDIO作为输出口SDO,串行数据从ADC输出,进入FPGA;当进行写操作....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:07

•6192次阅读

最熟悉的度量两个量之间的相关性的方法是皮尔逊乘积矩相关系数(PPMCC),也称为“皮尔逊相关系数”,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-07 17:04

•28388次阅读

近日,一名黑客公布了从英特尔窃取的 20GB芯片机密工程数据。这些数据可能会导致多个平台的用户面临新....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-05 11:49

•4019次阅读

同学们在学网络课程的时候都知道,除巨帧外,常见的以太网帧的长度范围是64字节到1518字节,并且因为....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-05 11:46

•9951次阅读

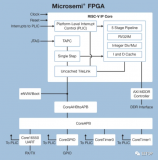

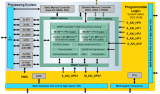

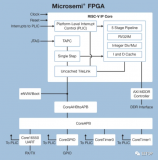

基于ZYNQ实现复杂嵌入式系统非常便利,其应用领域也越来越广泛,本文来从对ZYNQ芯片架构的理解来谈....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-05 11:44

•5921次阅读

Linux 内存是后台开发人员,需要深入了解的计算机资源。合理的使用内存,有助于提升机器的性能和稳定....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 10:46

•3193次阅读

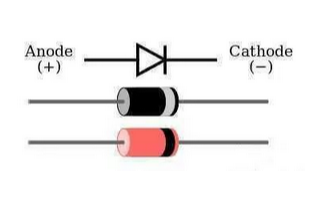

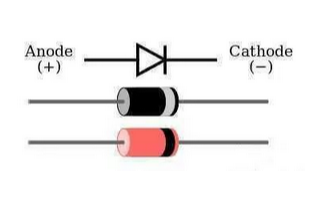

首先要开始这个话题要先说一下半导体。啥叫半导体? 半导体其实就是介于导体和绝缘体中间的一种东西,比如....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 08-25 17:41

•7740次阅读

8月30日,中国移动副总裁李正茂在2019世界人工智能大会“5G与人工智能”主题论坛上表示,2019....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 10:20

•4009次阅读

微软小冰一直是比较特殊的人工智能产品。相较于其他助手型人工智能产品,以少女形态出现在人们面前的小冰,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 10:09

•5499次阅读

8月29日下午,LG Display宣布,其在广州建设的8.5代OLED面板生产线正式投产。了解到该....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 09-01 09:51

•3227次阅读

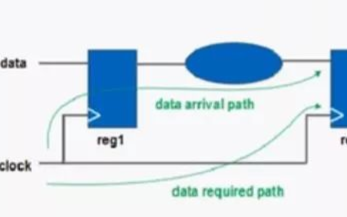

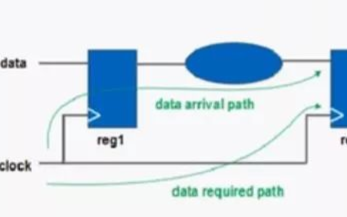

在输入信号到输出信号中,因为经过的传输路径、寄存器、门电路等器件的时间,这个时间就是时序。开发工具不....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-31 14:50

•7265次阅读

接着开始正文。据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-31 09:45

•7654次阅读

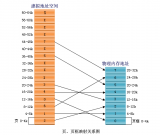

比如,一个16MB的程序和一个内存只有4MB的机器,OS通过选择,可以决定各个时刻将哪4M的内容保留....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 07-28 09:56

•14162次阅读