来到我所在的工作车间,提取指令的小A、分析指令的小胖和负责结果回写的老K都已经到了,就差执行指令的我....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 05-03 09:28

•3179次阅读

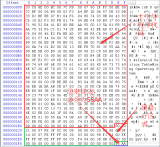

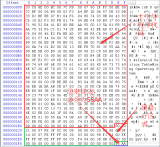

有符号数的计算在 Verilog 中是一个很重要的问题(也很容易会被忽视),在使用 Verilog ....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 05-02 10:48

•8745次阅读

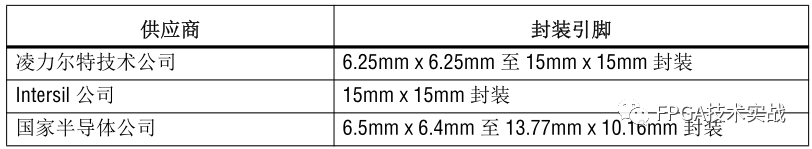

面向收发器 (SERDES) FPGA 的PDN设计对电源有严格的要求,需要干净的电压源。虽然低功耗....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 05-02 09:58

•2665次阅读

FPGA的应用 FPGA 是可编程再设计的“万能”芯片。FPGA (Field Programmab....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 14:22

•3027次阅读

1、 关于如何在VHDL模块调用一个Verilog模块 在VHDL模块声明一个要与调用的Verilo....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 14:06

•12516次阅读

一、前言 在嵌入式项目开发中,字符串格式化是很常见的操作,我们一般都会使用 C 库中的 sprint....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 13:43

•2437次阅读

学习内容 学习关于AXI总线的信号接口的具体要求(包括不同通道之间的关系,握手机制说明等)和AXI4....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 11:22

•5406次阅读

FPGA 是可以先购买再设计的“万能”芯片。FPGA (Field Programmable Gat....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 11:13

•7565次阅读

SVPWM SVPWM是空间矢量脉宽调制(Space Vector Pulse Width Modu....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 11:07

•9819次阅读

说起给单片机烧录程序,大家应该都不陌生,我最早接触单片机是从51单片机开始的,型号是STC89C52....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-30 11:02

•17502次阅读

锁相环(Phase Locked Loop,PLL)是一个闭环负反馈相位控制系统,至少包含3个基本单....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 15:17

•7717次阅读

这篇文章就以市场应用最为广泛的x86-x64架构为目标,通过学习了解它内部的100个寄存器功能作用,....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 14:32

•7189次阅读

如果你参加过IC校招面试,自然会被问到“setup/hold的概念,以及setup/hold违例怎么....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 14:15

•5539次阅读

线程被另一个线程通过 pthread_cancel() 函数取消,这和通过kill() 发送 SIG....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 13:41

•4170次阅读

目前,虽然基于C/C++等高层次综合相较于手写RTL层级HDL语言已大幅提升了开发效率,但随着相关技....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 11:44

•3106次阅读

ESP8266支持3种模式:Station模式、AP模式和Station+AP混合模式。关于这三种模....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 11:23

•16194次阅读

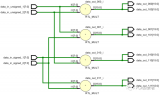

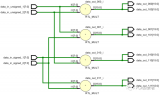

在一个项目中,当你使用microblaze作为控制器来进行系统调度的时候,一般是建议将所有模块封装成....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 11:17

•8974次阅读

笔者因为工作原因,接触到一种叫做RAC的定位产品,该定位产品不同于一般的定位模组,它产品外表看起来很....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 11:08

•3812次阅读

每一个做数字逻辑的都绕不开跨时钟域处理,谈一谈SpinalHDL里用于跨时钟域处理的一些手段方法。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 10:52

•5298次阅读

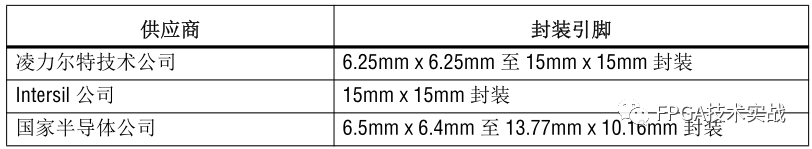

我们在进行FPGA原理图和PCB设计时,都会涉及到FPGA芯片管脚定义和封装相关信息,本文就Xili....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 10:45

•9363次阅读

引言:本文我们简单介绍下Xilinx FPGA管脚物理约束,包括位置(管脚)约束和电气约束。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-27 10:36

•6470次阅读

这篇文章的标题听起来像是上世纪90年代电视剧里的玩笑,但它实际上是一个严肃的问题。很多人不明白,是什....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-22 09:43

•6356次阅读

Xilinx zynq系列FPGA实现神经网络评估 本篇目录 1. 内存占用 1.1 FPGA程序中....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-19 11:12

•3487次阅读

最近偶尔需要用到SPI模块。正巧看到SpinalHDL中所提供的SPI-Master设计。看完之后尤....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-19 09:58

•4553次阅读

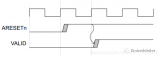

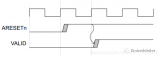

在FPGA视频图像处理系统中,经常需要使用到SDRAM作为视频图像缓存。SDRAM控制器可以分为上电....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-19 09:46

•7783次阅读

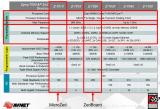

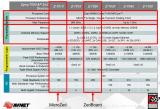

最近很多人讨论下一家收购FPGA企业的大佬是谁,Nvidia?Broadcom?说法不一,有人问德州....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-18 11:36

•2561次阅读

在嵌入式软件开发中,一个项目往往需要多人协作完成。

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-15 11:07

•2373次阅读

USB 4只采用USB Type-C连接器,USB 4讯号采双通道传输;而过去的连接器如USB Ty....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-15 10:58

•13648次阅读

在vivado中设置modelsim(即第三方仿真工具)的安装路径。在vivado菜单中选择“Too....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-15 10:10

•6833次阅读

SOPC技术,即软核处理器,最早是由Altera公司提出来的,它是基于FPGA的SOC片上系统设计技....

![的头像]() FPGA之家 发表于

FPGA之家 发表于 04-15 09:48

•11094次阅读