Vitis AI 开发环境是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘器件和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

全新 1.2 版本新增了以下功能:

Vitis AI 量化器和 DNNDK 运行时开源

AI Model Zoo 中添加了 14 个新参考模型(Pytorch, Caffe, Tensorflow)

Vitis AI 量化器支持优化的模型(剪枝)

更新了 DPU 命名规则,以在所有配置中保持一致

推出面向边缘和云的 Vitis AI Profiler

ONNXRuntime 和 TVM 支持 Vitis AI

新增了对 Alveo U50/U50LV 和 U280 的支持

Alveo U50/U50LV DPU DPUCAHX8H 微架构改进

升级 DPU TRD,以支持 Vitis 2020.1 和 Vivado 2020.1

Vitis AI 支持 Pytorch CNN 通用访问(测试版)

Vitis AI 平台的介绍

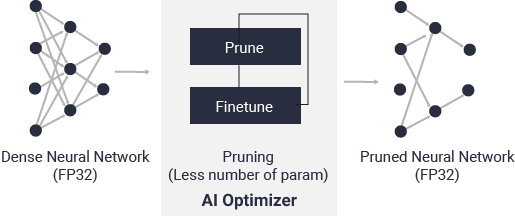

◆◆AI 优化器◆◆

有了世界领先的模型压缩技术,我们可以在对精度影响极小的情况下,将模型的复杂性降低 5 至 50 倍。深度压缩可将您的 AI 推断性能提升到一个新的层次。

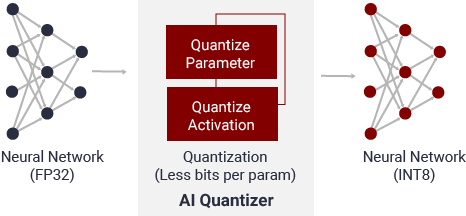

◆◆AI 量化器◆◆

通过将 32 位浮点权值和激活量转换为 INT8 这样的定点,AI 量化器可在不影响预测精度的情况下,降低计算复杂度。定点网络模型需要的内存带宽更少,因此比浮点网络模型速度更快,电源效率更高。

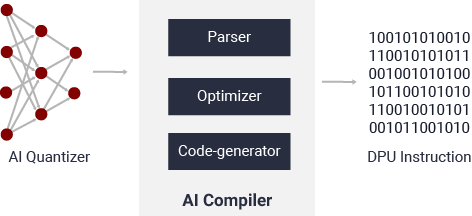

◆◆AI 编译器◆◆

将 AI 模型映射至高效指令集及数据流。还可执行高级优化任务,如层融合和指令排程等,并可尽量重复使用片上内存。

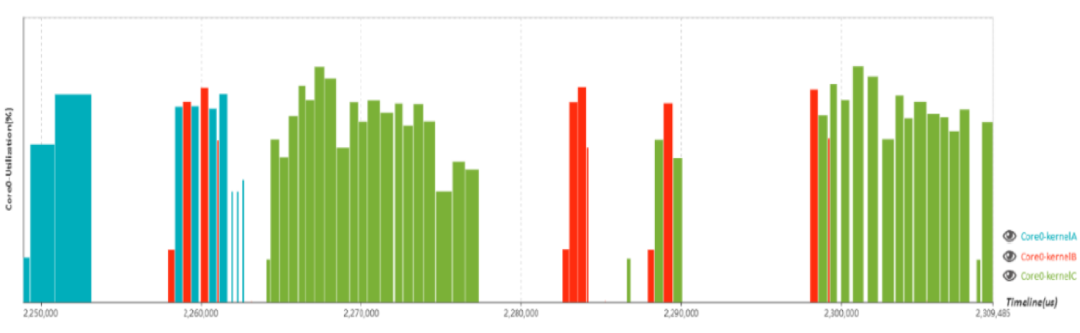

◆◆AI 配置器◆◆

性能分析器有助于程序员深入分析 AI 推断实现方案的效率和利用率。

◆◆AI 库◆◆

该运行时提供一系列轻量级 C++ 及 Python API,其可实现便捷的应用开发。此外,它还提供高效的任务调度、内存管理和中断处理。

责任编辑:lq

-

Xilinx

+关注

关注

73文章

2206浏览量

131898 -

AI

+关注

关注

91文章

41107浏览量

302593 -

人工智能

+关注

关注

1820文章

50324浏览量

266938

原文标题:速来,Xilinx Vitis AI 1.2 开放下载了!

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

曙光云AI全栈平台解锁政企AI新效能

基于Vitis Model Composer完成全流程AI Engine开发

全新AMD Vitis统一软件平台2025.2版本发布

如何在AMD Vitis Unified IDE中使用系统设备树

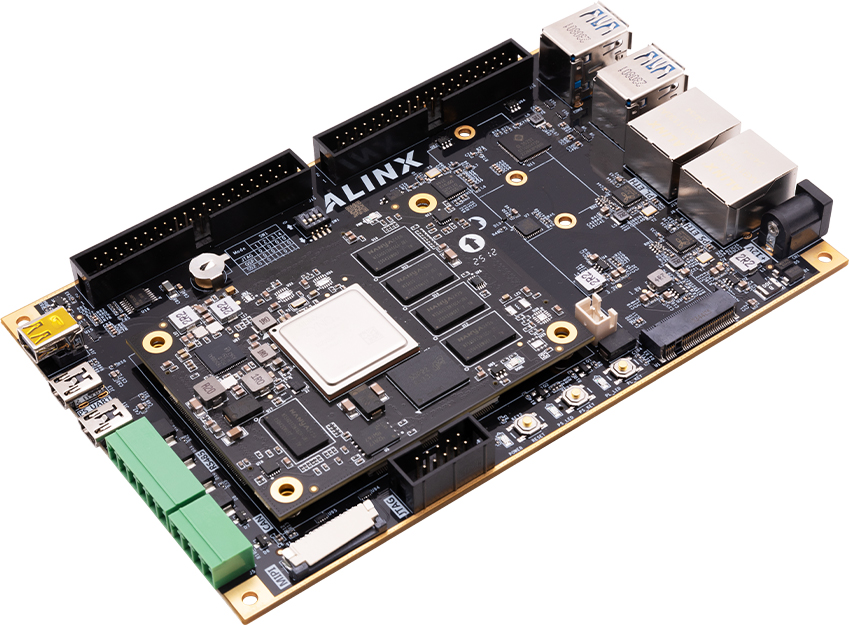

同系列性能更强!面向高性能 AI 应用,AXU2CGB-I 有何亮点?

AMD Vitis AI 5.1测试版现已开放下载

AMD Vitis AI 5.1测试版发布

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI的科学应用

【「AI芯片:科技探索与AGI愿景」阅读体验】+AI芯片的需求和挑战

LambdaTest推出全球首个AI智能体测试平台

全新AMD Vitis统一软件平台2025.1版本发布

使用AMD Vitis Unified IDE创建HLS组件

如何使用AMD Vitis HLS创建HLS IP

Vitis AI平台的介绍

Vitis AI平台的介绍

评论