台积电一条龙布局再突破,完成全球首颗3D IC封装技术,预计2021年量产。业界认为,台积电3D IC封装技术主要为未来苹果新世代处理器导入5纳米以下先进制程,整合人工智能(AI)与新型存储器的异质芯片预作准备,有望持续独揽苹果大单。

台积电向来不评论接单与客户状况。业界认为,台积电正式揭露3D IC封装迈入量产时程,意味全球芯片后段封装进入真正的3D新纪元,台积电掌握先进制程优势后,结合先进后段封装技术,对未来接单更具优势,将持续维持业界领先地位。

先进封装近来被视为延伸摩尔定律的利器,透过芯片堆叠,大幅提升芯片功能。台积电这几年推出的CoWoS及整合扇出型封装(InFO),就是因应客户希望一次到位,提供从芯片制造到后段封装的整合服务。

台积电强调,CoWoS及整合扇出型封装(InFO)仍是2.5D IC封装,为了让芯片效能更强,芯片业花了相当的时间,开发体积小、功能更复杂的3D IC,这项技术需搭配难度更高的矽钻孔(TSV)技术,以及晶圆薄化、导电材质填孔、晶圆连接及散热支持。

尽管台积电未透露合作开发对象,业界认为,3D IC封装技术层次非常高,主要用来整合最先进的处理器、数据芯片、高频存储器、CMOS影像感应器与微机电系统(MEMS),一般需要这种技术的公司,多是国际知名系统厂。以台积电技术开发蓝图研判,苹果应该是首家导入3D IC封装技术的客户。

-

台积电

+关注

关注

44文章

5811浏览量

177055 -

苹果

+关注

关注

61文章

24613浏览量

208748

原文标题:台积电完成全球首颗3D IC封装技术

文章出处:【微信号:SEMI2025,微信公众号:半导体前沿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

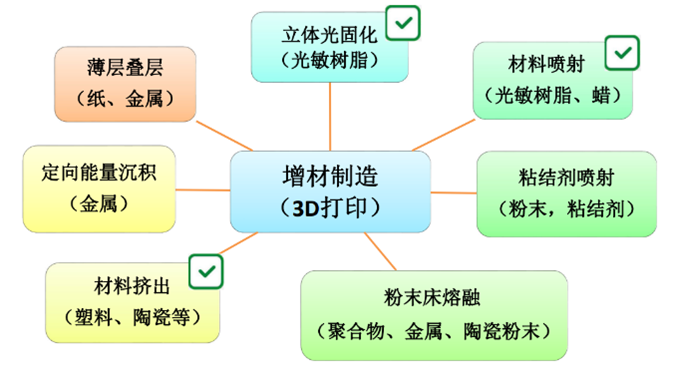

3D打印又火了!全球最大工厂将落地深圳

台积电完成全球首颗3D IC封装技术

台积电完成全球首颗3D IC封装技术

评论