和1Xnm半导体工艺的百花齐放相比,个位数的制程就显得单调许多了,很多在10Xnm大放异彩的半导体公司都在7nm制程处遭遇到了苦头。

随着AMD御用代工厂商GF宣布无限期延期7nm制程工艺,目前仅剩下的7nm工艺也只有台积电能够在现阶段实现量产,无论是华为的麒麟980处理器还是苹果的A12处理器,他们清一色地选择了台积电作为代工厂。

在这个赢者通吃的半导体工业中,台积电似乎占据了半壁江山,尤其是7nm这种先进制程工艺。而芯片行业也随着工艺难度的加深呈现贫富两极分化的情况。

为什么7nm工艺制程这么难?

在讨论7nm制程难度的时候,我们需要普及一个量子力学上的概念,这样子可以有助于我们理解为什么低制程的成本急剧提升,那就是量子隧穿效应。

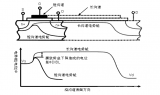

在量子力学里,量子隧穿效应指的是,像电子等微观粒子能够穿入或穿越位势垒的量子行为,尽管位势垒的高度大于粒子的总能量。在经典力学里,这是不可能发生的,但使用量子力学理论却可以给出合理解释。

如果通俗点来讲,就是说制程工艺到一定程度下,电路与电路之间的距离降低到一定程度就会出现量子隧穿效应,这些电子呈现的是一种我们所不知道的规律进行运动,于是这些不可控制的电子造成了半导体的漏电率急剧上升,有太多的能源被浪费在控制电子运动上,自然不能发挥晶体管应该有的性能,宏观上表现为处理器的发热量增加,但是性能没有太大的变化。

当然对于量子隧穿效应目前还没有完全能够消除的办法,毕竟这个已经属于自然规律,即使是量子力学我们也没有完全掌握,因此只能减少这种情况的发生。

这就意味着制造材料需要进行重新研发,而这种尖端技术的投入可能是无底洞,投资了一大笔钱,最后获得的成果或许不尽如人意,沉没成本实在太高,因此只有充足的资金才能够投入到更新的工艺制程的研发中去。

而实现低距离制程的还有一个重要的因素,那就是被称之为现代光学工业之花的光刻机,7nm制程的实现离不开高性能光刻机的运行,其中荷兰的ASML几乎垄断了全球顶级光刻机的份额。

众所周知,光刻机这种精密仪器制造成本高和制造时间漫长,其中ASML最新的光刻机之一的NXT2000i光刻机单台售价更是达到上亿美元,而NXT2000i光刻机也是进行7nm乃至于未来5nm制程的最佳利器,尽管光刻机售价高昂,但是追求者络绎不绝。

除了台积电之外,三星和Intel也砸巨资追求这台性能出色的光刻机,在产量有限的情况下,其他的芯片工艺制造商即使拥有合适的工艺,没有性能出色的光刻机,同样不能进行优秀的代工。这也就是7nm制程芯片成本急剧提升,量产困难的另外一个原因。

除了台积电,还有谁?

当然不差钱的主除了台积电之外,自然还有其他的半导体公司在追求7nm制程工艺,包括三星以及英特尔。和台积电进行纯粹的代工不同的是,三星和英特尔都有自己的产业链,也就是说自己就可以实现自给自足。当然这也是7nm时代能够存活下来的一个重要因素。

芯片代工讲究的是规模效应,前期投入的资金需要通过大量的芯片来平摊巨额的研发成本,同时芯片代工行业也是一个商业行为,企业追求是利润,如果没有利润,赔本的买卖相信大家都不愿意长期干下去。

而作为拥有完整IC设计的三星和英特尔自然拥有大量的芯片需求来满足自己的芯片代工行业。即使没有代工,他们同样可以自主满足7nm工艺制程的产能,而其他的芯片代工或许就没这么幸运了。

例如格罗方德先进制程制造公司,没有了AMD最新的Zen 2以及Navi显卡的订单,自然推广7nm制程的动力就小了很多,没有订单也没有利润,导致没有足够的研发资金投入到先进制程工艺的研发中去。

“马太效应”逐渐显现

马太效应,指强者愈强、弱者愈弱的现象,广泛应用于社会心理学、教育、金融以及科学领域。马太效应,是社会学家和经济学家们常用的术语,反映的社会现象是两极分化,富的更富,穷的更穷。

“马太效应”同样适用于7nm的芯片行业,在这个赢者通吃的行业中,像台积电凭借着率先实现的7nm工艺获得了大量的订单,而AMD也已经宣布未来的Zen 2和Navi显卡将会让台积电进行代工,海量的订单满足了台积电的7nm胃口,自然可以分摊巨额研发费用,同时还能赚取大量的利润进行更进一步的制程工艺中来,这种良性循环也让台积电的财报节节攀升。

而其他的芯片代工企业恐怕就过得不那么舒服了,没有率先占据7nm的高点,随后便失去客户的订单,同时也没有足够的预算进行研发投入,这样周而复始,自然也就退出了芯片行业的竞争中来。

而整个芯片行业也伴随着门槛的提升处于寡头化的情形,除非有黑科技大幅降低先进制程的制造成本,玩得转现在和未来芯片代工的最终还是那几个科技巨头。

-

芯片

+关注

关注

463文章

54429浏览量

469371 -

7nm

+关注

关注

0文章

267浏览量

36388

原文标题:从7nm看芯片行业的贫富差距

文章出处:【微信号:IC-008,微信公众号:半导体那些事儿】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

半导体芯片行业设备管理:核心逻辑+智能运维落地全攻略

绕开先进制程卡脖子:2026先进封装成中国AI芯片自主突围关键一战

2026年AI芯片破局指南:晶圆厂不再是瓶颈,先进封装才是核心胜负手

重磅研究:7nm FinFET 性能优化的隐藏密码 —— 栅极与鳍片间距调控

漏致势垒降低效应如何影响晶体管性能

国产芯片真的 “稳” 了?这家企业的 14nm 制程,已经悄悄渗透到这些行业…

“汽车智能化” 和 “家电高端化”

国产AI芯片真能扛住“算力内卷”?海思昇腾的这波操作藏了多少细节?

白光干涉仪在浸没式光刻后的3D轮廓测量

AMD 7nm Versal系列器件NoC的使用及注意事项

7nm时代,芯片行业的“马太效应”

7nm时代,芯片行业的“马太效应”

评论