大功率碳化硅(SiC) MOSFET模块的分级退饱和(Desat)保护、软硬短路区分及软关断技术深度研究报告

1. 碳化硅功率器件的技术演进与系统级保护的范式转移

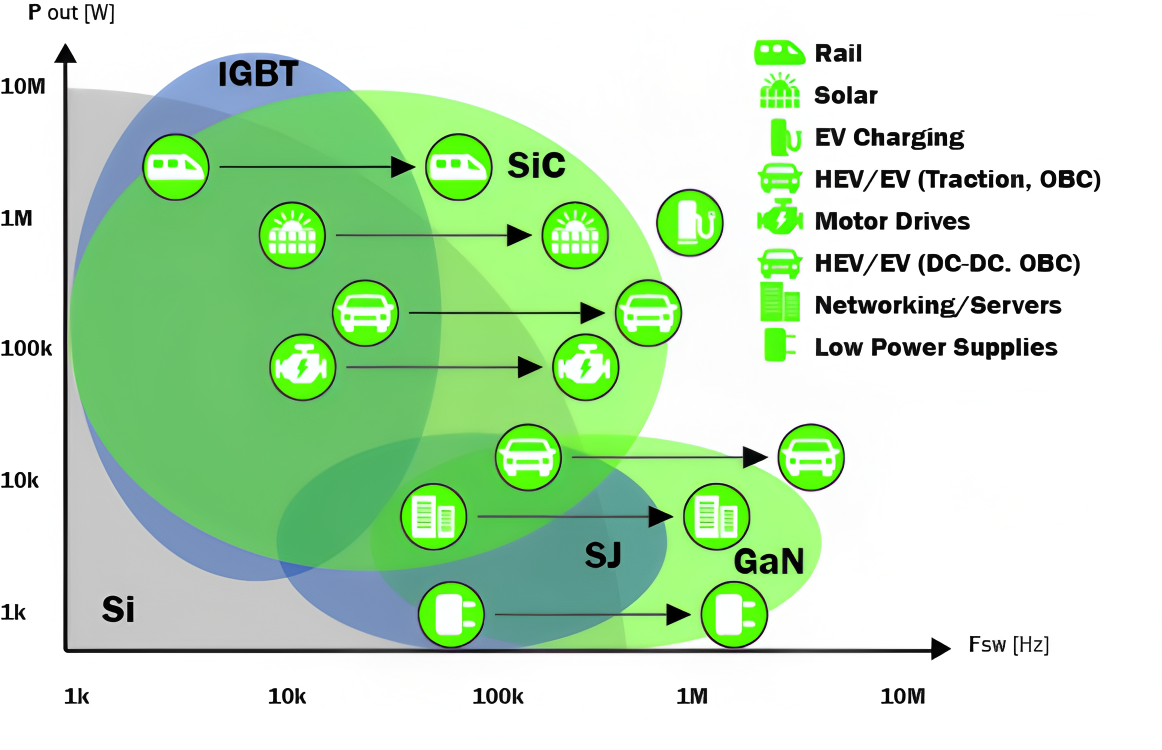

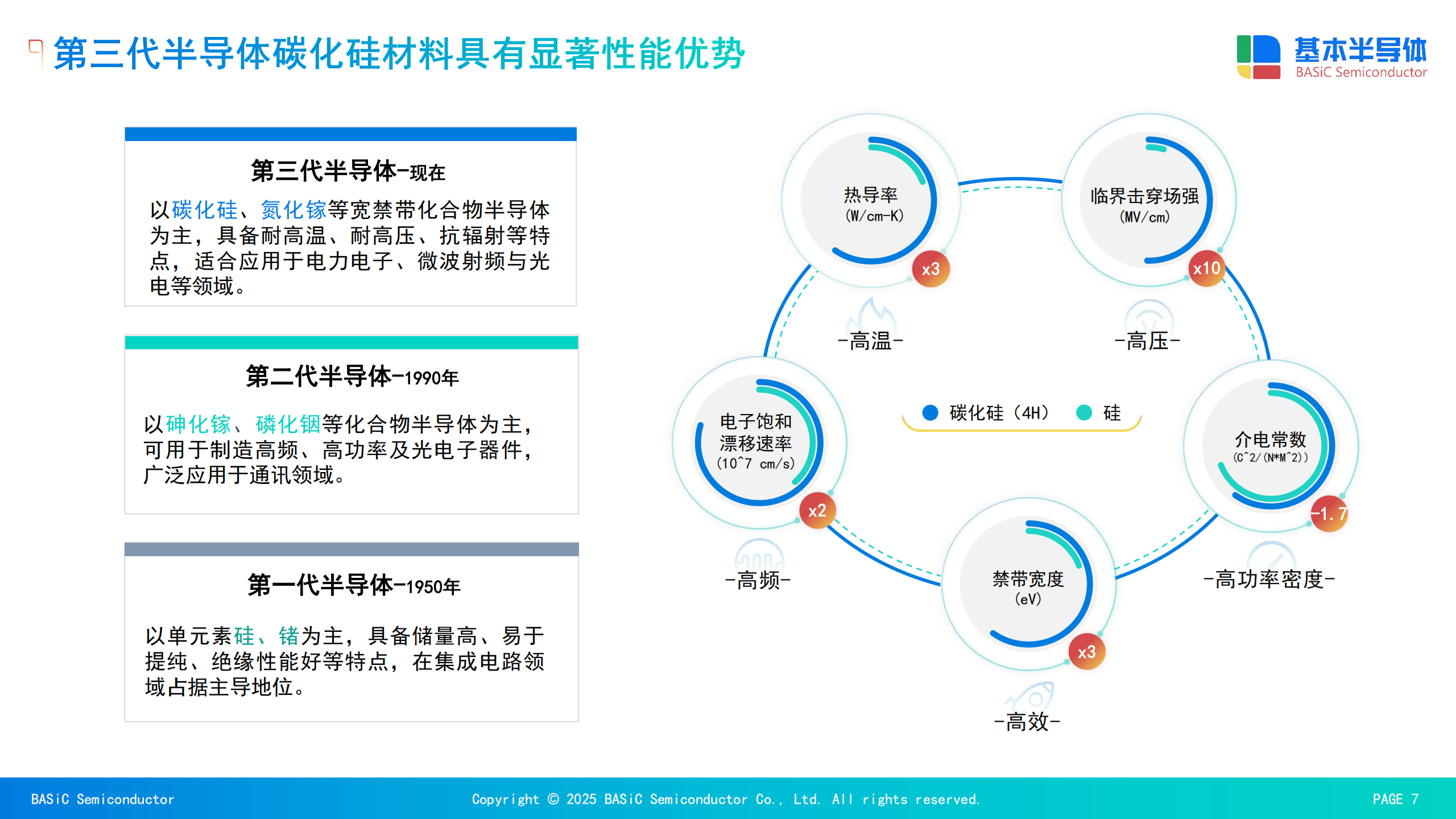

在当代高频、高效、高功率密度电力电子系统的发展浪潮中,碳化硅(SiC)宽禁带半导体材料凭借其颠覆性的电气和热力学特性,已经确立了其在航空航天、新能源汽车(EV)、固态变压器(SST)、高压直流输电以及大功率储能系统中的核心地位 。相较于传统的硅(Si)基绝缘栅双极型晶体管(IGBT),SiC 材料具有约 3.2 eV 的宽禁带宽度、高达 3 MV/cm 的临界击穿电场以及卓越的热导率 。这些底层的物理优势使得 SiC MOSFET 能够在极低的导通电阻(RDS(on))下承受超高的阻断电压。更为关键的是,作为单极型器件,SiC MOSFET 彻底消除了硅基 IGBT 在关断期间由少数载流子复合引起的“拖尾电流”现象,从而将开关损耗降低了数个数量级,使得电力电子变换器能够向百千赫兹(kHz)的超高频领域迈进 。 基本半导体一级代理商-倾佳电子力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板,PEBB电力电子积木,Power Stack功率套件等全栈电力电子解决方案。

基本半导体授权代理商倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

然而,SiC MOSFET 在实现极致电气性能的同时,也为系统级的高可靠性保护带来了前所未有的严峻挑战,其中最为核心的痛点便是其极度脆弱的短路耐受能力(Short-Circuit Withstand Time, SCWT) 。为了在给定的芯片面积内最大化地降低导通损耗,现代 SiC MOSFET 的元胞密度被设计得极高,沟道长度大幅缩短,同时栅极氧化层厚度也被削薄 。这种追求极限导通性能的结构设计导致器件在面临短路故障时,由于较短的沟道引起的漏极诱导势垒降低(Drain-Induced Barrier-Lowering, DIBL)效应,短路电流(ISC)可能在几百纳秒内瞬间飙升至额定工作电流的十倍以上 。

在传统的硅基驱动系统中,IGBT 通常具备长达 10μs 的短路耐受时间,这为驱动电路留出了充足的检测与响应窗口 。然而,大功率 SiC MOSFET 由于芯片面积较小,其热容(Thermal Mass)显著低于同等电流等级的 IGBT,导致在短路期间数兆瓦的瞬态功耗下,器件结温(Tj)以极其惊人的速率急剧攀升 。经验证,大功率 SiC MOSFET 的临界破坏时间通常不足 2μs 甚至更短 。这不仅要求保护电路必须在微秒级乃至纳秒级内做出关断决断,更要求保护机制在极高开关噪声(高 dv/dt 与 di/dt)环境下保持极高的抗干扰能力 。在此背景下,传统的单一阈值退饱和(Desaturation, Desat)保护已经无法满足安全需求,行业必须转向更为精细化、智能化的分级退饱和保护(Graded Desat Protection)与软关断(Soft Turn-Off)协同控制技术 。

2. SiC MOSFET 短路故障的微观物理失效机制解析

要设计出高鲁棒性的短路保护机制,首先必须深刻理解 SiC MOSFET 在极端短路应力下的微观物理失效机理。当短路持续时间超过器件的安全工作区(SOA)极限时,巨量的短路能量会在极短的时间内转化为热能,引发一系列不可逆的物理破坏 。

首当其冲的是热失控(Thermal Runaway)与寄生晶体管激活。在极高的漏源电压(VDS)与短路电流(ISC)的乘积作用下,SiC 芯片的结温可能瞬间突破 1000 K 。这种极端高温会激发半导体内部强烈的本征载流子激增,进而激活 SiC MOSFET 内部寄生的双极结型晶体管(BJT)结构。一旦寄生 BJT 被开启,栅极将完全失去对漏极电流的控制能力,导致漏源电流彻底失控并呈指数级雪崩增长,最终在几微秒内将芯片物理烧毁熔融 。这种失效模式在故障能量极高的情况下尤为常见,且往往伴随着封装的灾难性炸裂 。

其次是栅极氧化层的不可逆退化与击穿。SiC MOSFET 为了实现较低的驱动阈值和极低的导通电阻,其栅极氧化层(SiO2)被设计得相对较薄 。在短路事件中,极高的电场与瞬态高温的双重应力共同作用于这一脆弱层。大量的热激发生电子和空穴会注入并隧穿氧化层,造成氧化层内部陷阱电荷的累积。研究表明,即使短路能量未能直接导致芯片热熔毁,也会在栅极结构中造成不可逆的损伤,表现为栅漏极或栅源极之间的短路失效(Gate-Source Failure) 。必须指出的是,当发生热失控时,必然伴随着栅源极失效,反之亦然 。

最后,热机械应力疲劳(Thermomechanical Stress)也是大功率模块中不容忽视的短路失效诱因。短路瞬间的局部极端热冲击会在 SiC 芯片、底层高温焊料以及陶瓷覆铜板(如 Si3N4 AMB 或 AlN DCB)之间产生巨大的温度梯度 。由于不同材料之间热膨胀系数(CTE)的显著失配,巨大的剪切应力会迅速撕裂焊料层或导致顶部铝键合线脱落断裂 。这种应力疲劳不仅在单次严重短路中致命,在多次连续的轻微短路冲击下同样会引发模块层面的结构性失效。

3. 短路故障类型的精细化分类与电气轨迹演变

在实际的电力电子变流器(如储能逆变器、高压电机驱动或固态变压器)中,由于故障发生的位置、时机以及外部回路阻抗的差异,SiC MOSFET 所面临的短路故障在电气波形演变上呈现出完全不同的特征。准确甄别这些故障类型是实现分级保护的逻辑前提。工业界与学术界通常将短路故障细分为两至三种主要类型:硬开关故障(Hard Switching Fault, HSF)、负载短路故障(Fault Under Load, FUL)以及第三象限短路 。

第一类短路:硬开关故障 (HSF / Type I Short Circuit)

硬开关故障(HSF),通常被称为“硬短路”或 Type I 短路,发生在器件从关断状态(Off-state)主动开通到一个已经存在短路的低阻抗回路中 。典型的系统级场景包括同一桥臂的上下管直通(Shoot-through),或者由于接线错误导致母排直接短路 。

电气波形与演变轨迹:在此类故障发生前,器件处于阻断状态,承受着全部的直流母线电压(VDC)。当栅极驱动信号(VGS)上升并跨过阈值电压(VGS(th))时,由于回路中仅存在极小的大功率模块与母排杂散电感(Lσ,通常在十几至几十纳秒级别,如 BASiC 62mm 模块标称的 ≤14 nH ),漏极电流(ID)将以极其恐怖的速率(di/dt 可达数 kA/μs)飙升 。 根据电感电压方程 VL=Lσ⋅(di/dt),极高的电流变化率会在杂散电感上产生明显的感应压降。因此,在导通的最初几百纳秒内,漏源电压(VDS)会从 VDC 出现一个短暂而微小的跌落 。然而,当极速飙升的电流触及 SiC 芯片物理结构的饱和电流上限(ID,sat)时,di/dt 骤降至零,杂散电感上的压降瞬间消失,VDS 迅速反弹并被死死钳位于接近直流母线的高电压水平 。保护挑战:HSF 的核心特征是器件同时、且从一开始就承受着极限高压与极限大电流。瞬态功率耗散极大,短路耐受时间极短,驱动器必须在没有任何系统级延迟的情况下实施无条件的最快硬件切断 。

第二类短路:负载短路故障 (FUL / Type II Short Circuit)

负载短路故障(FUL)或 Type II 短路,发生在器件已经处于正常的深度导通状态(ON-state)并承载正常工作电流时,外部负载回路突然发生短路或绝缘击穿 。

电气波形与演变轨迹:在故障前夕,VGS 处于稳定的正偏置电压(如 +18 V),器件运行在极低压降的线性区(Ohmic Region),VDS 仅由负载电流与极低的导通电阻(RDS(on))决定(例如几十至几百毫伏) 。短路发生后,由于故障点通常位于电机绕组、变压器副边或较长的外部电缆处,整个短路回路包含了巨大的感抗(μH 甚至 mH 级别)。因此,短路电流 ID 的攀升速度(di/dt)相对平缓得多 。 随着电流的逐渐增大,器件的本征跨导(Transconductance)无法继续维持其在线性区的工作状态,芯片开始被迫脱离线性区,向有源饱和区(Active/Saturation Region)转移。在这一阶段,VDS 呈现出极其经典的“退饱和(Desaturation)”现象,即电压从极低水平开始,随着电流的攀升而缓慢爬升,最终在长时间后才趋近于母线电压 VDC 。保护挑战:FUL 具有极强的隐蔽性。由于短路初期 VDS 爬升缓慢,如果保护阈值设定过高或响应延迟过长,器件将在这种非稳态的过渡区累积惊人的热量(因为耗散功率 P=VDS(t)⋅ID(t) 随时间积分在不断累加) 。这种热累积如果不被及时切断,即便随后触发了保护,器件也可能由于内部热机械应力或超过结温极限而造成隐性内伤或直接烧毁 。因此,针对 FUL,保护电路必须具备极高的灵敏度与智能的缓变信号捕捉能力。

第三类短路:第三象限短路 (Type III Short Circuit)

除了上述两种最常见的工况,在电机驱动或四象限变流器应用中,SiC MOSFET 频繁运行在第三象限(反向导通模式)。当器件在此状态下遭遇负载侧短路时,它会被迫从低电压的反向续流状态(通过体二极管或沟道同步整流)瞬间切换至高压、大电流的正向短路状态 。这种剧烈的模式切换对器件的体二极管反向恢复(Reverse Recovery)以及驱动器的负压钳位能力提出了严苛的考验,往往容易诱发桥臂内额外的位移电流串扰。

下表对大功率应用中硬短路与软短路的关键特征进行了系统性对比与总结:

| 故障触发时机 | 器件刚接收导通脉冲的瞬间 | 器件已处于稳态导通的中后期 |

| 回路等效感抗 | 极小 (数十纳秒级 Lσ) | 较大 (包含外部负载/线缆的 μH 级电感) |

| 电流变化率 (di/dt) | 极其陡峭,瞬间达到饱和极限 | 相对平缓,受限于外部大感抗 |

| VDS 电压轨迹 | 初始即为极高电压,微跌后钳位于母线电压 | 从极低导通压降缓慢爬升,最终逼近母线电压 |

| 热损毁主导因素 | 极限功率峰值带来的瞬间热震与热失控 | 长时间非稳态中高压大电流并存导致的累积热量 |

| 保护逻辑核心诉求 | 零容忍的极速关断,强效对抗高 dv/dt 噪声 | 灵敏的斜率捕捉,防止高阈值盲区带来的延迟热毁 |

| 对比维度 | 硬开关短路 (HSF / Type I) | 负载软短路 (FUL / Type II) |

|---|

4. 传统退饱和(Desat)保护的数学模型与SiC适配性瓶颈

在剖析了短路的物理机制与电气特征后,必须探讨现有的检测手段。退饱和(Desaturation, 简称 Desat)检测由于其原理简单、无需在主功率回路中串联昂贵的霍尔传感器或高损耗的分流电阻,长期以来一直是高功率 IGBT 模块短路保护的工业标准 。

传统 Desat 的检测机制与数学模型

标准的 Desat 保护电路依托于驱动芯片内部的逻辑单元,主要由一个高压隔离阻断二极管(Blocking Diode)、一个恒流源(ICHG)、一个消隐电容(Blanking Capacitor, CBLK)以及电压比较器组成 。 在正常的稳态导通期间,恒流源(通常在 500 μA 至 1 mA 之间)通过隔离二极管流入处于极低 RDS(on) 状态的功率器件漏极。此时,检测引脚上的电压 VDESAT 被强行钳位在:

VDESAT=VDS(on)+VF(diode)

其中,VF(diode) 为高压二极管的正向压降。

一旦发生短路(不论是 HSF 还是 FUL),器件退出线性区进入饱和区,VDS 急剧升高,导致隔离二极管反向偏置而截止。此时,芯片内部的恒流源 ICHG 无法继续流向漏极,转而对消隐电容 CBLK 进行线性充电 。电容上的电压随时间 t 变化的规律为:

VDESAT(t)=CBLKICHG⋅t+Vclamp

当该电压越过驱动器内部设定的退饱和阈值电压(Vth,DESAT)时,比较器翻转,系统确认为短路故障并触发关断动作 。

为了防止器件在正常的硬开关开通瞬间(此时 VDS 从千伏级别下降至零点几伏的过程需要几十到上百纳秒的时间)触发误保护,电路必须引入消隐时间(Blanking Time, tblk)。消隐时间的数学表达式为 :

tblk=tcla+tRC

式中,tcla 是内部钳位开关释放的初始延迟,tRC 则是电容 CBLK 从初始电压充电至阈值 Vth,DESAT 所需的时间。

移植至 SiC MOSFET 面临的核心瓶颈

将上述基于 IGBT 特性设计的标准 Desat 模型直接移植到 SiC MOSFET 驱动系统中,会遭遇极其严重的适配性悖论 :

第一,长消隐时间与极短临界耐受时间的矛盾。对于 IGBT 而言,高达 10 μs 的短路耐受时间允许设计者配置 3~5 μs 的消隐时间,以充分滤除开通噪声 。然而,SiC MOSFET 的短路临界时间通常小于 2 μs 。如果依然采用微秒级的消隐时间,SiC MOSFET 将在保护动作触发前就被彻底烧毁 。为了将保护响应时间压缩至 1 μs 以内,必须大幅减小 CBLK,但这将直接削弱系统的抗噪声能力 。

第二,极高 dv/dt 引发的致命位移电流与误触发。SiC MOSFET 的核心优势是超快开关速度,其正常的导通与关断 dv/dt 动辄超过 50 V/ns(大功率下甚至突破 100 V/ns) 。在如此陡峭的电压变化率下,Desat 检测回路中高压隔离二极管的本征结电容(Cj)将成为极其敏感的干扰源。根据公式 Idisp=Cj⋅(dvDS/dt),极高的 dvDS/dt 会在二极管反向恢复或高频振荡期间产生巨大的位移电流(Displacement Current) 。 这股不可忽视的位移电流会反向注入检测节点,瞬间抬高消隐电容 CBLK 上的电压,极易导致比较器在器件正常工作时发生误触发(False Triggering) 。这就构成了 SiC 保护设计中最棘手的矛盾:为了抗击高 dv/dt 噪声,需要增大 CBLK;而为了保证 SiC 的生命安全,又必须减小 CBLK 以缩短 tblk 。

第三,转移特性差异导致阈值设定困难。与 IGBT 在退饱和时具有明显的限流平台特征不同,SiC MOSFET 由于较低的跨导(Transconductance),在进入饱和区后,其短路电流依然会随着 VDS 的升高而呈现明显的非线性增长,缺乏一个理想的平坦限流区 。如果将 Vth,DESAT 设置得像 IGBT 那样高(7V~9V),那么在软短路(FUL)发生时,由于 VDS 上升缓慢,检测将面临漫长的盲区延迟 。反之,若盲目降低 Vth,DESAT,又会在正常的大负载电流峰值处频繁引发误报警。

5. 分级退饱和(Graded Desat)保护的动态架构与软硬短路区分逻辑

为了在纳秒级开关噪声的干扰下,精准且极速地保护极其脆弱的 SiC MOSFET,现代先进驱动系统(例如 Bronze Technologies 开发的 2CP0225Txx-AB 和 2CP0425Txx 等高度集成的 SiC 专用即插即用驱动板 )彻底摒弃了单一维度的保护思路,转而采用了极为复杂的分级退饱和保护(Graded Desat Protection 或 Two-Level Desat)以及多维状态机逻辑 。

分级 Desat 的核心哲学在于:通过多阈值检测网络与动态消隐时间的交叉配合,实现对不同严重程度、不同阻抗特征短路故障(HSF 与 FUL)的分类响应与自适应处理 。

级限一:针对软短路 (FUL/Class II) 的“低阈值-长延迟”捕捉逻辑

当系统处于稳态运行中突然发生负载短路(Class II 短路)时,短路阻抗较大导致 VDS 呈现缓慢的斜率爬升 。如果在这种工况下采用单一的高阈值检测,SiC 器件将在检测盲区内承受漫长的高压大电流双重折磨,累积致命的热量 。 为了破解这一难题,分级保护的第一级会设定一个相对较低的电压检测阈值(Low Vth,DESAT,例如适配 SiC 器件特性的 3V~5V),并赋予其一段相对较长的时间判定窗口(Longer Trip Delay) 。逻辑机理:由于软短路多发生于器件稳态导通期,此时避开了开通瞬间恶劣的 dv/dt 噪声与位移电流干扰,因此采用极低的电压阈值并不会引发误触发 。相反,低阈值能够像“过流限幅器”一样,敏锐地捕捉到 VDS 刚刚开始脱离欧姆区的微小异常,在热量累积到不可逆阶段之前,提前介入并触发保护机制 。该机制从根本上弥补了传统高阈值 Desat 面对大电抗软短路时反应迟钝的致命缺陷。

级限二:针对硬短路 (HSF/Class I) 的“高阈值-极短消隐”切断逻辑

当器件直接开通到极低阻抗的桥臂直通短路路径(Class I 短路)上时,巨大的 di/dt 导致 VDS 会瞬间被钳位于直流母线高压 。这种灾难性的故障不允许系统有任何的迟疑,必须在微秒级内做出决断。 因此,分级保护的第二级设有一个较高的触发阈值(High Vth,DESAT,例如 7V~9V 甚至更高),并配合极致压缩的消隐时间(Ultra-short Blanking Time,通常在 1 μs 左右) 。逻辑机理:较高的阈值设计主要用于跨越器件正常硬开关导通初期那几百纳秒内剧烈的电压震荡与高 dv/dt 带来的位移电流伪影,构筑起强大的抗干扰屏障(Noise Immunity) 。而在高阈值确认越界后,基于内部 ASIC 极速的硬件数字状态机,系统会立刻发出最高优先级的保护指令,将总体的故障响应时间(从短路发生到开始执行关断动作)强制压缩在 1 μs 甚至更短的时间内,确保在 SiC 芯片热失控前强行切断毁灭性的能量洪流 。

以青铜剑技术(Bronze Technologies)的 2CP0225Txx 系列即插即用型驱动器为例,其内置的硬件管理器(Hardware Manager)在底层芯片架构上完美融合了这种多维逻辑 。当开通指令下达后,专用 VDS 监控电路开始实时采集管压降:若波形特征符合 Class I 直通短路,极短时间的硬件逻辑将瞬间接管,在 1 μs 内锁定;若呈现 Class II 缓慢退饱和特征,则动态延长监控窗口以确保判断的准确性,随后果断触发保护 。这种分级响应不仅保全了极低热容的 SiC 芯片,也最大程度地保障了宏观逆变系统的连续可用性 。

6. 软关断(Soft Turn-Off)与多级降压控制的过电压抑制策略

通过复杂的硬件逻辑精准识别出短路故障并下达保护指令,仅仅完成了 SiC MOSFET 保护战役的上半场。在确认短路后,如何“安全、平稳地”将承载着极端过载电流的半导体器件关断,是决定生死存亡的下半场 。

硬关断诱发的毁灭性雪崩过电压

如果在短路状态下,驱动系统依然沿用正常工况下的快速关断策略(即硬关断,Hard Shutdown),以极小的驱动电阻(如 RG(off) 在 12 Ω 级别)将栅极电荷在几十纳秒内瞬间抽干,流经功率模块的数千安培故障电流将遭遇暴跌 。 这种高达 1020 kA/μs 的电流断崖式下降(−di/dt),作用于功率模块封装和系统母排的杂散电感(Lσ)上,会激发出骇人的反向感应电动势 。根据公式:

VDS,peak=VDC+Lσ⋅

dtdiSC

在 800V 或 1000V 的直流母线系统中,瞬态过压尖峰(Voltage Spike)极易瞬间突破 SiC 器件 1200V 的物理耐压极限(VDSS),导致极其惨烈的非钳位感性开关(UIS)雪崩击穿甚至模块炸毁 。

软关断(Soft Shut Down, SSD)技术

为了在掐断故障与抑制过电压之间寻求完美的平衡,现代高端驱动器全面标配了软关断(Soft Turn-Off, STO 或 SSD)机制 。软关断的核心思想是:摒弃瞬间截断,改为通过主动控制栅极电容(CGS 和 CGD)的放电速率,缓慢拉长器件的线性下降区间,从而有效压低 di/dt,将关断过电压限制在绝对安全的范围之内 。

在电路实现上,通常会在驱动级旁路设置一条独立的、串联大阻值电阻(RSTO)和专用延时电容(CSTO)的软关断放电回路,或者采用专门受控的缓降 BJT 缓冲网络 。一旦收到短路保护触发信号,主关断通路(低阻抗)被立即屏蔽,系统强制切换至高阻抗的 STO 慢速放电路径,使 VGS 呈平缓斜坡下降 。

两级降压关断(Two-Level Turn-Off / Multi-Level Turn-Off)架构

虽然纯粹的大电阻软关断能够抑制过压,但如果下降过慢,器件将在高耗散的饱和区停留过久,短路损耗(ESC)的剧增同样会导致热失控 。为了进一步追求极致的保护效能,诸如 TI UCC217xx 家族、ST TD350E 以及 Microchip mSiC 等旗舰级驱动方案,引入了更为高级的“两级降压关断(Two-Level Turn-Off / TLTO)”动态策略 。

TLTO 的动态执行序列:

第一级限流降压(Current Limiting Stage):当分级 Desat 检测到短路并触发后,驱动器并不会立刻将栅极拉向负压,而是迅速将栅极电压从正常的高电平(如 +18V)阶跃式拉低至一个精心设计的中间平台电压(Intermediate Voltage,通常在 +5V 至 +8V 之间) 。在这一较低的栅压水平下,SiC MOSFET 的沟道电阻显著增大,强制将原本可能高达数千安培的短路电流瞬间压制到一个相对较低的水平 。这一动作犹如在洪峰来临前紧急落下的闸门,极大遏制了短路能量指数级的暴增。

第二级深度关断(Deep Turn-Off Stage):器件在平台电压上停留一段极短的、可编程的延迟时间(通常在几百纳秒到 1μs 左右,用以耗散掉初始的峰值电感能量并平滑 di/dt)后,驱动器再将栅极电压彻底拉低至负向偏置电平(如 -4V 或 -5V) 。由于此时短路电流已经被第一级动作大幅削弱,执行彻底关断时产生的 L⋅di/dt 电压尖峰自然大幅降低。

这种结合了分级 Desat 识别与多级电压轨迹卸载的体系,堪称目前大功率 SiC 保护领域的最高工程艺术,它完美调和了“快速止损”、“抑制过压”与“防误触发”这一几乎不可逾越的技术“不可能三角” 。

7. 封装级寄生参数优化与大功率商用模块性能纵览

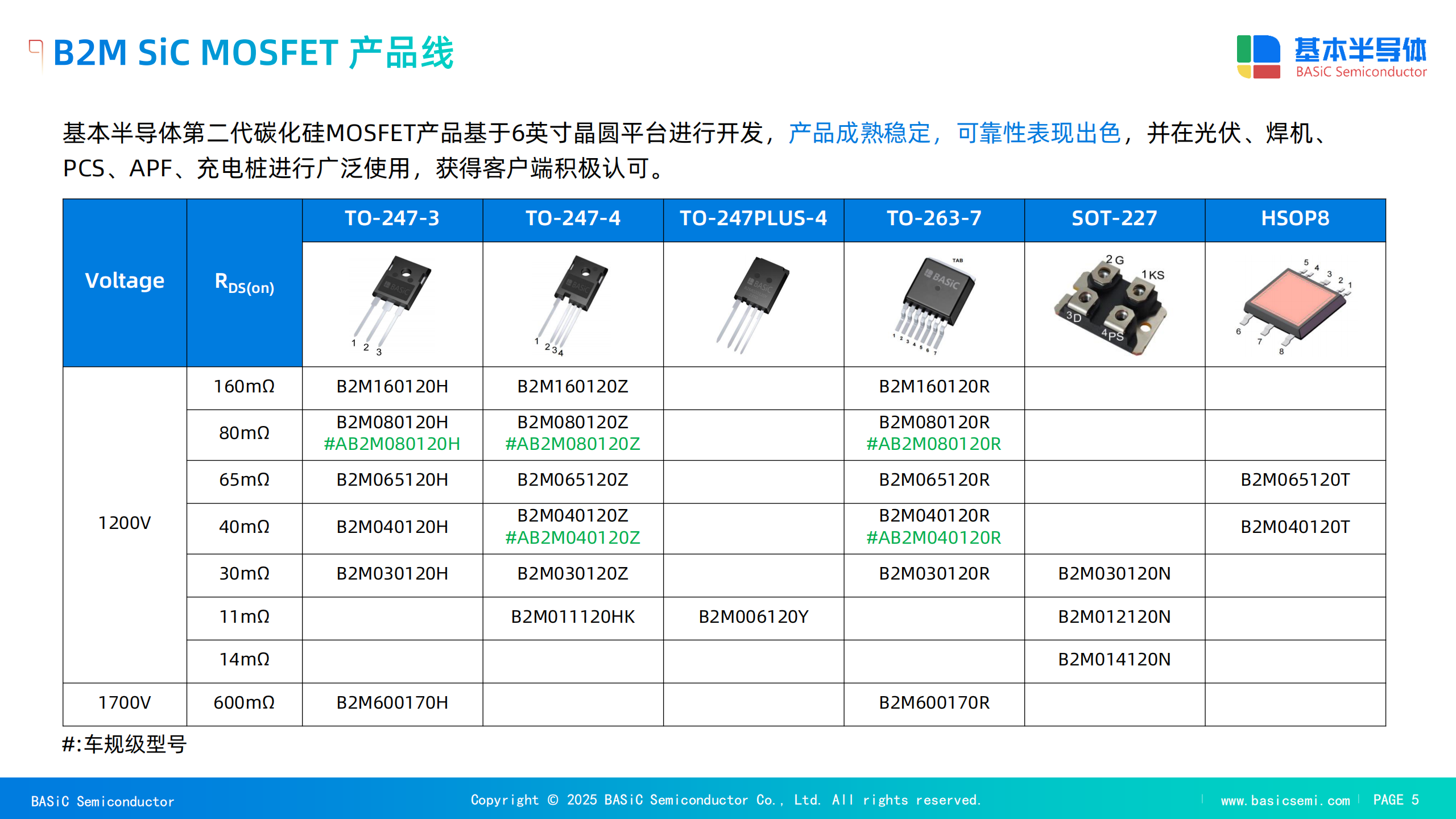

即便拥有了顶级的驱动保护逻辑,若没有优异的半导体模块封装结构作为物理支撑,系统在面临极限短路冲击时依然脆弱不堪。基本半导体(BASiC Semiconductor)针对工业及汽车级大功率需求,推出了一系列深度优化的 SiC 模块解决方案(如 62mm BMF540R12KA3 及 ED3 BMF540R12MZA3 等) 。分析其物理规格,可深刻洞察现代高可靠性系统如何从材料学与寄生参数控制层面应对短路与高频应力 。

高韧性 Si3N4 AMB 陶瓷覆铜板的引入

在几微秒的极限短路时间内,热量几乎完全淤积在芯片和绝缘基板内部,这就对封装材料的热冲击承受力提出了严苛挑战。传统模块多采用氧化铝(Al2O3)或氮化铝(AlN)作为绝缘基板,但它们的抗弯强度较差(Al2O3 约 450 N/mm2,AlN 仅 350 N/mm2),在经历短路热震后极易发生脆性断裂或铜箔剥离分层 。 BASiC 高性能模块全面引入了氮化硅(Si3N4)活性金属钎焊(AMB)技术 。Si3N4 具备高达 700 N/mm2 的抗弯强度和 6.0 Mpam

的断裂韧性,不仅热导率达到 90 W/mK(远超 Al2O3),而且在 1000 次极端的温度冲击循环实验后,依然保持极高的剥离强度(≥10N/mm)而不出现任何分层现象 。这种坚韧的热力学屏障,为 SiC 芯片抵御短路期间瞬态温升所引发的热机械应力疲劳(Thermomechanical stress)提供了坚实的物理基础。

寄生电感抑制与内置 SBD 的可靠性提升

极致的低感设计:大电流模块(如 BMF540R12KA3)通过内部叠层铜排布局优化,将杂散电感(Lσ)控制在 14 nH 及以下 。这一指标至关重要:更低的 Lσ 意味着在同等的软关断(STO) −di/dt 斜率下,诱发的过压尖峰更低,从而允许驱动器采用更为激进的关断速度,从整体上缩短短路能量的持续注入时间 。

内置 SiC SBD 防双极性退化:模块内部通过并联 SiC 肖特基势垒二极管(SBD),不仅大幅降低了反向续流的管压降,更从根本上消除了 SiC MOSFET 体二极管长时反向导通可能诱发的双极性退化(Bipolar Degradation / Stacking Fault 扩展)风险,实测证明导通电阻变化率抑制在 3% 以内,全方位护航全生命周期的系统可靠性 。

以下为几款典型大功率模块在短路评估与高频选型中的关键静态参数对照表:

| BMF240R12E2G3 | Pcore™2 E2B 半桥 | 1200 V | 240 A | 5.5 mΩ | 4.0 V | TBD | +18V / -4V |

| BMF360R12KHA3 | 62mm 半桥 | 1200 V | 360 A | 3.3 mΩ | 2.7 V | TBD | +18V / -5V |

| BMF540R12KA3 | 62mm 半桥 | 1200 V | 540 A | 2.5 mΩ | 2.7 V | ≤14nH | +18V / -4V |

| BMF540R12MZA3 | Pcore™2 ED3 半桥 | 1200 V | 540 A | 2.2 mΩ | 2.7 V | TBD | +18V / -5V |

| 产品型号 | 封装与拓扑 | VDSS | 额定电流 (IDnom) | RDS(on)(25℃) | VGS(th)典型值 | 回路杂散电感 | 驱动工作电压 |

|---|

(数据综合整理自 BASiC Semiconductor 的产品应用手册及预发布数据手册 )。

有源米勒钳位(AMC)防二次直通保护

在大功率驱动层面,必须考虑相间高 dv/dt 带来的寄生导通灾难。当半桥中的上管极速开通时,巨大的 dv/dt(通常 > 50V/ns)会通过下管的反馈电容(Cgd)抽取位移电流,并流经关断电阻。如果由此在栅极激发的感应电压超过了极低的 VGS(th)(高温下常跌破 2V ),将导致下管误导通,进而引发最凶险的桥臂直通短路(Type I HSF) 。

即使驱动器提供了如 -5V 的负偏置电压(由于 NBTI 负偏置温度不稳定性效应的限制,一般不建议超过 -5V ),在极端的工业现场依然不足以绝对免疫米勒效应。因此,现代驱动板集成了有源米勒钳位(Active Miller Clamp, AMC)功能。当检测到关断后的栅极电压低于 2V 时,驱动器内部的钳位开关自动闭合,为位移电流提供一条近乎零阻抗的旁路直通负电源轨 。这不仅强化了常规开关状态下的抗扰度,更是配合软关断机制,在复杂的短路瞬态中将功率器件死死“钉牢”在安全区间。双脉冲测试表明,引入 AMC 后,寄生电压尖峰可从危险的 2.8V 被彻底抹平至 0V,全面杜绝了二次短路的爆发 。

8. 系统级仿真验证与全景应用效能分析

经过精密的底层物理防护武装后,SiC MOSFET 展现出了惊人的宏观系统级效能跨越。无论是用于下一代智慧电网的固态变压器(SST)、储能系统(PCS)、还是有源电力滤波器(APF),大功率 SiC 模块均呈现出对传统硅基 IGBT 的降维打击 。

通过 PLECS 电力电子仿真分析可以量化这种压倒性的优势。在典型的电机驱动系统应用中(仿真条件:800V 母线电压,300A 均方根相电流,80℃ 散热器背板温度),采用 1200V/540A 级别的 BASiC BMF540R12KA3 模块,以 12 kHz 的载波频率运行,其单开关总损耗仅为 242.66 W,系统整体输出效率高达 99.39% 。 相比之下,若采用相同电压等级的传统 FF800R12KE7 IGBT 模块,即便将其载波频率被迫腰斩至 6 kHz,其庞大的开关损耗与拖尾电流依然导致单管总损耗飙升至 1119.71 W,总体效率跌至 97.25% 。两者巨大的发热差距(相差数倍)意味着,在具有完善分级 Desat 与多级软关断护航的前提下,采用 SiC 技术的系统不仅体积更小、被动散热组件成本大幅缩减,而且能够在前所未有的高频(20 kHz 甚至 100 kHz)区间进行大功率电能变换 。

在 Buck 降压拓扑仿真中(输入 800V,输出 300V/350A),BMF540R12MZA3 在 20 kHz 频率下的模块总损耗仅为 955 W(结温 141.9℃),效率仍维持在 99.09% 。而对应规格的 Infineon 或 Fuji 的硅基 IGBT 在区区 2.5 kHz 频率下,发热损耗就已逼近 SiC 20kHz 时的水平 。这一仿真数据有力地证明:只要能在 1 μs 的生死时速内驾驭好短路保护的难题,SiC MOSFET 必将释放出无可比拟的能源转化红利。

9. 研究结语与前瞻

综上所述,大功率碳化硅(SiC)MOSFET 正在重塑全球电力电子系统的效率与体积版图,但其本征的低热容与极短的微秒级短路耐受时间,彻底颠覆了传统的保护系统设计哲学。

本报告的深度解析表明: 第一,保护系统的设计必须建立在对故障物理特性的精准分类之上。硬开关短路(HSF)带来的极致大电流与高 dv/dt 耦合,与负载软短路(FUL)呈现的隐蔽性退饱和慢速爬升,要求检测机制不能“一刀切”。 第二,分级退饱和保护(Graded Desat)通过“低阈值长延迟”捕捉软短路的隐性热累积,依靠“高阈值极短延迟”跨越硬短路的开关噪声并实施 1 μs 级极速切断,完美化解了传统保护在响应速度与抗干扰能力之间的悖论。 第三,面对极速切断故障必然引发的 L⋅di/dt 雪崩过压危机,具有限流效果的两级降压(Multi-Level Turn-Off)以及大阻抗软关断(Soft Shut Down)策略,配合 Si3N4 AMB 封装的极致低杂散电感控制,构筑了化解过电压的物理与逻辑闭环。

展望未来,随着基于数字状态机与边缘计算的自适应驱动器(如集成了高级隔离与智能状态反馈的集成驱动方案)的发展,叠加 Rogowski 线圈或 dv/dt 积分算法等多维监测手段的融合 ,SiC MOSFET 的短路保护将朝着完全软件定义与智能自纠错的维度持续进化,为高压大功率能源转换提供更具韧性的数字硬件屏障。

审核编辑 黄宇

-

MOSFET

+关注

关注

151文章

10801浏览量

234881 -

碳化硅

+关注

关注

26文章

3541浏览量

52655

发布评论请先 登录

碳化硅(SiC)模块短路保护与多级自适应去饱和(DESAT)技术研究

SiC碳化硅MOSFET短路保护中两级关断(2LTO)机制的决定性地位

碳化硅 (SiC) MOSFET 分立器件与功率模块规格书深度解析与应用指南

倾佳电子碳化硅SiC MOSFET驱动特性与保护机制深度研究报告

基本股份SiC功率模块的两电平全碳化硅混合逆变器解决方案

基于SiC碳化硅功率模块的高效、高可靠PCS解决方案

国产SiC碳化硅功率模块全面取代进口IGBT模块的必然性

基于国产碳化硅SiC MOSFET的高效热泵与商用空调系统解决方案

碳化硅(SiC) MOSFET模块的分级退饱和(Desat)保护、软硬短路区分

碳化硅(SiC) MOSFET模块的分级退饱和(Desat)保护、软硬短路区分

评论