倾佳电子碳化硅 (SiC) MOSFET 分立器件与功率模块规格书深度解析与应用指南

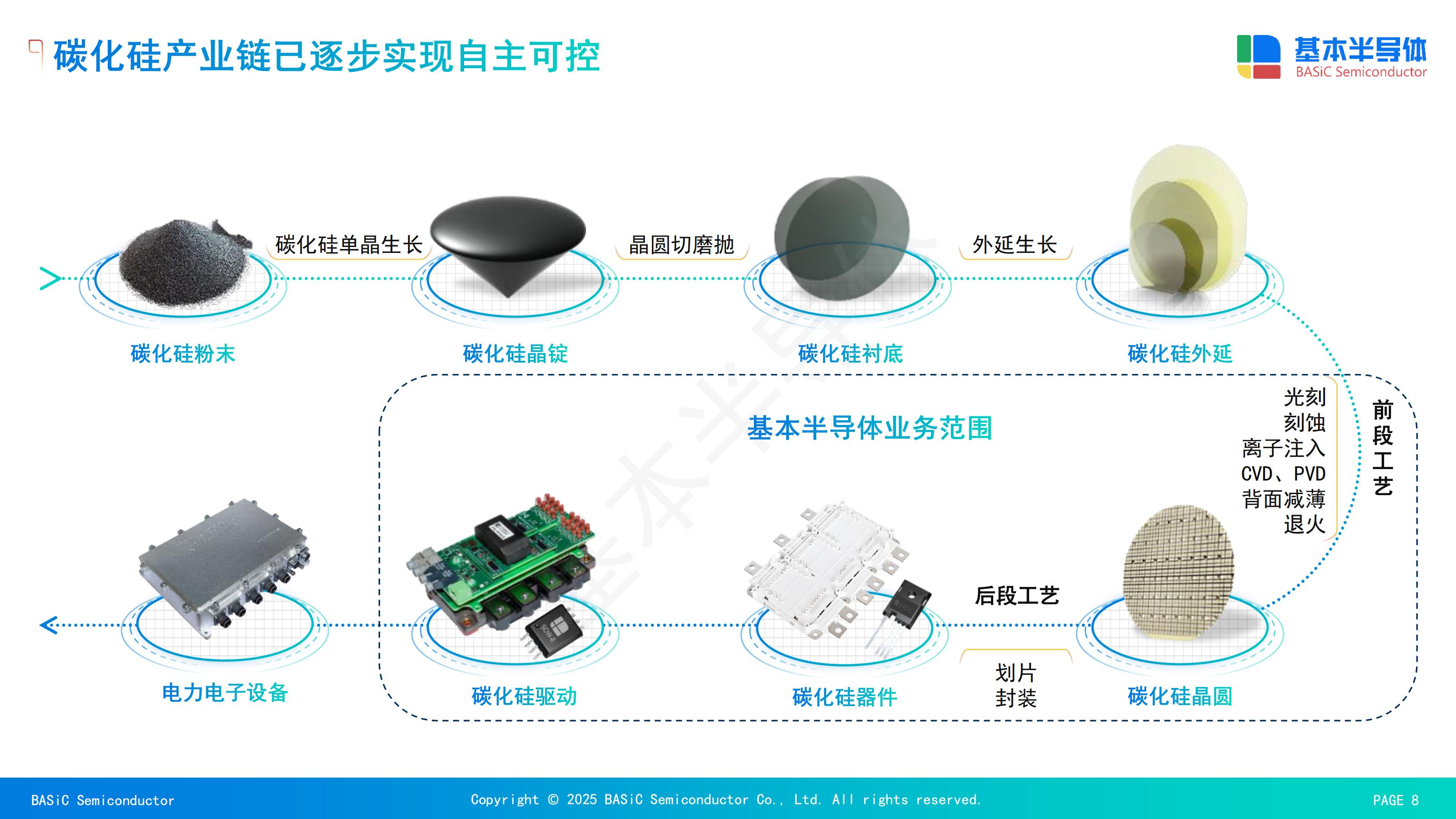

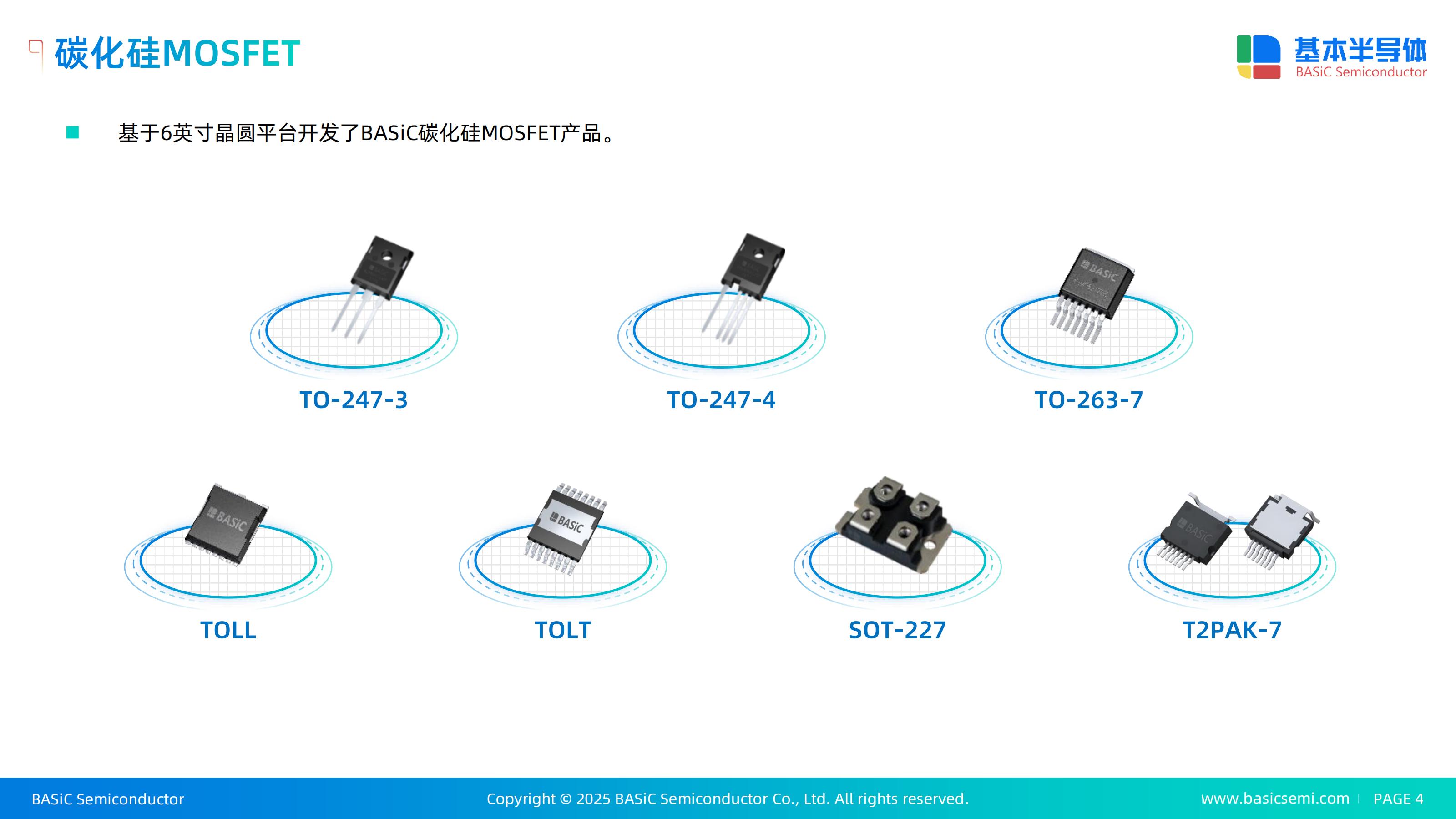

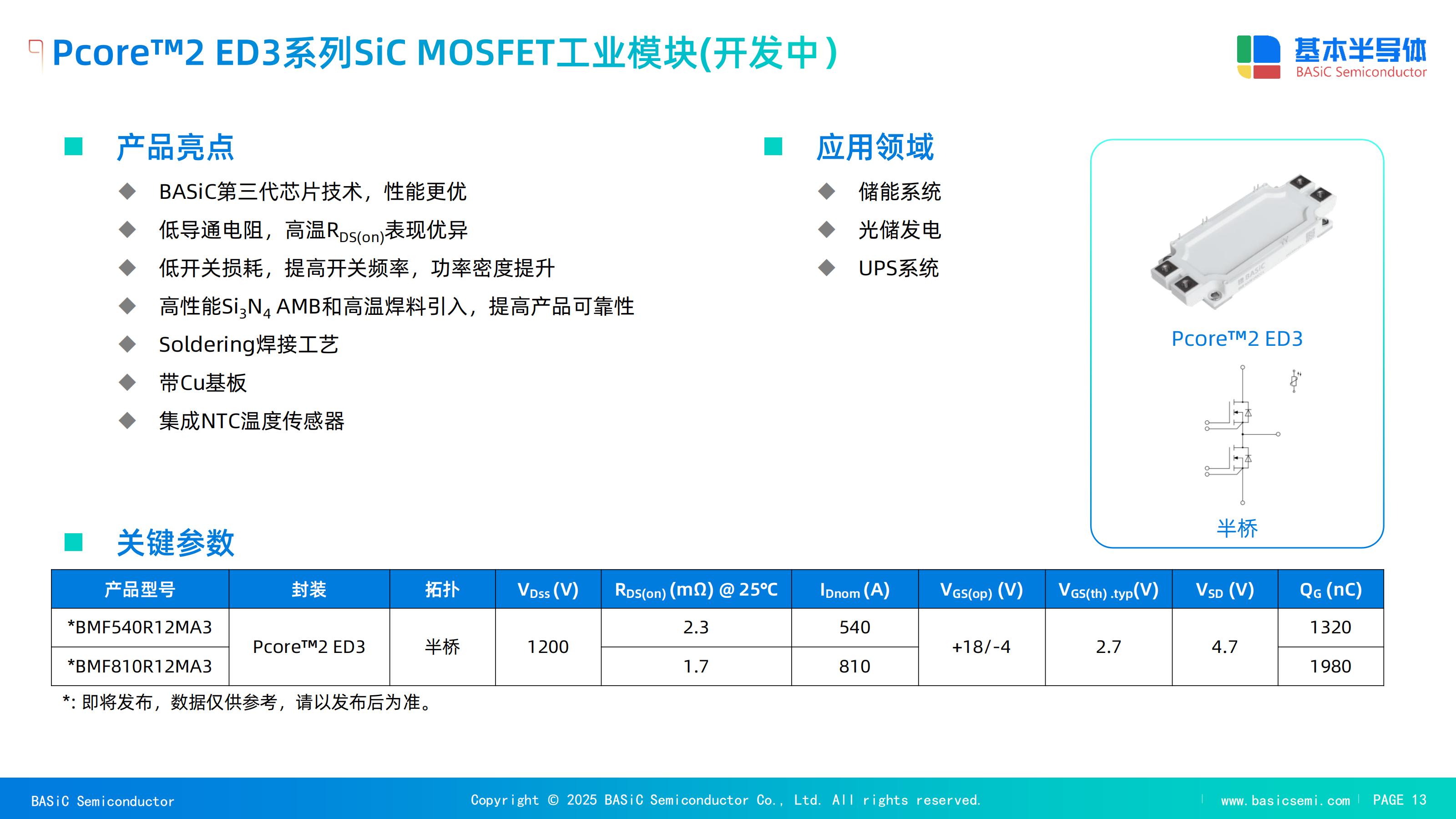

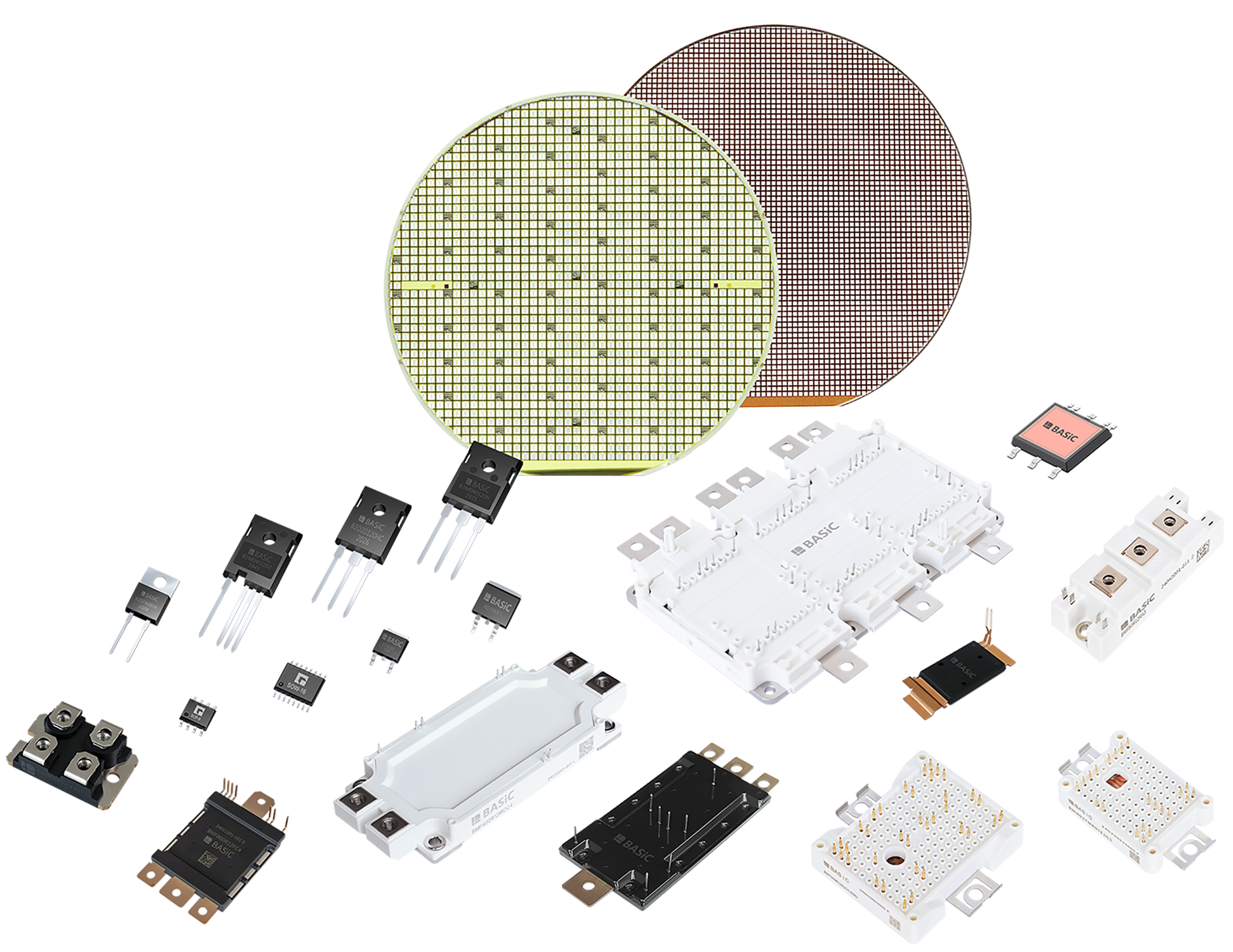

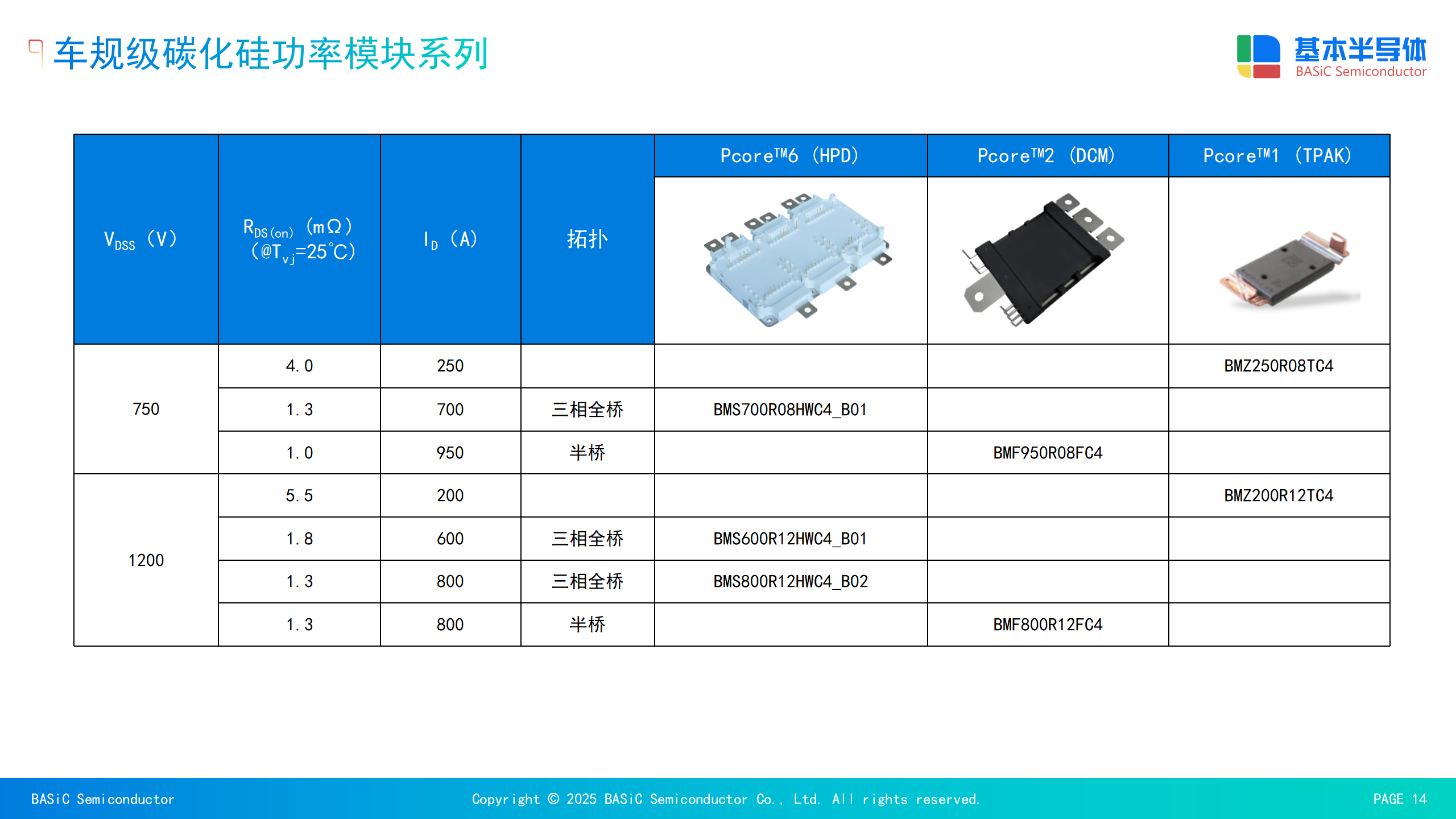

倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,分销代理BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

摘要

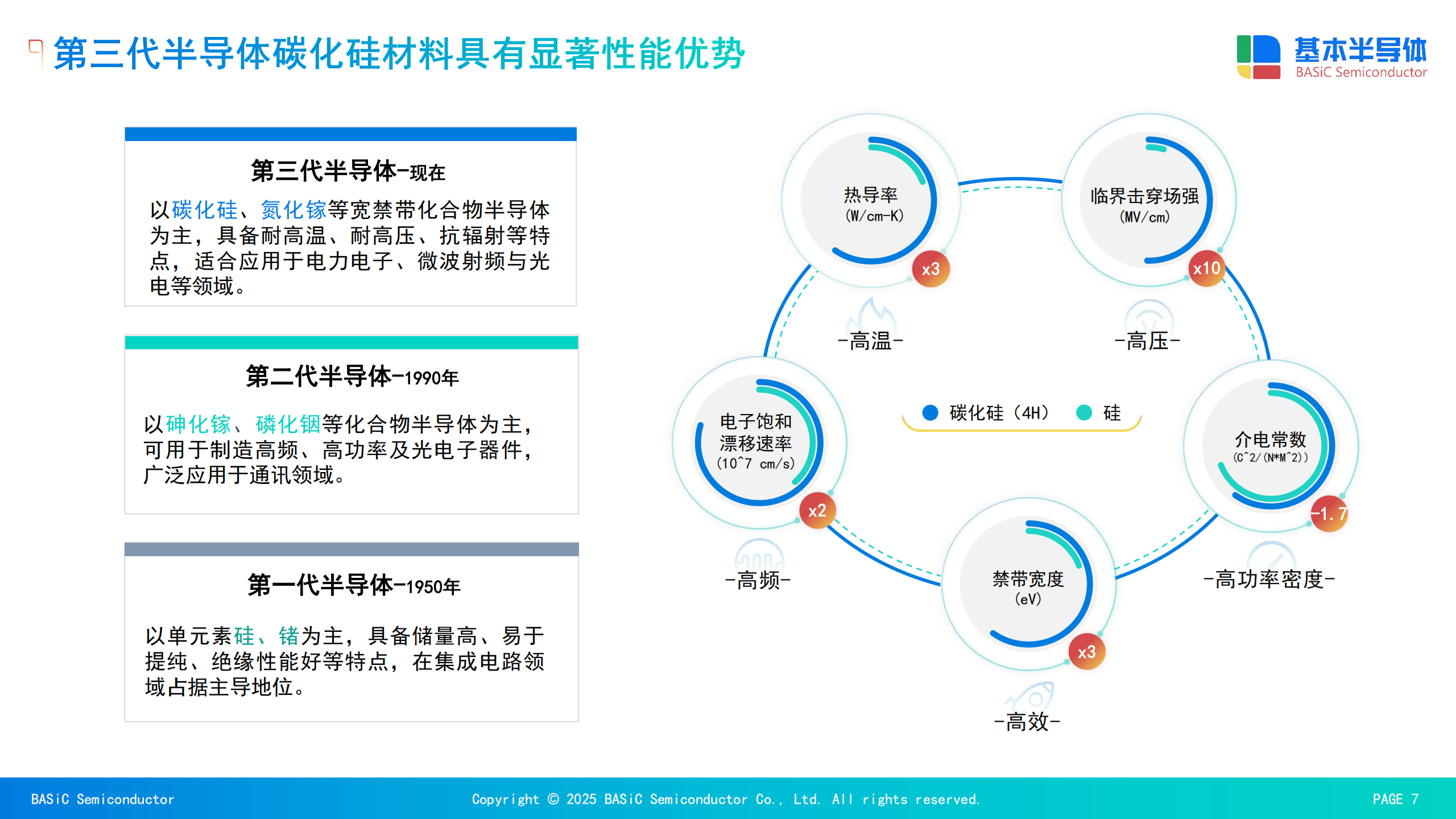

随着宽禁带半导体技术的飞速发展,碳化硅(SiC)MOSFET 已成为高频、高压、高功率密度电力电子转换器的核心器件。与传统的硅基(Si)IGBT 和 MOSFET 相比,SiC 器件凭借其宽禁带(3.26 eV)、高临界击穿场强(比 Si 高 10 倍)和高热导率等固有物理优势,能够显著降低开关损耗并提升系统效率 1。然而,这些物理特性的改变也使得 SiC MOSFET 的规格书参数呈现出与硅器件截然不同的特征。工程师若仅沿用硅器件的经验解读 SiC 规格书,极易在栅极驱动设计、热管理及短路保护等方面产生误判,进而影响系统的可靠性。

倾佳电子旨在为电力电子工程师提供一份详尽的 SiC MOSFET 规格书解读指南。倾佳电子将涵盖从单管到功率模块的全系列参数,深入剖析绝对最大额定值、静态电气特性、动态开关特性、热阻抗特性及可靠性指标。特别针对 SiC 特有的参数——如不对称栅极电压额定值、体二极管的双极性退化效应、开尔文源极(Kelvin Source)的影响、以及短路耐受时间(tSC)的限制——进行重点阐述,并结合实际应用场景探讨参数间的制约关系与设计权衡。

1. 绝对最大额定值(Absolute Maximum Ratings):安全边界的物理诠释

绝对最大额定值定义了器件能够承受的应力极限。超过这些限制,即便是一瞬间,也可能导致器件的永久性损坏或性能的不可逆退化。对于 SiC MOSFET 而言,其额定值的设定逻辑与失效机理与硅器件存在显著差异。

1.1 漏源极电压 (VDSS) 与击穿机理

VDSS 代表了器件在关断状态下(VGS=0V)漏极与源极之间所能承受的最大电压。虽然 SiC 材料具有极高的临界击穿场强,允许在更薄的漂移层上实现高耐压(如 650V, 1200V, 1700V, 3300V),但设计者必须清醒地认识到,VDSS 是一个绝对上限,而非工作电压 。

在实际的高频开关应用中,电路中的寄生电感(Lσ)与极高的电流变化率(di/dt)相互作用,会在关断瞬间产生电压尖峰(Vspike=VDC+Lσ×di/dt)。SiC MOSFET 的开关速度远快于 Si IGBT,这意味着在同样的杂散电感下,SiC 会产生更高的电压过冲。因此,设计者必须预留充足的电压裕量,通常建议工作母线电压不超过 VDSS 的 80% 。若电压尖峰超过 VDSS,器件将进入雪崩击穿模式,虽然 SiC 具备一定的雪崩耐受能力,但这并非正常工作状态。

1.2 栅源极电压 (VGSS) 的不对称性与氧化层可靠性

与硅 MOSFET 通常具有对称的栅极耐压(如 ±20V)不同,SiC MOSFET 的栅极氧化层界面特性决定了其额定电压往往是不对称的,常见的额定值−5V/+18V 。这种不对称性源于 SiC 与 SiO2 界面处较高的缺陷密度以及 SiC 侧较高的电场强度。

正向偏置 (+VGSS):为了获得最低的导通电阻 (RDS(on)),SiC MOSFET 通常推荐在接近最大额定值的电压下驱动(如 +18V )。然而,长期承受过高的正向栅压会加速经时介质击穿(TDDB),缩短器件寿命。因此,规格书中通常会区分“推荐工作电压”(Recommended Operating Voltage)和“绝对最大电压”。例如,某器件可能允许瞬态达到 +22V,但推荐工作电压严格限制在 +18V 。

负向偏置 (−VGSS):由于 SiC MOSFET 的阈值电压 (VGS(th)) 较低且随温度升高而降低,为了防止在关断过程中因米勒效应(dV/dt 耦合)导致的误导通,通常必须施加负偏置电压 -5V。VGSS 的负向极限限制了设计者可使用的负压幅度。如果负压过大,不仅可能导致栅极氧化层损伤,还可能引起阈值电压的漂移(Vth Hysteresis),这是 SiC 特有的界面陷阱效应导致的 。

1.3 漏极电流 (ID) 与 脉冲电流 (IDM)

规格书中的连续漏极电流 ID 通常是一个基于热阻计算出来的理论值,而非实测值。它表示在特定的壳温(TC,通常为 25∘C 或 100∘C)下,器件结温达到最大允许值(Tj,max)时所能流过的电流。

ID=RDS(on)×RthJCTj,max−TC

然而,在实际的大功率模块或分立器件中,电流能力往往受到封装限制(Package Limit),例如键合线的熔断电流或端子的载流能力。仔细阅读规格书会发现,某些器件的计算电流可能高达 100A,但受限于 TO-247 封装引脚,实际标注的 ID 被限制在 75A 左右 。

脉冲漏极电流 IDM 则定义了器件在极短时间内(通常为微秒级)承受大电流的能力,这通常受限于器件的瞬态热阻抗 (ZthJC) 和安全工作区 (SOA)。对于 SiC MOSFET,IDM 通常是连续电流的 2 到 4 倍 。

1.4 功率耗散 (Ptot) 的误区

Ptot 是指当壳温恒定在 25∘C 时,器件内部能够耗散的最大热功率。这是一个理想化的参数,因为在实际应用中,散热器极其难以将壳温维持在室温。该参数主要用于比较不同器件的热性能优劣,而非设计依据。实际允许的功耗必须根据实际的散热条件(RthCA)和环境温度进行降额计算 。

1.5 结温 (Tj) 与存储温度 (Tstg)

SiC 材料本身的固有本征温度极高(超过 600∘C),但商业化 SiC MOSFET 的最高结温 (Tj,max) 通常限制在 150∘C 或 175∘C。这一限制并非来自芯片本身,而是受限于封装材料(如环氧树脂、焊料层、键合线)的耐温能力 。随着封装技术的进步(如银烧结技术的应用),部分先进模块的 Tj,max 正逐步提升至 200∘C,这将显著提升器件的功率密度。

2. 模块级特性与机械参数(Module Characteristics)

对于 SiC 功率模块(如 62mm 封装或 EasyPACK 封装),除了芯片本身的参数外,模块的封装特性对系统设计至关重要。

2.1 绝缘电压 (Visol)

绝缘电压是指模块的功率端子与底板(散热器)之间能够承受的电压有效值(RMS),通常测试时间为 1 分钟。常见的等级有 2500V、3000V 甚至 4000V 。这一参数直接决定了系统是否符合特定的安规标准(如 UL1557)。在高压应用中,高 Visol 等级是确保操作人员安全和防止系统对地击穿的关键。

2.2 杂散电感 (Lσ 或 LsCE)

在 SiC 模块规格书中,杂散电感是一个极其关键的参数。由于 SiC MOSFET 的开关速度极快(di/dt 可达数 kA/μs),即便是极小的杂散电感也会产生巨大的电压过冲。

Vovershoot=Lσ×dtdi

传统 IGBT 模块的杂散电感可能在 20nH 到 50nH 之间,而为了适配 SiC 的高速特性,新型低电感模块设计通常将 Lσ 控制在 10nH 甚至更低 10。在 BMF540R12KA3 等模块的规格书中,杂散电感可能作为开关特性测试条件的一部分给出(如 Lσ=30nH),这提示了测试环境的限制,也暗示了实际应用中母排设计必须追求极低电感 。

2.3 模块引线电阻 (RCC′+EE′)

这是一个经常被忽视但对高电流模块至关重要的参数。它代表了从模块外部端子到芯片表面的连接电阻(包括端子、键合线、覆铜板走线等)。在几百安培的大电流下,即便 0.5 mΩ 的引线电阻也会产生数十瓦的额外损耗(Ploss=I2×R)。

热计算修正:规格书中的 VDS(on) 或 VCE(sat) 有时是在芯片级(Chip level)定义的,有时是在端子级(Terminal level)定义的。若是前者,计算总损耗时必须加上引线电阻产生的压降;若是后者,则已包含。明确这一点对于精确的热仿真至关重要 。

2.4 相比漏电起痕指数 (CTI)

CTI(Comparative Tracking Index)衡量了封装绝缘材料在受污染环境下抵抗表面漏电起痕(Tracking)的能力。CTI 值越高(如 >400 或 >600),意味着材料绝缘性能越好,在 PCB 设计或模块布局时可以允许更小的爬电距离(Creepage Distance),从而有助于提高系统的功率密度 。SiC 模块通常采用高 CTI 值的材料以适应高压紧凑型设计。

2.5 安装扭矩 (Mounting Torque)

对于依靠螺栓固定的模块,规格书会严格规定安装扭矩(如 2.5 - 5 N.m)。

过小:导致接触热阻(RthCS)过大,热量无法有效传导至散热器,导致过热失效。

过大:可能导致陶瓷基板(DBC/AMB)破裂,破坏绝缘性能,甚至直接压碎芯片。

专业的装配工艺要求分步拧紧,并严格控制导热硅脂的厚度。

3. 静态电气特性(Static Characteristics):导通与阻断的细节

静态特性描述了器件在稳态导通或关断时的行为,主要影响导通损耗和静态功耗。

3.1 导通电阻 (RDS(on)) 的复杂依赖性

RDS(on) 是 SiC MOSFET 最核心的参数,直接决定了导通损耗。与硅器件不同,SiC MOSFET 的 RDS(on) 表现出独特的特性:

栅极电压依赖性:SiC MOSFET 的跨导较低,这意味着其通道并没有在阈值电压后迅速完全开启。从 +15V 增加到 +18V 或 +20V,其 RDS(on) 仍会有显著下降 。因此,为了获得最佳效率,推荐使用规格书建议的较高栅压(如 +18V)进行驱动。

正温度系数 (PTC):幸运的是,SiC MOSFET 的 RDS(on) 随温度升高而增加。例如,从 25∘C 到 175∘C,电阻值通常增加 1.4 到 1.6 倍 20。这种 PTC 特性有利于多管并联时的均流,防止热失控。相比之下,硅 CoolMOS 的电阻随温度变化率更大(可达 2.5 倍),这意味着 SiC 在高温下的导通性能衰减更小,实际高温运行时的效率优势比室温下看起来更大。

3.2 阈值电压 (VGS(th)) 与漂移

VGS(th) 定义为漏极电流开始流动的栅极电压。SiC MOSFET 的 VGS(th) 具有以下关键特征:

负温度系数:随温度升高,VGS(th) 会显著降低。一个室温下阈值为 2.7V 的器件,在 175∘C 时可能降至 1.9V 甚至更低 。这极大地增加了高温下因噪声或米勒效应导致误导通(Parasitic Turn-on)的风险,因此在关断时施加负偏置电压(如 -5V)几乎是强制性的 。

漂移现象:由于栅氧界面的缺陷,长时间的正向或负向偏置应力(PBTI/NBTI)会导致 VGS(th) 发生漂移。现代 SiC 工艺已通过筛选和工艺优化控制了这一问题,但设计者仍需关注规格书中的 VGS(th) 最小值范围 。

3.3 漏电流 (IDSS)

虽然 SiC 是宽禁带材料,理论漏电流极低,但实际器件的 IDSS 仍受表面漏电和封装影响。规格书通常给出 25∘C 和高温下的漏电流值。值得注意的是,SiC 的高温漏电流依然非常小,这使得它非常适合高压阻断应用,且不会因漏电流引起显著的热失控风险。

4. 动态电气特性(Dynamic Characteristics):开关行为的物理本质

SiC MOSFET 的优势在于“快”。要理解其开关行为,必须深入解读电容、电荷和内部电阻参数。

4.1 寄生电容 (Ciss,Coss,Crss) 的非线性

MOSFET 的三个寄生电容随漏源电压 (VDS) 的变化呈现高度非线性。

Ciss(输入电容,CGS+CGD):决定了栅极驱动所需的瞬态电流。虽然 SiC 的 Ciss 通常小于同规格的 Si IGBT,但由于驱动电压摆幅大(如 -5V 到 +18V,共 23V 摆幅),驱动功率需求并不低 。

Coss(输出电容,CDS+CGD):在硬开关中,Coss 储存的能量 (Eoss) 会在每次开通时被耗散在通道内,转化为热量。在软开关(如 LLC、ZVS)应用中,Coss 决定了实现零电压开通所需的死区时间和励磁电流。

Crss(反向传输电容/米勒电容,CGD):这是决定开关速度和抗干扰能力的核心参数。SiC MOSFET 的 Crss 通常极小,这允许极快的电压转换速率 (dV/dt)。然而,Crss/Ciss 的比率决定了器件对米勒效应的敏感度。如果该比率过大,漏极电压的快速跳变会通过 Crss 耦合到栅极,导致栅压抬升并引起误导通。

4.2 等效输出电容 (Co(er) 与 Co(tr))

由于 Coss 随电压变化剧烈(在低压时极大,高压时极小),为了方便计算,规格书引入了两个等效线性电容参数 :

Co(er) (能量等效电容):该固定电容值在充电到规定电压(如 800V)时,所储存的能量与实际非线性 Coss 储存的能量 (Eoss) 相同。

Eoss=∫0VDCv⋅Coss(v)dv=21Co(er)⋅VDC2

用途:用于计算硬开关拓扑中的开关损耗。

Co(tr) (时间等效电容):该固定电容值在恒流充电到规定电压时,所需的时间与实际 Coss 相同。

用途:用于计算软开关拓扑中的死区时间(Dead-time)或 dV/dt 转换时间。

关键洞察:Co(er) 和 Co(tr) 数值可能相差很大。混用会导致损耗估算或时序设计的严重偏差。

4.3 栅极电荷 (Qg) 与米勒平台

Qg 曲线描述了驱动器必须提供的电荷量。曲线中的平坦区域被称为“米勒平台”。在此阶段,栅极电流全部用于给 Crss 充电,以支持漏极电压的快速变化 (dVDS/dt),栅压保持不变。SiC MOSFET 的米勒平台电压通常较高(约 6V-10V),且平台宽度较窄,意味着其开关过程极快 。

4.4 内部栅极电阻 (RG(int))

这是芯片内部栅极流道的物理电阻。与硅器件不同,SiC MOSFET 的 RG(int) 在某些设计中可能受频率影响 。

影响:RG(int) 与外部栅极电阻 (RG(ext)) 串联,共同决定了开关速度。如果 RG(int) 过大,即使外部电阻设为零,开关速度也会受限。

振荡阻尼:适当的 RG(int) 有助于抑制栅极振荡,但过大会增加开关损耗。在计算驱动电流峰值时,必须包含此电阻:Ig,peak=ΔVGS/(RG(ext)+RG(int)+Rdriver)。

4.5 开关时间与能量 (ton/off,Eon/off)

规格书中的开关时间(td(on),tr,td(off),tf)和损耗能量(Eon,Eoff)是在特定测试条件下测得的(通常是双脉冲测试,感性负载)。

Eon的构成:包含了 MOSFET 通道的开通损耗以及续流二极管的反向恢复损耗 (Err)。如果是带有集成 SBD 的 SiC MOSFET,其 Eon 会显著降低 。

Eoff的特性:SiC MOSFET 没有 IGBT 的拖尾电流(Tail Current),因此关断极快,主要受限于 dV/dt 和杂散电感。

损耗估算公式:在实际应用中,电压和电流往往与测试条件不同。可以使用修正系数进行估算 :

Esw(Iapp,Vapp)≈Esw(datasheet)×(VtestVapp)Kv×(ItestIapp)Ki

其中 Kv 通常接近 1.2-1.4(考虑电容非线性),Ki 接近 1(线性关系)。

5. 第三象限特性与体二极管(Reverse Diode Characteristics)

SiC MOSFET 在桥式电路中需要处理反向续流。其特性由体二极管或同步整流模式决定。

5.1 体二极管的正向压降 (VSD)

SiC MOSFET 的本征体二极管是 PN 结结构。由于 SiC 的禁带宽度大,其开启电压(Knee Voltage)很高,通常在 3V 到 4V 以上 。

功耗陷阱:如果在死区时间内长时间让体二极管导通,巨大的 VSD 会导致严重的导通损耗。

同步整流 (Synchronous Rectification):为了避免上述损耗,必须在二极管导通后迅速开启 MOSFET 沟道(VGS>Vth)。此时电流流经沟道,表现为电阻特性(V=I×RDS(on)),压降可大幅降低至 1V 以下。规格书中的“第三象限特性曲线”通常会展示 VGS=−5V(二极管模式)和 VGS=18V(同步整流模式)两条曲线,两条曲线的交点提示了在极大电流下二极管模式可能反而压降更低,但在正常工作范围内,同步整流优势明显 。

5.2 反向恢复特性 (Qrr,trr)

虽然 SiC 体二极管是 PN 结,但由于载流子寿命极短,其反向恢复电荷 (Qrr) 远小于同电压等级的硅快恢复二极管。

温度独立性:硅二极管的 Qrr 随温度升高而急剧增加,而 SiC 二极管的 Qrr 对温度几乎不敏感 。这使得 SiC 转换器在高温下仍能保持极低的开关损耗和电磁干扰 (EMI)。

6. 热阻抗特性与瞬态热响应

6.1 热阻 (RthJC) 与 瞬态热阻抗 (ZthJC)

RthJC:描述了稳态下的散热能力。

ZthJC曲线:描述了器件对短脉冲功率的热响应。对于毫秒级甚至微秒级的过载脉冲,热量还没来得及传导到散热器,主要由芯片本身的热容吸收。ZthJC 曲线允许工程师计算在脉冲负载下的瞬时结温升 。

应用:在电机启动堵转或短路保护设计中,必须使用 ZthJC 而非 RthJC 来评估芯片是否会过热烧毁。

7. 安全工作区 (SOA) 与鲁棒性

7.1 正向偏置安全工作区 (FBSOA)

FBSOA 定义了器件在导通状态下允许的电压和电流范围。

线性模式限制:与硅 MOSFET 不同,SiC MOSFET 的 FBSOA 曲线在“线性模式区”(高电压、大电流同时存在)往往受到更严格的限制,或者甚至不建议在此区域工作 。这是因为 SiC 芯片面积小,功率密度极高,且在某些条件下可能出现类似 Spirito 效应的热不稳定性(局部热点导致电流集中)。

应用警示:SiC MOSFET 不适合用作线性稳压器或电子负载。它们是为开关应用而优化的。

7.2 反向偏置安全工作区 (RBSOA)

RBSOA 定义了关断过程中的安全轨迹。通常为矩形区域,即在关断瞬间,电压不超过 VDSS,电流不超过 IDM 。SiC MOSFET 必须在此范围内硬关断,且需严格控制关断电压尖峰。

7.3 短路耐受时间 (tSC)

这是 SiC MOSFET 的一个短板。由于芯片面积小、热容量小,SiC MOSFET 承受短路电流的时间显著短于 IGBT。

典型值:IGBT 通常为 10μs,而 SiC MOSFET 通常仅为 2μs 到 3μs 。

保护要求:这对门极驱动器的去饱和检测(Desat)或电流保护电路提出了极高的响应速度要求。标准 IGBT 驱动器可能太慢,无法保护 SiC 器件。

7.4 雪崩能量 (EAS)

虽然 SiC 具有 Avalanche Ruggedness,但由于沟槽栅(Trench)结构的电场集中效应和较小的芯片体积,其标称的 EAS 值可能看似不高。但关键在于其在规定能量下的耐受力是可靠的。设计时应尽量避免让 SiC 器件频繁进入雪崩状态,通常建议通过钳位电路吸收感性关断能量 。

7.5 dV/dt 耐受力

SiC MOSFET 能够承受极高的电压变化率(如 >100 V/ns)。

风险:过高的 dV/dt 即使不击穿器件,也可能通过寄生电容耦合导致低压侧电路故障,或触发器件内部寄生 BJT 的闩锁效应(Latch-up)。不过现代 SiC 器件通常对 dV/dt 具有很高的免疫力,规格书常标注 >50 V/ns 或更高 。

8. 封装对性能的影响:开尔文源极 (Kelvin Source)

在阅读规格书时,封装引脚配置是一个极易被忽视但至关重要的细节。

8.1 传统 3 引脚封装的局限

在 TO-247-3 等传统封装中,源极引脚同时承载驱动回路的参考地和功率回路的主电流。功率回路的巨大电流变化 (di/dt) 会在源极引线的寄生电感 (LS) 上产生感应电压 (V=LS×di/dt)。这个电压会负反馈到栅极驱动回路,减缓开启速度,增加开关损耗。

8.2 4 引脚开尔文源极封装 (TO-247-4)

新型 SiC 分立器件常采用 4 引脚封装,增加了一个开尔文源极引脚 (Driver Source / Kelvin Source)。

原理:该引脚专门用于连接栅极驱动器的回路参考地,不流过功率电流。因此,功率回路的 di/dt 不会影响驱动电压。

优势:这消除了源极电感的负反馈效应,使得 SiC MOSFET 能够以更快的速度开关,通常可降低 30%-50% 的开关损耗 (Eon) 。

解读:在对比不同器件规格书时,若一个是 3 引脚,一个是 4 引脚,即使芯片参数相同,4 引脚器件在实际应用中的动态性能也会显著优越。

9. 结论:解读 SiC 规格书的系统化思维

深圳市倾佳电子有限公司(简称“倾佳电子”)是聚焦新能源与电力电子变革的核心推动者:

倾佳电子成立于2018年,总部位于深圳福田区,定位于功率半导体与新能源汽车连接器的专业分销商,业务聚焦三大方向:

新能源:覆盖光伏、储能、充电基础设施;

交通电动化:服务新能源汽车三电系统(电控、电池、电机)及高压平台升级;

数字化转型:支持AI算力电源、数据中心等新型电力电子应用。

公司以“推动国产SiC替代进口、加速能源低碳转型”为使命,响应国家“双碳”政策(碳达峰、碳中和),致力于降低电力电子系统能耗。

需求SiC碳化硅MOSFET单管及功率模块,配套驱动板及驱动IC,请添加倾佳电子杨茜微芯(壹叁贰 陆陆陆陆 叁叁壹叁)

解读 SiC MOSFET 规格书不仅仅是比对数字,更是一个理解器件物理限制与应用场景匹配的过程。工程师应遵循以下逻辑:

核对绝对边界:确保 VDSS 留有足够的过冲裕量;严格遵守负向栅压 VGSS 限制以防 Vth 漂移;确认短路保护机制能覆盖 tSC 的极短时间窗口。

评估静态损耗:不要只看 25∘C 的 RDS(on),更要关注 175∘C 下的数值。利用 SiC 的 PTC 特性进行并联设计,但需警惕 ZTC 点以下的负温度系数区域不稳定性 。

精算动态损耗:区分 Eon 是否包含二极管损耗;利用 Co(er) 计算电容损耗;意识到实际开关速度受限于外部 RG 和回路电感 Lσ,规格书中的纳秒级速度仅在理想测试条件下实现。

重视封装特性:在高频应用中,优先选择带开尔文源极的封装或低电感模块(Lσ<15nH),并关注模块的 RthJC 和 Visol 等级。

热设计验证:利用 ZthJC 曲线校核最恶劣工况(如堵转、浪涌)下的瞬态结温,确保不超过 Tj,max。

通过全面、深入地理解这些参数及其背后的物理意义,设计者才能真正释放碳化硅功率器件的潜能,构建出高效、可靠且具有竞争力的电力电子系统。

审核编辑 黄宇

-

MOSFET

+关注

关注

150文章

9462浏览量

229954 -

分立器件

+关注

关注

5文章

252浏览量

22230 -

功率模块

+关注

关注

11文章

612浏览量

46663

发布评论请先 登录

双脉冲测试技术解析报告:国产碳化硅(SiC)功率模块替代进口IGBT模块的验证与性能评估

倾佳电子碳化硅SiC MOSFET驱动特性与保护机制深度研究报告

倾佳代理的基本半导体碳化硅MOSFET分立器件产品力及应用深度分析

基本股份SiC功率模块的两电平全碳化硅混合逆变器解决方案

全球功率半导体变革:SiC碳化硅功率器件中国龙崛起

BASiC基本股份国产SiC碳化硅MOSFET产品线概述

碳化硅 (SiC) MOSFET 分立器件与功率模块规格书深度解析与应用指南

碳化硅 (SiC) MOSFET 分立器件与功率模块规格书深度解析与应用指南

评论