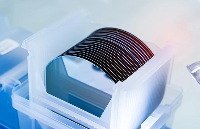

4月17日,长电科技宣布成功完成基于玻璃通孔(TGV)结构与光敏聚酰亚胺(PSPI)再布线(RDL)工艺的晶圆级射频集成无源器件(IPD)工艺验证,通过测试结构的试制与实测评估,公司验证了在玻璃基底上构建三维集成无源器件的可制造性与性能优势,为5G及面向6G的更宽带宽射频前端与系统级封装优化提供了新的工程化路径。

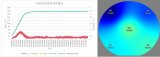

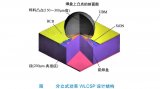

长电科技基于TGV构建3D互连骨架,在玻璃基板上实现电感、电容等关键无源结构的集成,并将传统平面电感升级为3D结构,以降低高频损耗并提升器件品质因数(Q值)。在对比评估中,3D电感在Q值等关键指标上实现显著提升,在既定测试条件下较同等电感值的平面结构提升接近50%。同时,整体性能表现优于硅基IPD技术路线,为射频模组的小型化、高集成度与性能指标提升提供了可行的工程方向。

面向5G及未来6G的通信需求,射频系统对带宽、线性度与集成度提出持续升级要求。长电科技在射频封装领域经过多年深耕,已形成面向射频PA、RFFE模组与毫米波应用的封装与测试能力:支持SiP、AiP等多种封装形态,覆盖共形、分腔及选择性溅射屏蔽,并具备5G、毫米波、NB‑IoT及高速信号测试能力;同时提供射频系统仿真与封装协同设计,并配套覆盖射频微波、毫米波、5G蜂窝与无线通信等的一站式验证测试平台,支撑客户从芯片、封装到模组与整机的验证与导入。

长电科技副总裁、技术服务事业部总经理吴伯平表示:“面向AI算力芯片的迭代跃迁与6G通信的前瞻布局,长电科技将加速推进玻璃基TGV与PSPI晶圆级IPD技术在射频系统级封装中的工程化落地。我们将深化与头部客户及产业链伙伴的协同创新,通过联合开发与验证,推动相关技术走向规模化量产,为下一代边缘计算和无线连接提供更高性能、更高集成度的系统级解决方案。”

长电科技是全球领先的集成电路制造与技术服务提供商,向全球半导体客户提供全方位、一站式芯片成品制造解决方案,涵盖微系统集成、设计仿真、晶圆中测、芯片及器件封装、成品测试、产品认证以及全球直运等服务。公司在中国、韩国和新加坡拥有八大生产基地,并在全球设有20多个业务机构,为客户提供紧密的技术合作与高效的产业链支持。

长电科技拥有先进和全面的芯片成品制造技术,包括晶圆级封装(WLP)、2.5D/3D封装、系统级封装(SiP)、倒装芯片封装、引线键合封装及主流封装先进化解决方案,广泛应用于汽车电子、人工智能、高性能计算、高密度存储、网络通信、智能终端、工业与医疗、功率与能源等领域。

-

射频

+关注

关注

106文章

6101浏览量

173827 -

无源器件

+关注

关注

5文章

239浏览量

24356 -

长电科技

+关注

关注

5文章

403浏览量

33563

原文标题:面向5G、6G需求:长电科技实现玻璃基TGV射频IPD性能突破

文章出处:【微信号:gh_0837f8870e15,微信公众号:长电科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

聊一聊国产射频无源器件的崛起 —— 成都恒利泰十年深耕,适配多场景需求

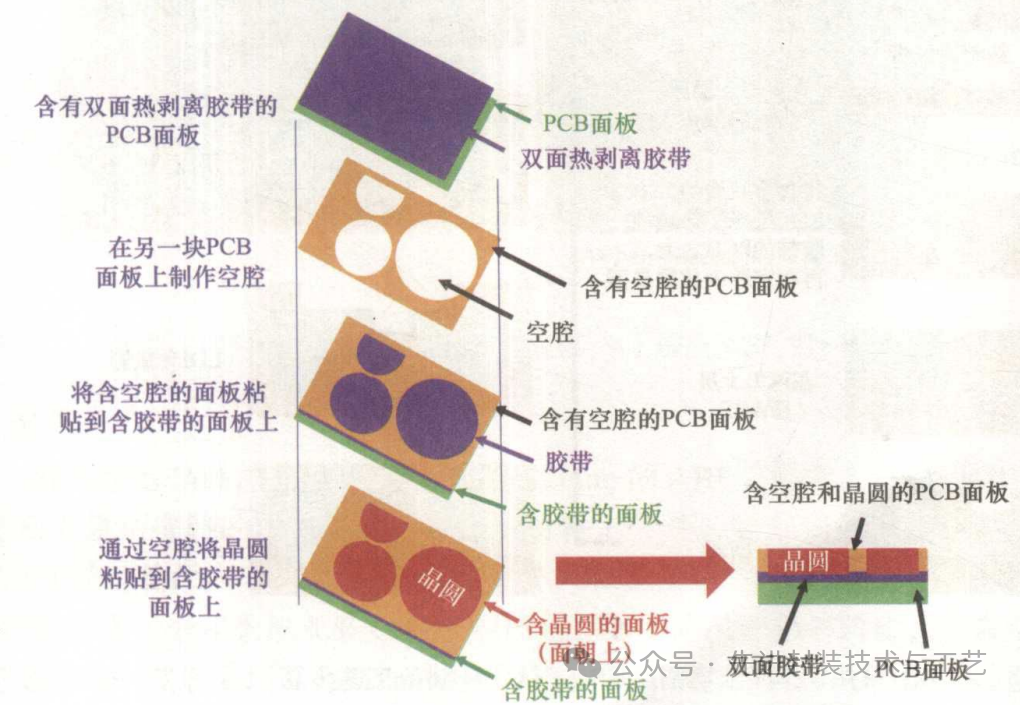

晶圆级扇出型封装的三大核心工艺流程

长电科技成功完成晶圆级射频集成无源器件工艺验证

长电科技成功完成晶圆级射频集成无源器件工艺验证

评论