文章来源:Jeff的芯片世界

原文作者:Jeff的芯片世界

在集成电路制造中,栅极线宽通常被用作技术节点的定义标准,线宽越小,单位面积内可容纳的晶体管数量越多,芯片性能随之提升。

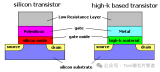

随着工艺尺寸持续缩小至90nm及以下节点,栅极制造面临日益严峻的挑战,其中多晶硅栅极因其独特优势而长期占据主流地位。多晶硅栅极可在高温源/漏扩散工艺中作为掩模实现自对准掺杂,与SiO₂界面工艺兼容且耐高温退火,同时可通过改变掺杂类型有效调节MOSFET的阈值电压。在栅极材料演变历程中,从早期金属栅到多晶硅栅,再到0.35μm时代的WSi加多晶硅,0.25μm后又回归多晶硅栅,直至28nm之后重新启用金属栅。

多晶硅栅刻蚀的主要步骤

多晶硅栅极刻蚀通常包含预刻蚀、主刻蚀和过刻蚀三个步骤。预刻蚀用于去除多晶硅表面的自然氧化膜、硬掩模和污染物,常用含氟气体如CF₄、CHF₃等。主刻蚀负责刻蚀大部分多晶硅膜,要求较高的刻蚀速率,同时对氧化硅的选择比较低。主刻蚀气体以Cl₂、HBr、HCl为主,其中Cl₂与硅反应生成挥发性SiCl₄,HBr生成挥发性SiBr₄。该步骤通常采用终点检测系统来监测底部栅极介质层。当工艺节点达到90nm、65nm时,可在传统气体中加入适量SF₆和NF₃等氟基气体,以防止多晶硅栅极形状畸变和预掺杂负载现象。过刻蚀用于去除刻蚀残留物和剩余多晶硅,要求对底部栅极氧化层具有较高选择比,因此不得使用任何含氟气体,以免损伤栅极氧化层并形成刻蚀微槽。

在多晶硅刻蚀中,HBr/Cl₂是主要的气体组合,其他气体作为添加气体使用。核心反应机理为Si + Cl₂ → SiCl₄。不同气体各有功能:Cl₂为主要刻蚀气体,HBr可提供侧壁钝化作用,HeO₂相当于O₂用于调控对SiO₂的选择比,SF₆和NF₃刻蚀速率极高但均匀性较差且倾向各向同性,含氟碳化合物气体既可提供氟自由基也可产生聚合物沉积,N₂用于调控刻蚀形貌。

关键工艺参数及其控制方法

刻蚀后检测得到的关键参数包括栅线条宽特征尺寸、线条均匀性、密集区与稀疏区刻蚀偏差、线宽粗糙度等,这些参数直接影响器件性能与良率。漏饱和电流正比于器件有效沟道长度,与多晶硅栅的CDU密切相关;而V_min双斜率问题则依赖于TPEB的表现,好的TPEB结构不会产生该问题;LWR与阈值电压变化相关,会明显增大关态电流泄漏。改善AEI CDU的成熟方法之一是进行ADI剂量补偿,即在已知片内AEI CD分布情况下,对ADI CD分布进行补偿,例如在晶圆边缘处增大CD。但这种方法不能解决多晶硅栅极底部形状的负载,且易引入更多疏密负载。

在刻蚀方面,底部抗反射涂层打开步骤是同时改进CDU、TPEB和LWR的关键手段。通过实验设计在偏置电压、腔室压力和晶圆温度中选择最佳条件。晶圆温度对CDU影响非常明显;对于TPEB,高压和低偏置是好的组合,但该条件会使LWR恶化。LWR的改善需关注气体组合,采用HBr基条件进行BARC打开优于Cl₂基,因为HBr基能提供更强的光刻胶侧墙保护。

栅极形状的优化与常见缺陷

多晶硅栅的形状主要取决于主刻蚀步骤,其改善可与CDU、TPEB、LWR无关。主刻蚀和过刻蚀步骤中的偏置电压和工艺时间对栅极形状有显著影响,侧墙角可作为评价指标。主刻蚀时间增加会使侧墙角增大,而主刻蚀偏置电压增高、过刻蚀时间增加或偏置电压增高均会使侧墙角变小。过刻蚀时间增加往往引起颈缩现象恶化。

对于65nm及以下工艺节点,多晶硅栅上任何微小缺口或脚都会改变栅的有效长度,影响器件性能。研究表明,局部刻蚀可能取决于多晶硅薄膜与衬底界面处的应力,优化多晶薄膜的本征应力有可能减小甚至消除多晶硅栅的脚。例如,当本征薄膜应力变为更大的压缩应力时,底部形状会从小脚演变为几乎无小脚,再到小缺口。此外,线边缘收缩可通过底部抗反射涂层打开步骤的优化得到改善,栅刻蚀后出现的硅凹陷可通过过刻蚀步骤调节得到改善。

-

集成电路

+关注

关注

5464文章

12669浏览量

375612 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

刻蚀工艺

+关注

关注

2文章

43浏览量

8838

原文标题:多晶硅栅刻蚀工艺介绍

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

分析MOS管未来发展与面临的挑战

多晶硅栅(Poly-Si Gate)

多晶硅的用途包括哪些

多晶硅栅耗尽效应简述

集成电路制造工艺中的刻蚀技术介绍

集成电路制造中多晶硅栅刻蚀工艺介绍

集成电路制造中多晶硅栅刻蚀工艺介绍

评论