探索Atmel AT17LV系列FPGA配置EEPROM:特性、应用与设计要点

在FPGA(Field Programmable Gate Array,现场可编程门阵列)的应用领域中,配置存储器是不可或缺的一部分。它负责存储FPGA的配置程序,确保FPGA能够按照预设的功能运行。Atmel公司的AT17LV系列FPGA配置EEPROM(Electrically Erasable Programmable Read-Only Memory,电可擦可编程只读存储器)就是这样一类产品,为FPGA提供了便捷、经济的配置解决方案。

文件下载:AT17LV002-10CU.pdf

一、产品概述

AT17LV系列包括AT17LV65、AT17LV128、AT17LV256、AT17LV512、AT17LV010、AT17LV002和AT17LV040等型号。不过需要注意的是,AT17LV65和AT17LV128已不推荐用于新设计,被AT17LV256所替代。这些器件支持3.3V和5.0V的工作电压,适用于多种不同的系统环境。

1. 主要特性

- 存储能力多样:提供了从65,536 x 1-bit到4,194,304 x 1-bit等多种存储容量选择,能够满足不同规模FPGA的配置需求。

- 双电压支持:可在3.3V和5.0V的工作电压下正常工作,增加了产品的通用性和适用性。

- 系统内可编程(ISP):通过2线总线即可实现系统内编程,方便用户在实际应用中进行配置程序的更新。

- 简单接口:与SRAM FPGA具有简单的接口,易于集成到系统中。

- 广泛兼容性:与Atmel的AT6000、AT40K和AT94K设备,以及Altera的FLEX、APEX设备,还有Xilinx的XC3000、XC4000、XC5200、Spartan、Virtex等FPGA器件兼容。

- 可级联回读:支持级联回读功能,能够为额外的配置或更高密度的阵列提供支持。

- 低功耗CMOS EEPROM工艺:采用低功耗的CMOS EEPROM工艺,降低了系统的功耗。

- 可编程复位极性:用户可以在编程时选择复位功能的极性,增加了设计的灵活性。

- 多种封装选择:提供6mm x 6mm x 1mm 8-lead LAP(与8-lead SOIC封装引脚兼容)、8-lead PDIP、8-lead SOIC、20-lead PLCC、20-lead SOIC和44-lead TQFP等多种封装形式,方便不同应用场景的使用。

- 低功耗待机模式:当芯片使能信号(CE)为高电平时,器件进入低功耗待机模式,进一步降低功耗。

- 高可靠性:具有100,000次的写入循环寿命,工业级部件在85°C环境下数据保存时间可达90年。

- 环保封装:提供绿色(无铅/无卤化物/符合RoHS标准)封装选项,符合环保要求。

2. 引脚配置与描述

AT17LV系列器件的引脚功能丰富,不同型号的引脚配置可能会有所差异。下面是一些主要引脚的功能介绍:

- DATA:配置时的三态数据输出,编程时为开漏双向引脚。

- CLK:时钟输入,用于在读写和编程时递增内部地址和位计数器。

- WP1、WP2:写保护引脚,用于在编程时保护部分内存,默认情况下由于内部下拉电阻而禁用,在FPGA加载操作时不使用,WP1仅在AT17LV512/010/002设备上可用,WP2仅在AT17LV512/010上可用。

- RESET/OE:复位(低电平有效)/输出使能(高电平有效),低电平可重置地址和位计数器,高电平(CE为低电平时)使能数据输出驱动器,该输入的逻辑极性可编程。

- WP:写保护输入(CE为低电平时),仅在编程时有效(SER_EN为低电平),低电平时可写入整个内存,高电平时最低内存块不可写入,仅在AT17LV65、AT17LV128和AT17LV256上可用。

- CE:芯片使能输入(低电平有效),低电平(OE为高电平时)允许CLK递增地址计数器并使能数据输出驱动器,高电平则禁用地址和位计数器并使器件进入低功耗待机模式,但在两线串行编程模式下(SER_EN为低电平)该引脚不用于使能/禁用器件。

- CEO:芯片使能输出(低电平有效),当地址计数器达到最大值时输出低电平,在AT17LV器件的级联链中,一个器件的CEO引脚必须连接到下一个器件的CE输入,该功能在AT17LV65上不可用。

- A2:设备选择输入,用于在编程时使能(或选择)设备,具有内部下拉电阻。

- READY:开集电极复位状态指示,上电复位时为低电平,上电完成后释放,使用该引脚时建议使用4.7kΩ上拉电阻。

- SER_EN:串行使能,FPGA加载操作时必须保持高电平,低电平则启用两线串行编程模式,对于非ISP应用,应将其连接到Vcc。

- Vcc:电源引脚,支持3.3V(±10%)和5.0V(±10%)的电源供应。

二、工作模式与应用

1. FPGA主串行模式

基于SRAM的FPGA的I/O和逻辑功能由配置程序确定。在主模式下,FPGA会自动从外部存储器加载配置程序,AT17LV系列串行配置EEPROM就是为此设计的,与主串行模式兼容。

2. 配置控制

FPGA与AT17LV串行EEPROM之间的大多数连接简单明了。AT17LV配置器的DATA输出驱动FPGA的DIN输入,主FPGA的CCLK输出驱动AT17LV配置器的CLK输入,任何AT17LV配置器的CEO输出驱动级联链中下一个配置器的CE输入。此外,SER_EN必须连接到Vcc(ISP期间除外),READY引脚可作为设备复位状态的开集电极指示。

3. 级联配置

对于多个FPGA以菊花链方式配置或需要更大配置内存的FPGA,级联配置器可以提供额外的内存。当第一个配置器的最后一位数据被读取后,其CEO输出变为低电平,禁用其DATA线驱动器,第二个配置器检测到CE输入为低电平后,启用其DATA输出。配置完成后,如果将每个配置器的RESET/OE驱动到其有效(低电平)状态,则所有级联配置器的地址计数器将被重置;如果不需要重置地址计数器,则可将RESET/OE输入连接到其无效(高电平)状态。需要注意的是,AT17LV65设备没有CEO功能,无法进行级联配置。

三、编程与待机模式

1. 编程模式

将SER_EN拉低即可进入编程模式,在该模式下,芯片可以通过2线串行总线进行编程,编程仅在Vcc电源下进行,芯片内部会产生编程超电压。

2. 待机模式

当CE信号为高电平时,AT17LV配置器进入低功耗待机模式。在3.3V电源下,AT17LV65、AT17LV128或AT17LV256配置器的电流消耗小于50μA,AT17LV512/010为100μA,AT17LV002/040为200μA。此时,无论OE输入状态如何,输出都保持高阻态。

四、电气特性

1. 绝对最大额定值

- 工作温度范围:-40°C至+85°C

- 存储温度范围:-65°C至+150°C

- 任何引脚相对于地的电压:-0.1V至Vcc + 0.5V

- 电源电压(Vcc):-0.5V至+7.0V

- 最大焊接温度(10s @ 1/16 in.):260°C

- ESD(RZAP = 1.5K,CZAP = 100pF):2000V

2. 工作条件

在工业温度范围(-40°C至+85°C)内,3.3V供电时,Vcc的范围为3.0V至3.6V;5.0V供电时,Vcc的范围为4.5V至5.5V。

3. 直流特性

不同型号器件在3.3V和5.0V供电时的直流特性略有差异,主要包括高电平输入电压、低电平输入电压、高电平输出电压、低电平输出电压、电源电流(有源模式和待机模式)以及输入/输出泄漏电流等参数。

4. 交流特性

交流特性参数包括OE到数据延迟、CE到数据延迟、CLK到数据延迟、数据保持时间、CE或OE到数据浮空延迟、CLK低电平时间、CLK高电平时间、CE设置时间、CE保持时间、OE高电平时间以及最大时钟频率等,这些参数在不同供电电压和级联情况下会有所不同。

5. 热阻系数

不同封装类型的器件具有不同的热阻系数,包括结到壳热阻(θJC)和结到环境热阻(θJA)。良好的散热设计对于保证器件的正常工作至关重要,工程师们在设计时是否充分考虑到了这些热阻系数对系统稳定性的影响呢?

五、订购信息与封装

1. 订购代码细节

订购代码包含了产品家族、设备密度、封装选项、等级、特殊引脚配置和产品变体等信息,例如“AT17LV256A - 10PU”,用户可以根据自己的需求进行选择。

2. 订购信息

提供了不同存储容量器件的具体订购代码、引脚镀层、封装、电压和工作温度范围等信息,方便用户进行采购。

3. 封装信息

包括8CN4 - LAP、8P3 - PDIP、8S1 - SOIC、20J - PLCC、20S2 - SOIC和44A - TQFP等多种封装形式的详细尺寸和相关说明。在实际应用中,你是否会根据电路板的空间和布局来选择合适的封装呢?

六、总结

Atmel的AT17LV系列FPGA配置EEPROM以其丰富的特性、广泛的兼容性和多样的封装选择,为FPGA的配置提供了可靠的解决方案。工程师们在使用这些器件时,需要根据具体的应用场景和系统要求,合理选择型号和封装,注意引脚的连接和配置,以及关注器件的电气特性和热性能,以确保系统的稳定运行。同时,由于技术不断发展,我们也需要持续关注产品的更新和改进,以适应新的设计需求。

在实际的设计过程中,你是否遇到过与AT17LV系列器件相关的问题呢?你又是如何解决的呢?欢迎在评论区分享你的经验和见解。

发布评论请先 登录

FPGA芯片配置方式及常见配置方法

有嵌入式EEPROM的FPGA系列吗?

AT17A系列FPGA配置EEPROM替代Altera EP

FPGA配置EEPROM存储器at17lv010

FPGA芯片配置分类及配置方式

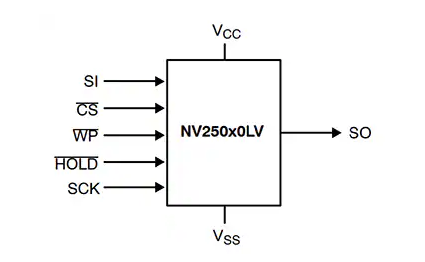

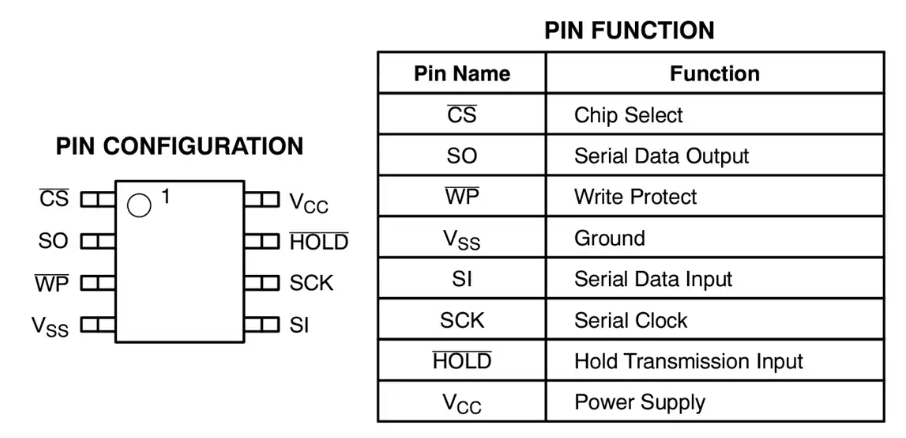

基于onsemi NV250x0LV系列EEPROM数据手册的技术解析与应用指南

探索onsemi EEPROM:NV25080LV系列的卓越性能与应用指南

探索Atmel AT17LV系列FPGA配置EEPROM:特性、应用与设计要点

探索Atmel AT17LV系列FPGA配置EEPROM:特性、应用与设计要点

评论