深入剖析LMK03000系列精密时钟调节器:特性、应用与设计要点

在当今数字化浪潮中,高精度时钟信号对于各类电子系统的稳定运行至关重要。在众多时钟调节器产品中,德州仪器(TI)的LMK03000系列凭借其卓越的性能和丰富的功能,成为了众多工程师的首选。今天,我们就来深入了解一下LMK03000系列精密时钟调节器。

文件下载:lmk03001.pdf

一、产品概述

LMK03000系列包括LMK03000、LMK03000C、LMK03000D、LMK03001、LMK03001C、LMK03001D、LMK03033和LMK03033C等型号。该系列产品集成了低相位噪声的电压控制振荡器(VCO)、高性能的整数N锁相环(PLL)、部分集成的环路滤波器,以及多达八个LVDS和LVPECL时钟输出分配模块,能够实现抖动清理、时钟倍频和分布等功能。

二、产品特性

2.1 卓越的时钟性能

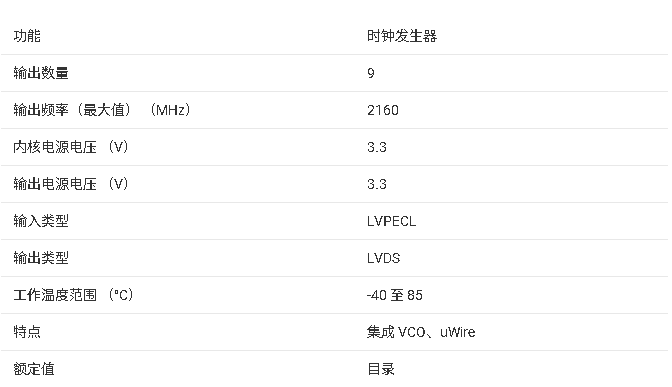

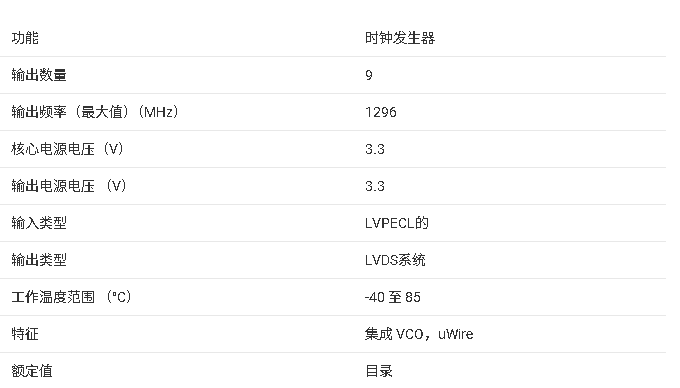

- 低相位噪声:集成的VCO具有极低的相位噪声底,整数N PLL的归一化相位噪声贡献可达 - 224 dBc/Hz,能够为系统提供高精度的时钟信号。不同型号的VCO输出频率范围有所不同,如LMK03000C的输出频率为400MHz,LMK03000的频率范围在1185 - 1296MHz,LMK03033C/LMK03033的频率范围为1843 - 2160MHz。

- 低抖动:在不同带宽下具有出色的RMS抖动性能,例如LMK03000C/LMK03001C的Fout RMS周期抖动在12kHz至20MHz带宽内为400fs,能够有效减少时钟抖动对系统的影响。

2.2 灵活的时钟配置

- 多样的分频选项:VCO分频值可选2 - 8,通道分频值可选1、2 - 510(偶数分频),可以根据不同的应用需求灵活配置时钟频率。

- 多种输出类型:提供LVDS和LVPECL时钟输出,满足不同类型设备对时钟信号的要求。

2.3 其他特性

- 集成部分环路滤波器:内部包含3阶和4阶极点,简化了环路滤波器的设计,同时提高了杂散性能。

- 引脚兼容:采用48引脚WQFN封装,与同系列其他时钟设备引脚兼容,方便进行升级和替换。

- 宽工作电压范围:工作电压范围为3.15 - 3.45V,具有较好的电源适应性。

三、目标应用

LMK03000系列适用于多种领域,包括数据转换器时钟、网络通信(SONET/SDH、DSLAM)、无线基础设施、医疗设备、测试测量以及军事/航空航天等领域。这些应用场景都对时钟信号的精度和稳定性有较高的要求,而LMK03000系列产品正好能够满足这些需求。

四、电气特性与规格

在使用该系列产品时,需要关注其电气特性和规格,以确保产品在合适的条件下正常工作。

4.1 绝对最大额定值

- 电源电压:范围为 - 0.3V至3.6V。

- 输入电压:范围为 - 0.3V至(Vcc + 0.3)V。

- 存储温度范围: - 65°C至150°C。

- 引脚温度(焊接4s):最高260°C。

- 结温:最高125°C。

4.2 推荐工作条件

- 环境温度: - 40°C至85°C。

- 电源电压:3.15V至3.45V,典型值为3.3V。

4.3 电流消耗与功耗

不同配置下的电流消耗有所不同,例如整个设备在一个LVDS和一个LVPECL时钟启用、无分频和无延迟的情况下,电源电流典型值为161.8mA;在所有输出关闭(无发射极电阻)时,电流为86mA。在设计电路时,需要根据具体的应用场景计算功耗,以确保系统的稳定性和可靠性。

4.4 时钟输出特性

- LVDS输出:具有20fs - 75fs的附加RMS抖动,差分输出电压范围为250 - 450mV等。

- LVPECL输出:附加RMS抖动为20fs - 75fs,输出高电压为Vcc - 0.98V,输出低电压为Vcc - 1.8V等。

五、功能描述与使用要点

5.1 偏置引脚(BIAS)

为了实现低噪声性能,需要使用一个低泄漏的1µF电容将偏置引脚(pin 36)连接到Vcc进行旁路。

5.2 LDO旁路

使用10µF电容对LDObyp1(pin 9)进行旁路,使用0.1µF电容对LDObyp2(pin 10)进行旁路,以保证器件的正常工作。

5.3 振荡器输入端口(OSCin,OSCin*)

OSCin端口用于为PLL提供参考信号,由于内部存在直流偏置,该端口应采用交流耦合方式。可以通过将OSCin*用0.1µF电容交流接地,实现单端驱动。

5.4 VCO频率校准

该系列器件的VCO使用频率校准算法,当编程R15寄存器时,会激活该算法。编程后,温度漂移不能超过最大允许的连续锁定温度漂移(ΔTCL),否则VCO可能无法保证锁定。同时,在编程R15时,OSCin必须由有效信号驱动。

5.5 时钟输出延迟

每个时钟输出都支持延迟调整,时钟输出延迟寄存器(CLKoutX_DLY)的步长为150ps,总延迟范围从0到2250ps。

5.6 时钟输出同步与使能

- 全局时钟输出同步:SYNC*引脚可用于同步时钟输出,当该引脚为低电平时,分频输出也被拉低;引脚变高后,分频时钟输出将同时变为高电平,实现同步。

- 时钟输出使能:每个时钟输出可以通过CLKoutX_EN位单独使能,也可以通过拉低GOE引脚或编程EN_CLKout_Global为0来同时禁用所有输出。

5.7 数字锁定检测

PLL数字锁定检测电路通过比较相位检测器输入的相位差与RC产生的延迟ε来判断锁定状态。当相位误差连续5个参考周期小于ε时,认为锁定;当误差大于δ时,认为失锁。ε和δ的值分别为10ns和20ns。当比较频率超过20MHz时,需要将DIV4字设置为1,以提高检测的准确性。

六、编程信息

6.1 编程寄存器

该系列器件通过多个32位寄存器进行编程,控制着设备的各种功能。其中,只有寄存器R0 - R7、R11和R13 - R15需要进行编程以确保设备正常运行。

6.2 推荐编程顺序

- 先将R0的复位位(RESET)设置为1,使设备处于默认状态。若再次编程R0,需将复位位清零。

- 根据需要对R0 - R7进行编程,设置时钟的使能、复用、分频和延迟等参数。

- 编程R8以获得最佳的相位噪声性能。

- 若需要,对R9进行编程设置Vboost。

- 根据情况对R11设置DIV4。

- 编程R13设置振荡器输入频率和内部环路滤波器值。

- 编程R14设置Fout使能位、全局时钟输出位、电源关闭设置、PLL复用设置和PLL R分频器。

- 最后编程R15设置PLL电荷泵增益、VCO分频器和PLL N分频器,同时启动频率校准程序。

七、应用设计要点

7.1 系统级设计

在实际应用中,需要注意OSCin/OSCin和CLKoutX/CLKoutX引脚可以单端或差分方式使用,GOE引脚需要设置为高电平以使输出正常工作。可以将LD引脚的输出作为GOE引脚的输入,当PLL失锁时,输出将关闭。

7.2 环路滤波器设计

LMK03000系列的内部电荷泵直接连接到集成的环路滤波器组件,第一和第二极点需要外部连接。在设计环路滤波器时,要确保其在整个频率范围内稳定,同时考虑到最小电阻热噪声的影响。通常可以选择最小的集成电阻值,并设计较大的内部电容值以获得足够宽的环路带宽。

7.3 电流消耗与功率计算

由于器件的配置多样,需要根据具体的配置计算电流消耗和功率。不同的输出模式、分频和延迟设置都会影响电流消耗,在设计时需要综合考虑这些因素。

7.4 热管理

该系列器件的功耗较高,需要注意热管理。为了确保可靠性和性能,管芯温度应限制在最高125°C。可以通过在PCB上设计热焊盘和多个过孔连接到接地层,以及在PCB另一侧设置铜面积较大的散热区域等方式来提高散热效果。

7.5 时钟输出端接和使用

在端接时钟驱动器时,要遵循传输线理论,进行良好的阻抗匹配,避免反射。对于LVDS和LVPECL驱动器,要提供合适的负载和直流偏置。根据不同的应用需求,可以采用直流耦合、交流耦合或单端驱动等方式,并选择合适的端接电路。

7.6 OSCin输入

OSCin输入除了支持LVDS和LVPECL输入外,还可以驱动正弦波。输入可以单端或差分方式使用,在使用正弦波输入时,需要注意输入功率的推荐范围,以保证PLL的噪声性能。

7.7 多输出应用

当需要超过8个输出时,可以结合使用LMK01000系列进行时钟分配。通过将一个LMK03000设备与多个LMK01000系列设备配合使用,最多可以分配64个时钟。

总之,LMK03000系列精密时钟调节器是一款功能强大、性能卓越的时钟解决方案。在实际应用中,工程师需要深入了解其特性、功能和设计要点,根据具体的应用需求进行合理的配置和设计,以实现最佳的系统性能。各位工程师在使用过程中有没有遇到过一些特殊的问题或者有趣的应用案例呢?欢迎在评论区分享交流。

发布评论请先 登录

LMK03000,datasheet,pdf(Precisi

LMK03002/LMK03002C精密时钟调节器数据表

LMK03000 1185 至 1296MHz、800fs RMS 抖动、集成 VCO 的精密时钟调节器技术手册

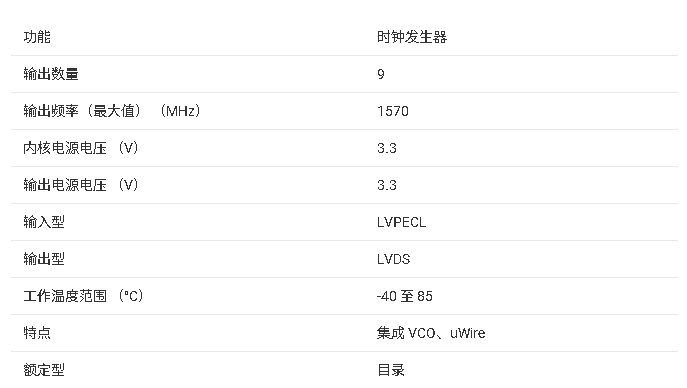

LMK03001 1470 至 1570 MHz、800 fs RMS 抖动、集成 VCO 的精密时钟调节器技术文档总结

深入剖析LMK03000系列精密时钟调节器:特性、应用与设计要点

深入剖析LMK03000系列精密时钟调节器:特性、应用与设计要点

评论