深入解析LMK03000系列精密时钟调节器

在电子设计领域,时钟信号的稳定性和准确性对于系统的性能至关重要。TI的LMK03000系列精密时钟调节器,凭借其出色的性能和丰富的功能,在众多应用场景中得到了广泛应用。本文将深入剖析LMK03000系列产品,帮助电子工程师更好地了解和使用该系列器件。

文件下载:lmk03000.pdf

一、产品概述

LMK03000系列包括LMK03000、LMK03000C、LMK03000D、LMK03001、LMK03001C、LMK03001D、LMK03033和LMK03033C等型号。这些器件集成了压控振荡器(VCO)、高性能整数N锁相环(PLL)、部分集成式环路滤波器,以及多达八个不同LVDS和LVPECL组合的输出,能够实现抖动清理/重新调节、参考时钟的乘法和分配等功能。

1.1 主要特性

- 低相位噪声VCO:集成的VCO具有极低的相位噪声本底,为系统提供稳定的时钟信号。

- 高性能PLL:整数N PLL的归一化相位噪声贡献低至 -224 dBc/Hz,有效减少相位噪声对系统的影响。

- 灵活的分频设置:VCO分频值为2至8,通道分频值为1、2至510(偶数分频),满足不同的时钟频率需求。

- 多种输出类型:支持LVDS和LVPECL时钟输出,可适应不同的负载需求。

- 部分集成环路滤波器:简化了设计,提高了系统的稳定性和抗干扰能力。

- 引脚兼容:该系列器件引脚兼容,方便在不同应用中进行替换和升级。

- 低功耗运行:工作电压范围为3.15至3.45 V,在提供高性能的同时降低功耗。

- 出色的时钟生成性能:在干净输入时钟的情况下,能够实现200 fs RMS的时钟生成性能(10 Hz至20 MHz)。

1.2 目标应用

LMK03000系列适用于多种应用场景,包括数据转换器时钟、网络通信(SONET/SDH、DSLAM)、无线基础设施、医疗设备、测试测量以及军事/航空航天等领域。

二、器件信息

2.1 功能框图

从功能框图可以看出,该器件主要由集成式环路滤波器、内部VCO、相位检测器、分频器、时钟分配路径和输出缓冲器等部分组成。OSCin端口提供参考信号,经过相位检测器与VCO输出信号进行比较,通过环路滤波器调整VCO的输出频率,实现锁相功能。VCO输出经过VCO分频器后,输入到各个时钟分配块,每个分配块包含可编程分频器、相位同步电路、可编程延迟、时钟输出复用器和输出缓冲器,可将参考时钟的多个整数相关且相位调整后的副本分配到八个系统组件。

2.2 连接图

48引脚WQFN封装的LMK03000系列器件,其引脚布局清晰,各引脚功能明确。其中,GND引脚用于接地,Vcc引脚提供电源,Fout引脚输出内部VCO频率,CLKuWire、DATAuWire和LEuWire用于编程控制,CLKoutX和CLKoutX*用于时钟输出等。具体引脚功能可参考下表:

| Pin # | Pin Name | I/O | Description |

|---|---|---|---|

| 1, 25 | GND | - | Ground |

| 2 | Fout | O | Internal VCO Frequency Output |

| 3, 8, 13, 16, 19, 22, 26, 30, 31, 33, 37, 40, 43, 46 | Vcc1, Vcc2, Vcc3, Vcc4, Vcc5, Vcc6, Vcc7, Vcc8, Vcc9, Vcc10, Vcc11, Vcc12, Vcc13, Vcc14 | - | Power Supply |

| 4 | CLKuWire | I | MICROWIRE Clock Input |

| 5 | DATAuWire | I | MICROWIRE Data Input |

| 6 | LEuWire | I | MICROWIRE Latch Enable Input |

| 7, 34, 35 | NC | - | No Connection to these pins |

| 9, 10 | LDObyp1, LDObyp2 | - | LDO Bypass |

| 11 | GOE | I | Global Output Enable |

| 12 | LD | O | Lock Detect and Test Output |

| 14, 15 | CLKout0, CLKout0* | O | LVDS Clock Output 0 |

| 17, 18 | CLKout1, CLKout1* | O | LVDS Clock Output 1 |

| 20, 21 | CLKout2, CLKout2* | O | LVDS Clock Output 2 |

| 23, 24 | CLKout3, CLKout3* | O | Clock Output 3 (LVDS for LMK03033C/LMK03033 LVPECL for all other parts) |

| 27 | SYNC* | I | Global Clock Output Synchronization |

| 28, 29 | OSCin, OSCin* | I | Oscillator Clock Input; Should be AC coupled |

| 32 | CPout | O | Charge Pump Output |

| 36 | Bias | I | Bias Bypass |

| 38, 39 | CLKout4, CLKout4* | O | LVPECL Clock Output 4 |

| 41, 42 | CLKout5, CLKout5* | O | LVPECL Clock Output 5 |

| 44, 45 | CLKout6, CLKout6* | O | LVPECL Clock Output 6 |

| 47, 48 | CLKout7, CLKout7* | O | LVPECLClock Output 7 |

| DAP | DAP | - | Die Attach Pad is Ground |

三、电气规格

3.1 绝对最大额定值

该系列器件的绝对最大额定值规定了其安全工作的范围,包括电源电压、输入电压、存储温度范围、引脚温度和结温等参数。例如,电源电压范围为 -0.3至3.6 V,存储温度范围为 -65至150 °C等。在设计过程中,必须确保器件的工作条件在这些额定值范围内,以避免损坏器件。

3.2 推荐工作条件

推荐工作条件为器件的正常工作提供了最佳环境。环境温度范围为 -40至85 °C,电源电压范围为3.15至3.45 V。在这些条件下,器件能够发挥最佳性能。

3.3 封装热阻

48引脚WQFN封装的热阻为5.8 °C/W,通过在PCB上使用16个热过孔将裸片连接到嵌入式铜平面,可以有效提高散热性能。在设计时,应尽量使用更多的过孔,以降低器件的温度。

3.4 电气特性

电气特性详细描述了器件在不同工作条件下的性能参数,包括电流消耗、参考振荡器、PLL、VCO等方面。例如,在整个器件中,当一个LVDS和一个LVPECL时钟启用,无分频和延迟时,电源电流典型值为161.8 mA;参考振荡器输入频率范围为1至200 MHz等。这些参数为工程师在设计电路时提供了重要的参考依据。

四、测量定义

文档中对电荷泵电流的相关参数进行了详细定义,包括电荷泵输出电流幅度随输出电压的变化、电荷泵吸收电流与源电流的失配以及电荷泵输出电流幅度随温度的变化等。这些定义有助于工程师准确理解和测量器件的性能。

五、典型性能特性

典型性能特性图表展示了器件在不同频率下的性能表现,如LVDS和LVPECL差分输出电压、输出缓冲器噪声本底以及延迟噪声本底等。这些图表虽然展示了超出器件保证工作频率范围的性能,但可以让用户了解器件的潜在能力。

六、功能描述

6.1 BIAS引脚

为了实现低噪声性能,需要使用一个低泄漏的1 µF电容器将Bias引脚(36脚)旁路到Vcc。

6.2 LDO旁路

将LDObyp1(9脚)用10 µF电容器旁路,LDObyp2(10脚)用0.1 µF电容器旁路,以确保器件的正常工作。

6.3 振荡器输入端口(OSCin,OSCin*)

OSCin端口为PLL提供参考信号,由于内部存在直流偏置,该端口应进行交流耦合。可以通过将OSCin*用0.1 µF电容器交流接地,实现单端驱动。

6.4 低噪声、完全集成的VCO

LMK03000系列器件包含一个完全集成的VCO,为了确保正常工作,VCO使用了频率校准算法。当编程R15寄存器时,会激活频率校准算法。一旦R15寄存器编程完成,温度漂移不得超过连续锁定的最大允许漂移,否则VCO无法保证保持锁定。

6.5 CLKout延迟

每个时钟输出都包含一个延迟调整功能,时钟输出延迟寄存器(CLKoutX_DLY)支持150 ps的步长,总延迟范围为0至2250 ps。

6.6 LVDS/LVPECL输出

默认情况下,所有时钟输出均处于禁用状态,直到进行编程。可以通过编程CLKoutX_EN位单独禁用每个LVDS或LVPECL输出,也可以通过将GOE引脚拉低或编程EN_CLKout_Global为0来同时禁用所有输出。不同的VCO_DIV和CLKoutX_MUX设置会影响时钟输出的占空比。

6.7 全局时钟输出同步

SYNC引脚用于同步时钟输出。当SYNC引脚保持低电平时,分频输出也保持低电平,旁路输出继续正常工作。SYNC*引脚变为高电平后不久,分频时钟输出将同时变为高电平,实现所有输出的同步。

6.8 CLKout输出状态

每个时钟输出可以通过CLKoutX_EN位单独启用,同时受到全局输出使能输入引脚(GOE)和全局输出使能位(EN_CLKout_Global)的控制。当LVDS输出处于关闭状态时,输出电压约为1.5 V;当LVPECL输出处于关闭状态时,输出电压约为1 V。

6.9 全局输出使能和锁定检测

GOE引脚具有内部上拉电阻,如果未进行外部端接,时钟输出状态由时钟输出使能位(CLKoutX_EN)和EN_CLKout_Global位决定。通过编程PLL_MUX寄存器为数字锁定检测高电平有效,可以将锁定检测(LD)引脚连接到GOE引脚,当合成器未锁定时,所有输出将自动置低。

6.10 上电复位

当器件的电源电压从地单调增加到Vcc时,上电复位电路将所有寄存器设置为默认值。所有Vcc引脚应同时施加电压。

6.11 数字锁定检测

PLL数字锁定检测电路通过比较相位检测器输入的相位差与RC产生的延迟ε来判断是否锁定。当相位误差连续5个参考周期小于ε时,指示锁定状态;当相位误差大于δ时,指示失锁状态。为了提高数字锁定检测的准确性,当比较频率超过20 MHz时,应将DIV4字设置为1。

七、通用编程信息

7.1 推荐编程顺序

推荐的编程顺序是先将R0寄存器的复位位设置为1,确保器件处于默认状态,然后依次编程R0至R7、R8、R9、R11、R13、R14和R15寄存器。编程R15寄存器时会启动频率校准程序。

7.2 寄存器R0至R7

这些寄存器控制八个时钟输出,每个寄存器对应一个时钟输出。寄存器中的位包括RESET、CLKoutX_MUX、CLKoutX_EN、CLKoutX_DIV、CLKoutX_DLY等,用于控制时钟输出的复用模式、使能状态、分频值和延迟等。

7.3 寄存器R8

编程R8寄存器可以提供最佳的相位噪声性能。

7.4 寄存器R9

编程R9寄存器是可选的,如果未编程,Vboost位将默认为0。启用Vboost位可以提高所有时钟输出的电压输出电平,并改善噪声本底。

7.5 寄存器R11

当相位检测器频率大于20 MHz且使用数字锁定检测时,需要编程该寄存器。DIV4位用于将呈现给数字锁定检测电路的频率除以4,以确保数字锁定检测输出的可靠性。

7.6 寄存器R13

该寄存器控制内部环路滤波器的电容和电阻值,以及振荡器输入频率的校准调整。

7.7 寄存器R14

寄存器R14包含PLL_R分频值、PLL_MUX输出模式、POWERDOWN位、EN_CLKout_Global位和EN_Fout位等,用于控制PLL的分频、LD引脚的输出模式、器件的电源状态、全局时钟输出使能和Fout端口的使能。

7.8 寄存器R15

编程R15寄存器会激活频率校准程序,该寄存器包含PLL_N分频值、VCO_DIV分频值和PLL_CP_GAIN电荷泵增益等参数。

八、应用信息

8.1 系统级图

在典型应用中,LMK03000系列器件可以对时钟进行乘法、重新调节和重新分配。OSCin/OSCin和CLKoutX/CLKoutX引脚可以单端或差分使用,GOE引脚需要保持高电平以使输出正常工作。可以将LD引脚的输出作为GOE引脚的输入,当锁定检测电路检测到PLL失锁时,输出将关闭。

8.2 BIAS引脚和LDO旁路

参考功能描述部分的相关内容,确保正确使用BIAS引脚和LDO旁路。

8.3 环路滤波器

内部电荷泵直接连接到集成式环路滤波器组件,环路滤波器的第一和第二极点需要外部连接。设计环路滤波器时,必须确保其在整个频率范围内稳定,同时要考虑最小电阻热噪声和环路带宽等因素。

8.4 电流消耗/功耗计算

文档提供了不同配置下器件的电流消耗和功耗计算方法,通过将各个模块的电流消耗相加,并减去LVPECL输出发射极电阻的功耗,可以得到器件的总功耗。

8.5 热管理

由于LMK03000系列器件的功耗可能较高,需要注意热管理。为了确保器件的可靠性和性能,芯片温度应限制在最大125 °C以内。可以通过在PCB上设计散热图案、使用热过孔和散热片等方式来降低器件温度。

8.6 时钟输出的端接和使用

在端接时钟驱动器时,应遵循传输线理论,确保良好的阻抗匹配,避免反射。LVDS驱动器需要闭合电流回路,LVPECL驱动器需要直流接地路径。同时,应确保接收器的信号偏置到指定的直流偏置电平。文档还详细介绍了DC耦合、AC耦合和单端操作的端接方法,以及如何将LVDS或LVPECL输出转换为LVCMOS输出。

8.7 OSCin输入

OSCin输入除了支持LVDS和LVPECL输入外,还可以使用正弦波驱动。可以单端或差分输入正弦波,文档给出了不同输入方式的配置图和推荐的功率电平。

8.8 更多输出需求

当需要超过八个输出时,可以使用与LMK03000系列引脚兼容的LMK01000系列进行时钟分配,通过组合使用多个器件,可以实现多达64个时钟的分配。

综上所述,LMK03000系列精密时钟调节器是一款功能强大、性能优异的时钟管理器件。电子工程师在设计过程中,应充分了解其特性、功能和应用要求,合理进行电路设计和编程配置,以确保系统的稳定性和可靠性。同时,在实际应用中,还需要注意热管理、端接和布线等问题,以充分发挥器件的性能优势。大家在使用过程中遇到过哪些问题呢?欢迎在评论区分享交流。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

LMK03000,datasheet,pdf(Precisi

LMK03002/LMK03002C精密时钟调节器数据表

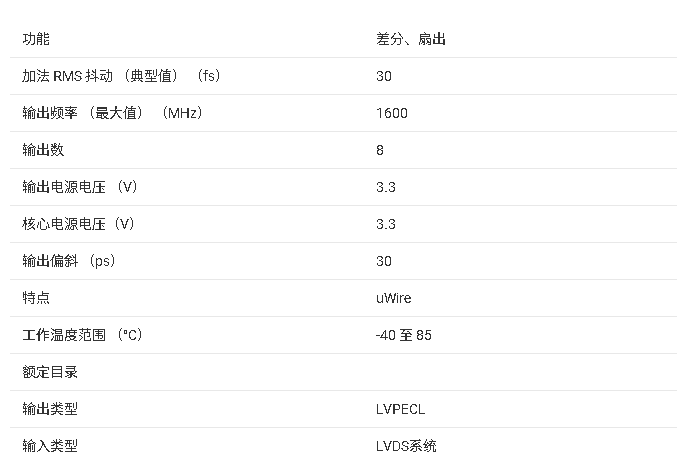

LMK01020 1.6 GHz 高性能时钟缓冲器、分频器和分配器技术手册

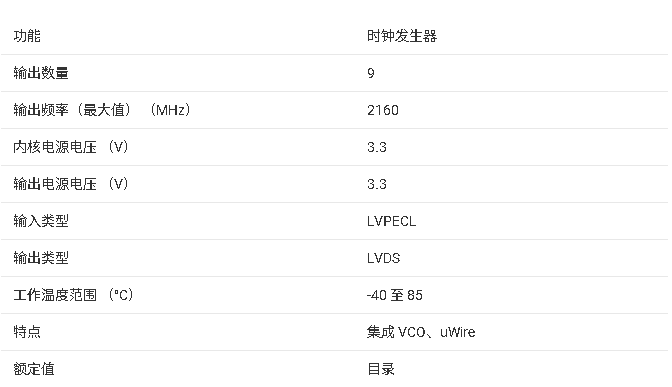

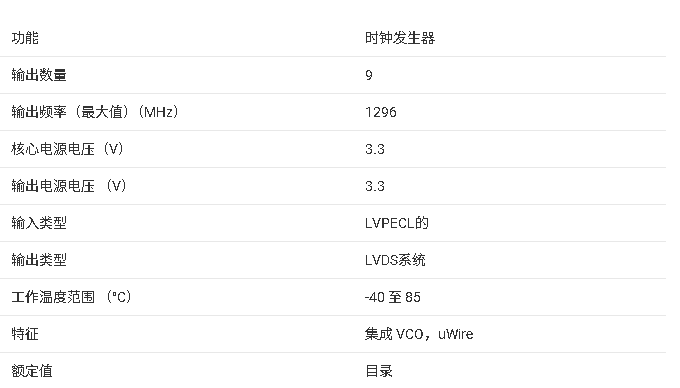

LMK03000 1185 至 1296MHz、800fs RMS 抖动、集成 VCO 的精密时钟调节器技术手册

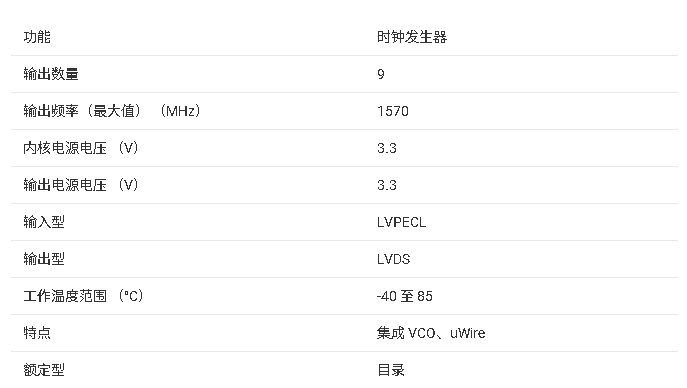

LMK03001 1470 至 1570 MHz、800 fs RMS 抖动、集成 VCO 的精密时钟调节器技术文档总结

深入解析LMK03000系列精密时钟调节器

深入解析LMK03000系列精密时钟调节器

评论