探索LMK03000系列精密时钟调节器:设计与应用指南

在电子设计领域,时钟信号的稳定性和精度对于系统的性能至关重要。德州仪器(TI)的LMK03000系列精密时钟调节器,集成了低噪声压控振荡器(VCO)和高性能整数N锁相环(PLL),为数据转换器、网络、无线基础设施等众多应用提供了理想的时钟解决方案。

文件下载:lmk03033.pdf

1. 功能特色

1.1 低噪声VCO与高性能PLL

LMK03000系列集成了超低相位噪声本底的VCO,以及归一化相位噪声贡献达 -224 dBc/Hz的整数N锁相环。VCO的分频值范围为2 - 8,通道分频值可为1、2 - 510(偶数分频),为时钟信号的生成和调节提供了丰富的选择。

1.2 多输出接口与灵活配置

该系列支持LVDS和LVPECL时钟输出,每个时钟输出都配备了专用的分频器和延迟块,可实现多个整数相关且相位可调的时钟信号分布。此外,部分集成的环路滤波器和48引脚WQFN封装,使其与同系列其他时钟器件引脚兼容,方便设计和替换。

1.3 高精度时钟性能

在干净输入时钟的条件下,LMK03000系列可实现200 fs RMS的时钟发生器性能(10 Hz - 20 MHz),确保了系统时钟的高精度和低抖动。

2. 应用场景

LMK03000系列的目标应用广泛,涵盖了数据转换器时钟、网络、无线基础设施、医疗、测试与测量以及军事/航空航天等领域。其不同型号具有不同的输出特性和调谐范围,以满足各种应用的需求。

| 型号 | 输出类型 | 调谐范围(MHz) | RMS抖动(fs) |

|---|---|---|---|

| LMK03000C | 3 LVDS | 400 | |

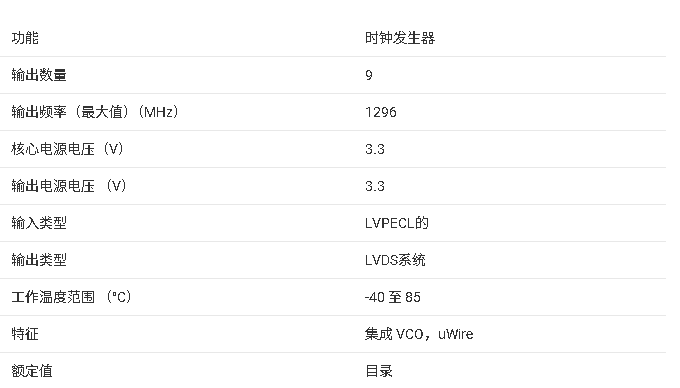

| LMK03000 | 1185 - 1296 | 800 | |

| LMK03000D | 3 LVDS | 1200 | |

| LMK03001C | 5 LVPECL | 400 | |

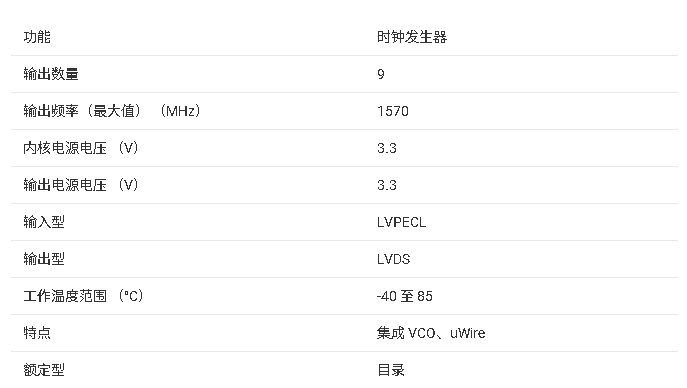

| LMK03001 | 1470 - 1570 | 800 | |

| LMK03001D | 1200 | ||

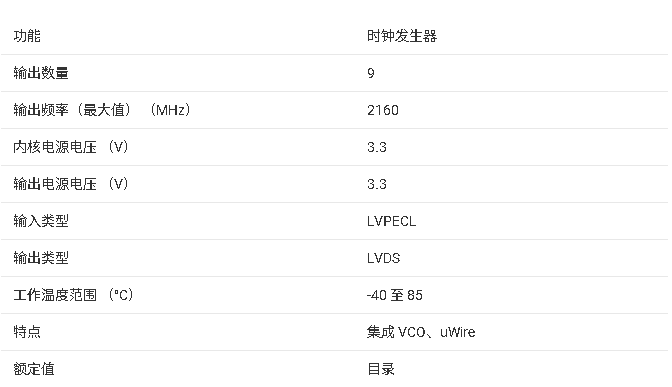

| LMK03033C/LMK03033 | 4 LVPECL/4 LVDS | 1843 - 2160 | 500/800 |

3. 电气特性与性能

3.1 绝对最大额定值与推荐工作条件

在设计中,我们需要关注器件的绝对最大额定值和推荐工作条件,以确保器件的正常运行和可靠性。LMK03000系列的电源电压范围为3.15 - 3.45 V,环境温度范围为 -40°C - 85°C。

3.2 电流消耗与功耗计算

器件的电流消耗和功耗是设计中的重要考虑因素。LMK03000系列在不同配置下的电流消耗不同,例如,在一个LVDS和一个LVPECL时钟启用、无分频和无延迟的情况下,典型电流消耗为161.8 mA。通过合理配置输出和功能,可以有效降低功耗。

3.3 典型性能特性

典型性能特性图表展示了器件在不同频率和条件下的性能表现,如LVDS和LVPECL差分输出电压、输出缓冲器噪声本底等。这些特性有助于我们评估器件在实际应用中的性能。

4. 功能描述与编程

4.1 关键引脚功能

- BIAS引脚:通过一个低泄漏的1 µF电容连接到Vcc进行旁路,对于低噪声性能至关重要。

- LDO旁路:LDObyp1(引脚9)用10 µF电容旁路,LDObyp2(引脚10)用0.1 µF电容旁路。

- *振荡器输入端口(OSCin, OSCin)**:为PLL提供参考信号,应采用交流耦合方式。

4.2 低噪声VCO与频率校准

LMK03000系列的VCO采用频率校准算法,当R15寄存器编程时,频率校准算法被激活。编程后,温度漂移不得超过连续锁定的最大允许漂移,否则VCO可能无法保持锁定。

4.3 时钟输出控制与同步

时钟输出可通过编程单独或全局启用/禁用,LVDS和LVPECL输出的占空比可根据VCO分频和输出模式进行调整。SYNC*引脚可实现时钟输出的同步,确保所有输出时钟信号的相位一致。

4.4 编程信息

器件通过多个32位寄存器进行编程,推荐的编程顺序包括先将R0的复位位设置为1,确保器件处于默认状态,然后依次编程其他寄存器,最后编程R15以启动频率校准程序。

5. 应用设计要点

5.1 系统级设计

在典型应用中,LMK03000系列的OSCin/OSCin和CLKoutX/CLKout引脚可单端或差分使用。GOE引脚需保持高电平以使输出正常工作,可将LD引脚的输出作为GOE引脚的输入,实现锁定检测功能。

5.2 环路滤波器设计

环路滤波器由七个组件组成,其中四个组件构成的第三和第四极点集成在芯片内,第一和第二极点为外部组件。设计时需确保环路滤波器在整个频率范围内稳定,可根据具体应用选择合适的电阻和电容值。

5.3 热管理

由于器件功耗较高,热管理至关重要。通过在PCB上设计热焊盘和多个过孔连接到接地层,可有效提高散热效率。同时,可在PCB另一侧增加铜面积作为简单的散热片。

5.4 时钟输出端接与使用

在端接时钟驱动器时,需遵循传输线理论进行阻抗匹配,确保时钟驱动器和接收器的负载匹配。对于LVDS和LVPECL驱动器,可根据不同的应用场景选择合适的端接和耦合方式。

6. 总结

LMK03000系列精密时钟调节器以其卓越的性能和丰富的功能,为电子设计提供了可靠的时钟解决方案。在实际应用中,我们需要根据具体需求选择合适的型号和配置,合理设计环路滤波器和热管理方案,正确进行时钟输出端接和编程,以确保系统的稳定性和性能。希望本文能为电子工程师在使用LMK03000系列器件时提供有益的参考。你在使用这款器件时遇到过哪些问题呢?欢迎在评论区分享你的经验和见解。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

LMK03000,datasheet,pdf(Precisi

LMK03002/LMK03002C精密时钟调节器数据表

LMK03000 1185 至 1296MHz、800fs RMS 抖动、集成 VCO 的精密时钟调节器技术手册

LMK03001 1470 至 1570 MHz、800 fs RMS 抖动、集成 VCO 的精密时钟调节器技术文档总结

探索LMK03000系列精密时钟调节器:设计与应用指南

探索LMK03000系列精密时钟调节器:设计与应用指南

评论