LMK03002/LMK03002C 精密时钟调节器:特性、应用与设计指南

在电子设计领域,时钟信号的稳定性和准确性对于系统的性能至关重要。今天,我们来深入了解一下德州仪器(Texas Instruments)的 LMK03002/LMK03002C 精密时钟调节器,探讨它的特性、应用场景以及设计要点。

文件下载:lmk03002.pdf

一、产品概述

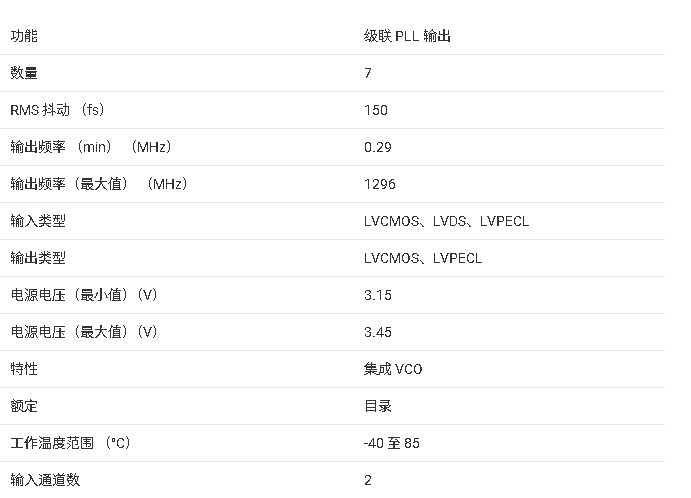

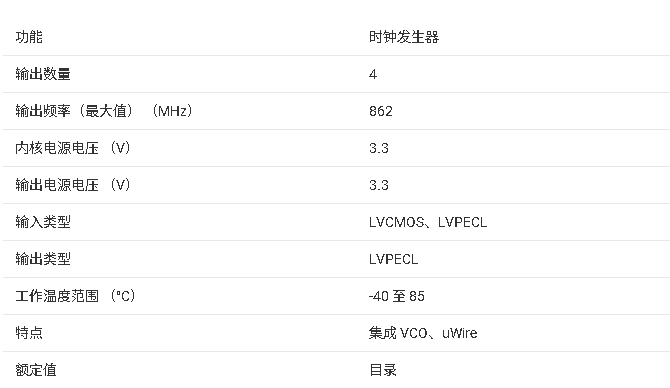

LMK03002/LMK03002C 是一款集抖动清理、时钟倍频和分配功能于一体的精密时钟调节器。它集成了压控振荡器(VCO)、高性能整数 N 锁相环(PLL)、部分集成的环路滤波器以及四个 LVPECL 时钟输出分配模块。这种高度集成的设计使得它在各种对时钟精度要求较高的应用中表现出色。

二、产品特性

(一)低相位噪声

- 集成 VCO:VCO 具有极低的相位噪声本底,频率范围为 1566 至 1724 MHz。在 12 kHz 至 20 MHz 带宽内,LMK03002 的 Fout RMS 周期抖动为 800 fs,LMK03002C 更是低至 400 fs。

- PLL 性能:PLL 的归一化相位噪声贡献可达 -224 dBc/Hz,在 10 kHz 偏移处的 1/f 噪声(PN10kHz)在不同增益设置下表现优异,如 PLL_CP_GAIN = 32x 时,PN10kHz 为 -122 dBc/Hz。

(二)高精度时钟输出

- 输出频率范围:时钟输出频率范围为 1 至 862 MHz,可满足多种应用需求。

- 抖动清理能力:在时钟生成性能(10 Hz - 20 MHz)方面,LMK03002C 的 RMS 抖动为 200 fs;在抖动清理性能等级(12 kHz 至 20 MHz)方面,LMK03002 为 800 fs,LMK03002C 为 400 fs。

(三)灵活的输出配置

- 输出类型:提供 4 个 LVPECL 时钟输出,每个输出都有专用的分频器和延迟块,可实现可编程分频、相位同步和延迟调整。

- 同步功能:通过 SYNC* 引脚可实现时钟输出的同步,确保多个输出之间的相位一致性。

(四)其他特性

- 电源电压:工作电压范围为 3.15 至 3.45 V,典型值为 3.3 V。

- 封装形式:采用 48 引脚 WQFN 封装(7.0 x 7.0 x 0.8 mm),与同系列其他时钟器件引脚兼容,便于 PCB 设计和升级。

三、目标应用

LMK03002/LMK03002C 的高性能使其在多个领域得到广泛应用:

- 数据转换器时钟:为 ADC 和 DAC 提供稳定、低抖动的时钟信号,确保数据转换的准确性。

- 网络通信:适用于 SONET/SDH、DSLAM 等网络设备,满足高速数据传输对时钟精度的要求。

- 无线基础设施:为基站、无线接入点等设备提供可靠的时钟源。

- 医疗设备:在医疗成像、监测等设备中,保证时钟信号的稳定性对于准确的数据采集和处理至关重要。

- 测试与测量:为测试仪器提供高精度的时钟参考,确保测量结果的准确性。

- 军事/航空航天:满足军事和航空航天领域对设备可靠性和性能的严格要求。

四、功能描述

(一)内部结构

该器件集成了 VCO、PLL、部分集成的环路滤波器和四个 LVPECL 时钟输出分配模块。内部包含 3 阶和 4 阶极点,简化了环路滤波器的设计,同时 1 阶和 2 阶极点位于片外,为不同环路滤波器带宽的设计提供了灵活性。

(二)时钟输出分配

每个时钟输出分配模块包括可编程分频器、相位同步电路、可编程延迟、时钟输出多路复用器和 LVPECL 输出缓冲器。通过这些模块,可以将参考时钟的多个整数相关且相位调整后的副本分配到四个系统组件中。

(三)关键引脚功能

- BIAS 引脚:需使用低泄漏的 1 µF 电容连接到 Vcc 进行旁路,以确保低噪声性能。

- LDO BYPASS 引脚:LDObyp1 用 10 µF 电容旁路,LDObyp2 用 0.1 µF 电容旁路。

- *OSCin/OSCin 引脚**:为 PLL 提供参考信号,必须进行 AC 耦合。

- *SYNC 引脚**:用于同步时钟输出,当该引脚为低电平时,分频输出也为低电平;引脚变为高电平后,分频时钟输出将同时变为高电平。

五、编程与配置

(一)寄存器编程

LMK03002/LMK03002C 通过多个 32 位寄存器进行编程,只需对 R0、R4 至 R8、R11、R13 至 R15 等寄存器进行编程即可确保设备正常工作。编程时,需注意 OSCin 必须在编程 R15 时提供有效信号,以激活频率校准算法。

(二)推荐编程顺序

- 对 R0 进行编程,设置复位位(RESET = 1),确保设备处于默认状态。

- 根据需要对 R4 至 R7 进行编程,设置所需的时钟参数,如使能、多路复用、分频和延迟等。

- 对 R8 进行编程,以获得最佳的相位噪声性能。

- 如有需要,对 R9 进行编程,设置 Vboost 参数。

- 若相位检测器频率大于 20 MHz 且使用数字锁定检测功能,对 R11 进行编程,设置 DIV4 参数。

- 对 R13 进行编程,设置振荡器输入频率和内部环路滤波器值。

- 对 R14 进行编程,设置 Fout 使能、全局时钟输出使能、电源关断、PLL 多路复用和 PLL R 分频值。

- 最后对 R15 进行编程,设置 PLL 电荷泵增益、VCO 分频和 PLL N 分频值,同时激活频率校准算法。

六、设计要点

(一)环路滤波器设计

环路滤波器的设计对于 PLL 的性能至关重要。内部电荷泵直接连接到集成的环路滤波器组件,而 1 阶和 2 阶极点位于片外。设计时需确保环路滤波器在整个频率范围内稳定,同时考虑最小电阻热噪声和环路带宽的要求。

(二)电源与接地

为了保证设备的稳定性和低噪声性能,所有 Vcc 引脚应同时施加电压,并且要注意 BIAS 引脚和 LDO BYPASS 引脚的旁路电容配置。同时,良好的接地设计对于减少干扰和噪声也非常重要。

(三)热管理

由于该器件的功耗可能较高,需要注意热管理。建议在 PCB 上设计散热图案,包括多个通孔连接到接地层,以提高散热效率。如果可能,还可以在 PCB 上构建简单的散热片,以降低结温。

(四)时钟输出端接

在端接时钟驱动器时,应遵循传输线理论,确保良好的阻抗匹配,防止反射。对于 LVPECL 驱动器,需要提供直流接地路径;对于接收器,应确保信号偏置到其指定的直流偏置电平。

七、总结

LMK03002/LMK03002C 精密时钟调节器以其低相位噪声、高精度时钟输出、灵活的输出配置和丰富的功能,为电子工程师在时钟设计方面提供了一个强大的解决方案。在实际应用中,通过合理的编程配置、精心的设计和良好的热管理,可以充分发挥该器件的性能优势,满足各种对时钟精度要求较高的应用需求。

希望这篇文章能对大家在使用 LMK03002/LMK03002C 进行电子设计时有所帮助。如果你在设计过程中遇到任何问题,欢迎在评论区留言交流。

-

电子设计

+关注

关注

42文章

2870浏览量

49916

发布评论请先 登录

LMK03002/LMK03002C精密时钟调节器数据表

LMK03002/LMK03002C 精密时钟调节器:特性、应用与设计指南

LMK03002/LMK03002C 精密时钟调节器:特性、应用与设计指南

评论