LMK04000系列时钟抖动清理器:高精度时钟解决方案

在电子设计领域,时钟信号的稳定性和低抖动性能对于众多应用至关重要。德州仪器(TI)的LMK04000系列精密时钟调节器,为数据转换器时钟、无线基础设施、网络等多个领域提供了低噪声抖动清理、时钟乘法和分配的理想解决方案。今天,我们就来深入了解一下这个系列的产品。

文件下载:lmk04033.pdf

产品概述

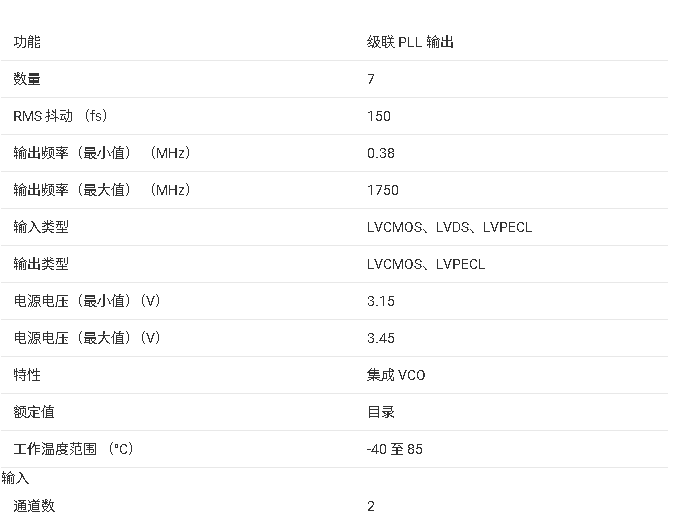

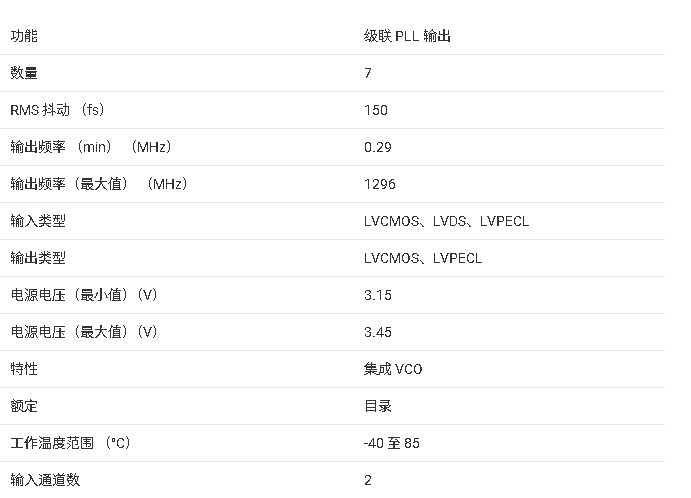

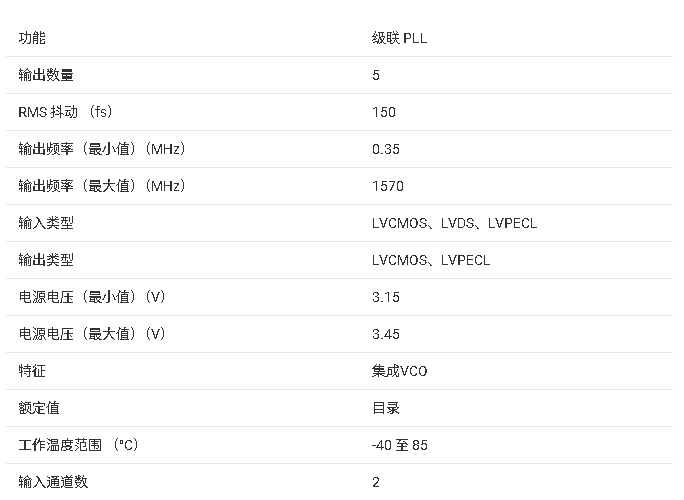

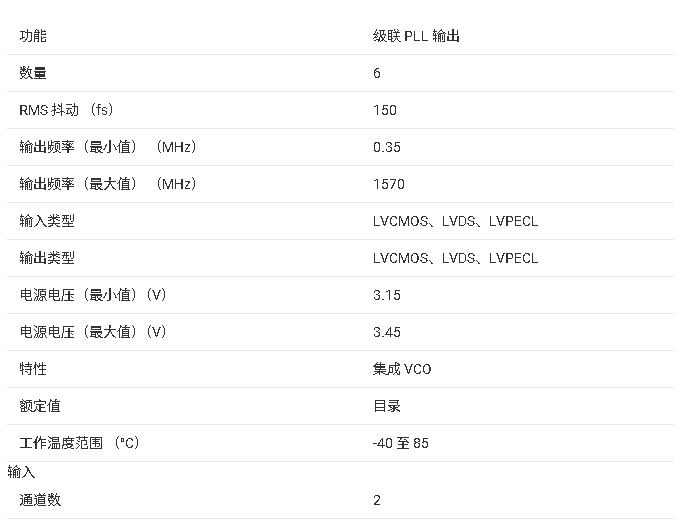

LMK04000系列包括LMK04000、LMK04001、LMK04002、LMK04010、LMK04011、LMK04031和LMK04033等型号。该系列采用级联PLLatinum™架构,结合外部晶体和变容二极管,无需高性能压控晶体振荡器(VCXO)模块,就能实现低于200飞秒(fs)的均方根(RMS)抖动性能。

产品特性亮点

级联PLLatinum™架构

级联架构由两个高性能锁相环(PLL)、一个低噪声晶体振荡器电路和一个高性能压控振荡器(VCO)组成。PLL1提供低噪声抖动清理功能,PLL2进行时钟生成。PLL1可配置为与外部VCXO模块配合使用,或使用集成晶体振荡器与外部晶体和变容二极管。当使用非常窄的环路带宽时,PLL1利用VCXO模块或晶体的优异近端相位噪声(偏移低于50 kHz)来清理输入时钟。PLL2的环路带宽可以优化,以清理远端相位噪声(偏移高于50 kHz),在这方面,集成VCO优于PLL1中使用的VCXO模块或晶体。

- PLL1参数:相位检测器速率高达40 MHz,集成低噪声晶体振荡器电路,具有带信号丢失检测(LOS)的双冗余输入参考时钟。

- PLL2参数:归一化[1 Hz]PLL噪声底至 - 224 dBc/Hz,相位检测器速率高达100 MHz,具有输入频率倍增器,集成低噪声VCO。

超低RMS抖动性能

- 150 fs RMS抖动(12 kHz – 20 MHz)

- 200 fs RMS抖动(100 Hz – 20 MHz)

丰富的输出类型和功能

- 支持LVPECL/2VPECL、LVDS和LVCMOS输出,支持高达1080 MHz的时钟速率。

- 上电时具有默认时钟输出(CLKout2)。

- 五个专用通道分频器和延迟块,引脚兼容的时钟设备系列。

- 工业温度范围为 - 40至85 °C,工作电压为3.15 V至3.45 V,采用48引脚WQFN(7.0 x 7.0 x 0.8 mm)封装。

应用领域广泛

该系列产品适用于多个领域,包括数据转换器时钟、无线基础设施、网络(SONET/SDH、DSLAM)、医疗、军事/航空航天、测试和测量以及视频等。

详细功能解析

系统架构

级联PLL架构旨在在最宽的输出频率和相位噪声偏移频率范围内提供最低的抖动性能。PLL1与外部参考时钟和外部VCXO配合使用,为PLL2提供频率准确、低相位噪声的参考时钟。PLL2可以使用更宽的环路带宽,利用内部VCO的优异高偏移频率相位噪声和参考VCXO的良好低偏移频率相位噪声,实现超低抖动。

冗余参考输入

LMK040xx有两个LVDS/LVPECL/LVCMOS兼容的PLL1参考时钟输入(CLKin0和CLKin1)。可以将首选输入固定为CLKin0或CLKin1,也可以配置为在存在冗余时钟信号时采用两种自动切换模式之一。PLL1参考时钟输入缓冲器还可以单独配置为CMOS缓冲输入或双极缓冲输入。

PLL1 CLKinX信号丢失检测

当为参考时钟输入模式选择两种自动切换模式之一时,所选参考时钟输入的信号状态由CLKinX_LOS(信号丢失)输出的状态指示。这些输出可以配置为CMOS(信号丢失时为高电平)、NMOS开漏或PMOS开漏。如果PLL1最初已锁定,然后两个参考时钟都消失,则LMK04000设备的频率精度将由PLL1上使用的VCXO的绝对调谐范围确定。

集成环路滤波器极点

LMK040xx具有可编程的3阶和4阶PLL2环路滤波器极点。启用后,可以从固定值范围中选择内部电阻器和电容器值,以实现3阶或4阶环路滤波器响应。这些可编程组件与芯片附近安装的外部组件互补。

时钟分配

LMK040xx具有一个时钟分配块,至少有五个输出,包括LVPECL、2VPECL、LVDS和LVCMOS的组合。具体组合由部件号决定。2VPECL是美国国家半导体的专有配置,可产生2 Vpp差分摆幅,与许多数据转换器兼容。

时钟输出控制

每个时钟输出通道可以通过时钟输出使能控制位启用或置于高阻抗状态。每个输出使能控制位与全局输出使能输入引脚(GOE)进行与运算。GOE引脚提供内部上拉,因此如果外部未端接,则时钟输出状态由时钟通道输出使能寄存器位确定。如果GOE引脚被外部信号拉低,则所有时钟输出可以同时禁用。

锁定检测

锁定检测(LD)信号可以连接到GOE引脚,在这种情况下,如果合成器未锁定,则所有输出将自动禁用。LD引脚可以编程为在PLL1和PLL2都锁定时输出“高”,或仅在PLL1锁定时输出“高”,或仅在PLL2锁定时输出“高”。

电气特性分析

电源和温度范围

- 电源电压范围为 - 0.3至3.6 V,输入电压范围为 - 0.3至(VCC + 0.3)V。

- 存储温度范围为 - 65至150 °C,引脚焊接温度(4秒)为 + 260 °C。

- 差分输入电流(CLKinX/X,OSCin/OSCin)为 ± 5 mA。

电流消耗

不同型号和工作模式下的电流消耗不同,例如,在所有时钟启用、所有延迟旁路、Fout禁用的情况下,LMK04000、LMK04001、LMK04002的典型电流消耗为380 mA,最大值为435 mA。

输入时钟规格

CLKin0/0和CLKin1/1的时钟输入频率在手动选择模式下为0.001至400 MHz,在自动切换模式下为1至400 MHz。

其他电气特性

还包括PLL1和PLL2的各种参数,如相位检测器频率、电荷泵电流、噪声等,以及内部VCO的调谐范围、相位噪声和抖动等特性。

应用信息与设计要点

典型应用电路

典型应用电路中,主参考时钟输入在CLKin0/0,辅助参考时钟驱动CLKin1/1。连接到OSCin/OSCin*端口的VCXO配置为交流耦合单端驱动器。LD引脚可以编程为输出锁定检测信号,当锁定丢失时,拉低GOE引脚,使所有时钟输出禁用。

环路滤波器设计

每个PLL都需要一个专用的环路滤波器。PLL1的环路滤波器应连接到CPout1引脚,建议总闭环带宽在10 Hz至200 Hz范围内。PLL2的电荷泵直接连接到可选的内部环路滤波器组件,设计时应确保环路在VCO的整个应用特定调谐范围内稳定。

电源供应和热管理

建议将时钟输出的电源引脚连接到专用电源平面,其他电源引脚连接到第二个电源平面。由于设备的功耗可能较高,需要注意热管理,确保芯片温度不超过125 °C。可以通过在PCB上设计热焊盘和多个过孔到接地层,以及在PCB另一侧添加铜区域等方式来散热。

晶体振荡器实现

LMK04000系列支持离散实现的振荡器驱动OSCin端口引脚。在选择晶体时,需要指定总负载电容,该电容由调谐电容、OSCin引脚的输入电容和PCB的杂散电容组成。

时钟输出端接

在端接时钟驱动器时,应遵循传输线理论进行良好的阻抗匹配,以防止反射。不同类型的输出(LVDS、LVPECL、LVCMOS)有不同的端接方式,如LVDS驱动器需要闭合电流回路,LVPECL驱动器需要接地的直流路径等。

编程与配置

通用编程信息

LMK040xx设备使用多个32位寄存器进行编程。每个寄存器由4位地址字段和28位数据字段组成。编程时,LE信号应保持低电平,串行数据在CLK信号的上升沿时钟输入。编程完成后,CLKuWire、DATAuWire和LEuWire信号应返回低电平。

推荐编程顺序

推荐的编程顺序是先将R7的复位位设置为1,确保设备处于默认状态。然后按顺序编程寄存器,最后编程R15。

寄存器功能

各个寄存器控制着设备的不同功能,如时钟输出的分频、延迟、使能,PLL的参数设置,参考时钟的选择等。

总结

LMK04000系列时钟抖动清理器凭借其级联PLL架构、超低抖动性能、丰富的功能和广泛的应用领域,为电子工程师提供了一个强大的时钟解决方案。在设计过程中,需要根据具体应用需求合理配置寄存器、设计环路滤波器、处理电源和热管理等问题,以充分发挥该系列产品的优势。你在使用类似产品时遇到过哪些问题呢?欢迎在评论区分享交流。

-

高精度时钟

+关注

关注

0文章

9浏览量

5824

发布评论请先 登录

LMK04000系列时钟抖动清理器:高精度时钟解决方案

LMK04000系列时钟抖动清理器:高精度时钟解决方案

评论