在开始芯片测试流程之前应先充分了解芯片的工作原理。要熟悉它的内部电路,主要参数指标,各个引出线的作用及其正常电压。

芯片很敏感,所以测试的时候要注意不要引起引脚之间的短路,任何一瞬间的短路都能被捕捉到,从而造成芯片烧坏。本篇文章纳米软件小编将带大家全方位了解IC芯片测试流程及IC芯片自动化测试平台。

1、晶圆测试(wafertest)

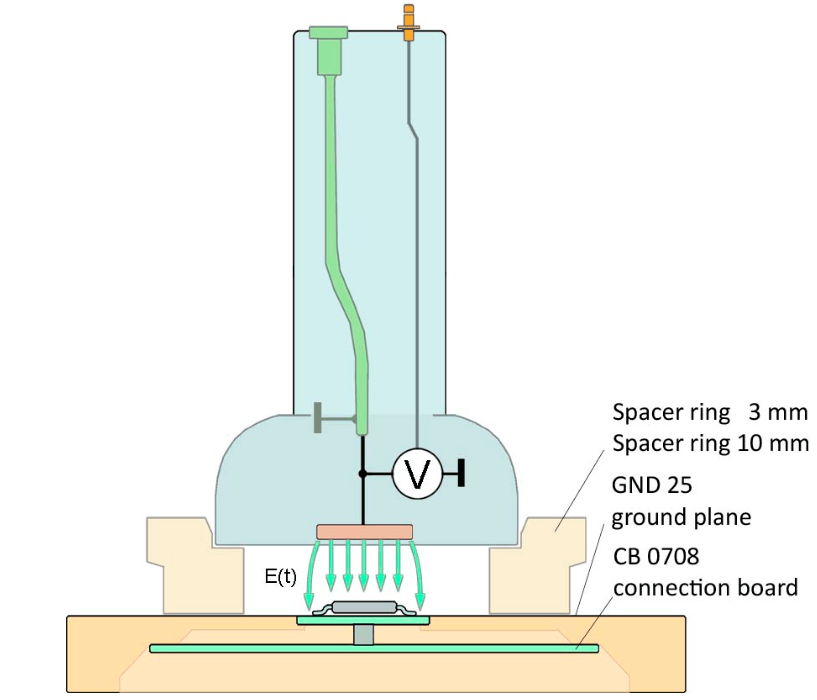

是在晶圆从晶圆厂生产出来后,切割减薄之前的测试。其设备通常是测试厂商自行开发制造或定制的,一般是将晶圆放在测试平台上,用探针探到芯片中事先确定的测试点,探针上可以通过直流电流和交流信号,可以对其进行各种电气参数测试。

2、芯片测试(chiptest)

是在晶圆经过切割、减薄工序,成为一片片独立的chip之后的测试。其设备通常是测试厂商自行开发制造或定制的,一般是将晶圆放在测试平台上,用探针探到芯片中事先确定的测试点,探针上可以通过直流电流和交流信号,可以对其进行各种电气参数测试。

chiptest和wafertest设备Z主要的区别是因为被测目标形状大小不同因而夹具不同。

3、封装测试(packagetest)

packagetest是在芯片封装成成品之后进行的测试。由于芯片已经封装,所以不再需要无尘室环境,测试要求的条件大大降低。

通常包含测试各种电子或光学参数的传感器,但通常不使用探针探入芯片内部(多数芯片封装后也无法探入),而是直接从管脚连线进行测试。由于packagetest无法使用探针测试芯片内部,因此其测试范围受到限制,有很多指标无法在这一环节进行测试。

不同芯片适用的测试

对于芯片面积大、良率高、封装成本低的芯片,通常可以不进行wafertest,而芯片面积小、良率低、封装成本高的芯片,Z好将很多测试放在wafertest环节,及早发现不良品,避免不良品混入封装环节,无谓地增加封装成本。

芯片的测试过程

芯片测试的过程是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

经一般测试合格的产品贴上规格、型号及出厂日期等标识的标签并加以包装后即可出厂。而未通过测试的芯片则视其达到的参数情况定作降级品或废品。

IC测试的设备,由于IC的生产量通常非常巨大,因此像万用表、示波器一类手工测试仪器是一定不能胜任的,目前的测试设备通常都是全自动化、多功能组合测量装置,并由程序控制,你基本上可以认为这些测试设备就是一台测量专用工业机器人。

芯片自动化测试平台

市面上芯片自动化测试系统五花八门,目前上市面上使用比较多的如ATECLOUD芯片自动测试平台。

使用ATECLOUD芯片自动测试系统整个过程只需1.5~2分钟即可完成芯片诸多参数的测试,而采集数据与报告导出只需15秒即可完成,相比人工手动测试和记录报告效率提升50-100倍,同时只需一个懂仪器操作的人员即可完成测试,极大节省了人力成本。

本文内容源于【IC测试之家】

-

集成电路

+关注

关注

5446文章

12469浏览量

372688 -

晶圆

+关注

关注

53文章

5345浏览量

131694 -

芯片测试

+关注

关注

6文章

156浏览量

21085

原文标题:深入掌握 IC 芯片的测试全过程

文章出处:【微信号:闪德半导体,微信公众号:闪德半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

电机驱动与控制专用集成电路及应用

中国集成电路大全 接口集成电路

科研分享|智能芯片与异构集成电路电磁兼容问题

硅集成电路技术的优势与挑战

集成电路为什么要封胶?

集成电路工艺中的金属介绍

探索集成电路的奥秘

集成电路新突破:HKMG工艺引领性能革命

集成电路制造中良率损失来源及分类

聚焦集成电路IC:掀起电子浪潮的 “芯片风暴”

集成电路封装的发展历程

集成电路电磁兼容性及应对措施相关分析(三)集成电路ESD 测试与分析

集成电路电磁兼容性及应对措施相关分析(三)—集成电路ESD 测试与分析

集成电路芯片的测试分类

集成电路芯片的测试分类

评论