该CDCU877是一款高性能、低抖动、低偏斜、零延迟缓冲器,可分配差分时钟输入 对(CK、CK)到十个差分时钟输出对(Yn、Yn)和一个差分对反馈时钟输出 (FBOUT,FBOUT)。时钟输出由输入时钟(CK、CK)、反馈时钟(FBIN、FBIN)、 LVCMOS 控制引脚(OE、OS)和模拟电源输入(AV DD ).当OE为低电平时,时钟输出,除了 FBOUT/FBOUT被禁用,而内部PLL继续保持其锁定频率。作系统(输出选择) 是必须连接到 GND 或 V 的程序引脚 DD .当作系统为高电平时,OE 功能如前所述。什么时候 OS和OE都较低,OE对Y7/Y7没有影响,它们是自由运行的。当 AVDD接地,PLL 接动 关闭并绕过测试目的。

*附件:cdcu877a.pdf

当两个时钟输入(CK、CK)逻辑低电平时,器件进入低功耗模式。输入逻辑检测电路 在差分输入上,独立于输入缓冲器,检测逻辑低电平并在低功耗状态下运行 其中所有输出、反馈和 PLL 均处于关闭状态。当时钟输入从逻辑低电平转换为逻辑低电平 差分信号,PLL 重新导通,输入和输出使能,PLL 获得锁相 反馈时钟对(FBIN、FBIN)和时钟输入对(CK、CK)在规定的稳定时间内。

该CDCU877能够跟踪扩频时钟 (SSC) 以降低 EMI。该器件工作温度范围为 -40°C 至 85°C。

特性

- 用于双倍数据速率 (DDR II) 应用的 1.8V 锁相环时钟驱动器

- 兼容扩频时钟

- 工作频率:10 MHz 至 400 MHz

- 低电流消耗:<135 mA

- 低抖动(周期-周期):±30 ps

- 低输出偏斜:35 ps

- 低周期抖动:±20 ps

- 低动态相位偏移:±15 ps

- 低静态相位偏移:±50 ps

- 将一个差分时钟输入分配给十个差分输出

- 52 引脚 μBGA(MicroStar™ Junior BGA,0.65 mm 间距)和 40 引脚 MLF

- 外部反馈引脚(FBIN、FBIN)用于将输出与输入时钟同步

- 达到或超过PC2-3200/4300的JESD82-8 PLL标准

- 故障安全输入

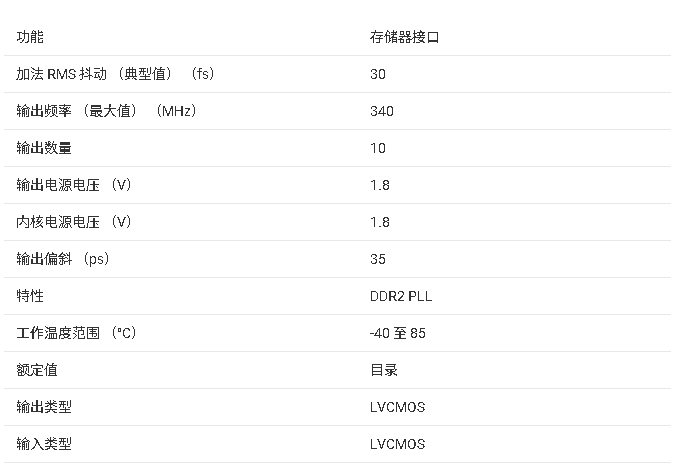

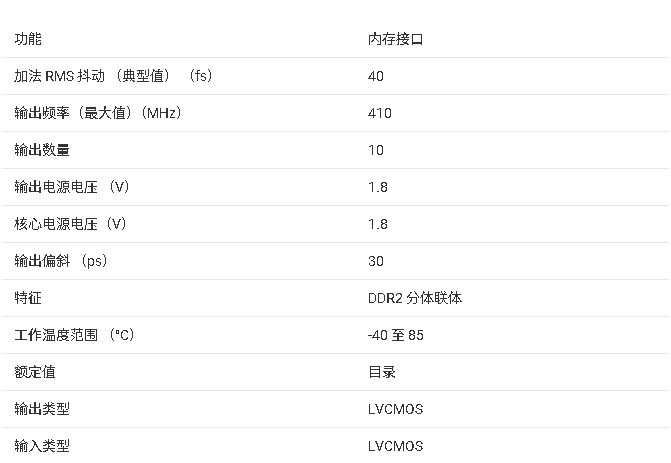

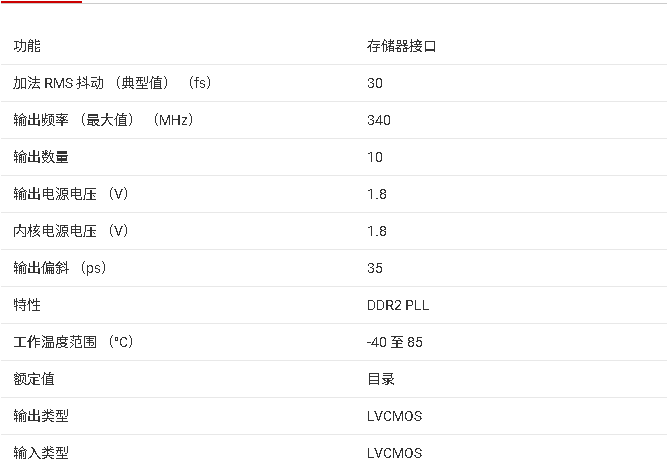

参数

1. 产品概述

- 型号:CDCU877/CDCU877A,德州仪器(TI)推出的高性能锁相环(PLL)时钟驱动器,专为DDR II应用设计。

- 核心功能:将1对差分时钟输入(CK/CK)分配至10对差分时钟输出(Yn/Yn)和1对反馈输出(FBOUT/FBOUT),支持零延迟缓冲和低抖动/低偏移特性。

- 兼容性:符合JESD82-8标准(PC2-3200/4300),支持扩频时钟(SSC)以减少电磁干扰(EMI)。

2. 关键特性

- 电气性能:

- 工作频率:10 MHz至400 MHz(锁相范围),应用频率160-340 MHz。

- 低功耗:静态电流<135 mA,动态电流235 mA(典型值)。

- 低抖动:周期抖动±30 ps,静态相位偏移±50 ps,动态相位偏移±15 ps。

- 输出偏斜:35 ps(最大)。

- 封装选项:

- 52球μBGA(0.65 mm间距)和40引脚MLF封装,工作温度-40°C至85°C。

3. 功能控制

- 控制引脚:

- OE(输出使能):低电平时禁用输出(FBOUT除外),PLL保持锁定。

- OS(输出选择):高电平时OE正常生效;低电平时Y7/Y7自由运行。

- AVDD:接地时PLL关闭(测试模式)。

- 低功耗模式:当CK/CK均为逻辑低时,进入省电状态,关闭所有输出和PLL。

4. 时序与稳定性

- 锁定时序:上电或退出省电模式后,PLL稳定时间≤12 μs。

- 抖动指标:

- 周期抖动:±20 ps(190-340 MHz)。

- 半周期抖动:±40 ps(250-300 MHz)。

5. 应用设计建议

- 布局优化:推荐AVDD电源滤波方案(4.7 μF+0.1 μF+2200 pF电容组合),靠近PLL放置。

- 信号完整性:输入/输出差分对需匹配走线长度,建议斜率≥2.5 V/ns以减少静态相位偏移。

6. 订购信息

- 提供多种型号后缀(如ZQL、RHA等),对应不同封装和温度范围,具体参见文档末尾的封装选项附录。

7. 注意事项

- ESD防护有限,存储时需短路引脚或使用导电泡沫。

- 生产数据以发布日为准,参数可能因测试条件差异而变动。

-

锁相环

+关注

关注

36文章

633浏览量

90817 -

缓冲器

+关注

关注

6文章

2215浏览量

48681 -

时钟输出

+关注

关注

0文章

11浏览量

5810 -

LVCMOS

+关注

关注

1文章

142浏览量

11945 -

时钟驱动器

+关注

关注

0文章

96浏览量

14345

发布评论请先 登录

CDCUA877 1.8V锁相环时钟驱动器技术文档总结

CDCU877 用于DDR2 SDRAM应用的1.8V锁相环时钟驱动器技术手册

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结

CDCVF25081 3.3-V 锁相环时钟驱动器技术文档总结

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDC2536 锁相环时钟驱动器技术文档总结

CDCU877/CDCU877A 1.8V锁相环时钟驱动器技术文档总结

CDCU877/CDCU877A 1.8V锁相环时钟驱动器技术文档总结

评论