该LMK00725是一款低偏斜、高性能时钟扇出缓冲器,可从两个输入之一分配多达五个3.3V LVPECL输出,该输入可接受差分或单端输入。时钟使能输入在内部同步,以消除时钟使能引脚置位或取消置位时输出上的欠幅或毛刺脉冲。低附加抖动和相位本底噪声以及确保的输出和器件间偏斜特性使该LMK00725成为需要高性能和可重复性的应用的理想选择。

*附件:lmk00725.pdf

特性

- 5个3.3V差分LVPECL输出

- 附加抖动:43 fs RMS(典型值)@ 312.5 MHz

- 本底噪声(≥1 MHz 偏移):

–158 dBc/Hz(典型值)@ 312.5 MHz - 输出频率:650 MHz(最大值)

- 输出偏斜:35 ps(最大值)

- 零件间偏斜:100 ps(最大值)

- 传播延迟:0.37 ns(最大值)

- 两个差分输入对(引脚可选)

- CLKx、nCLK输入对可以接受LVPECL、LVDS、

HCSL、SSTL、LVHSTL或单端

信号

- CLKx、nCLK输入对可以接受LVPECL、LVDS、

- 同步时钟使能

- 电源:3.3V ±5%

- 封装:20引脚TSSOP

- 工业温度范围:–40°C 至 +85°C

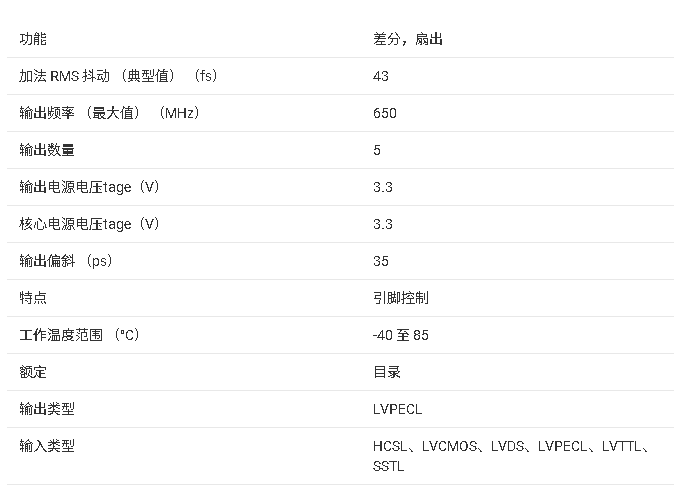

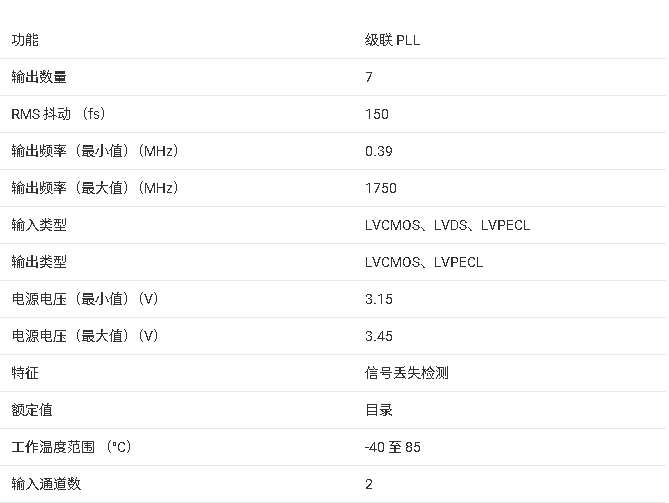

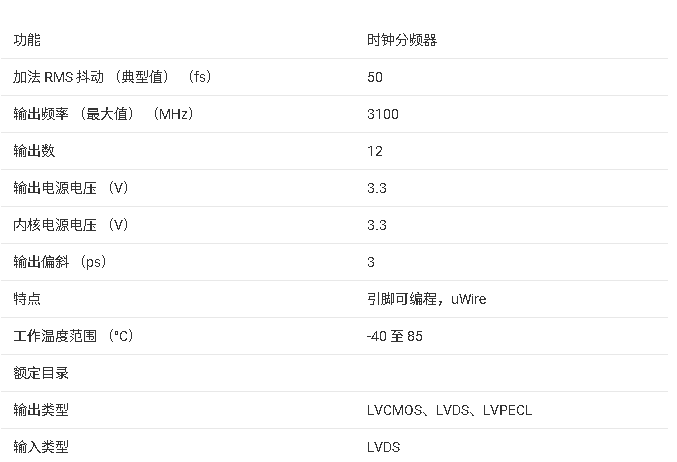

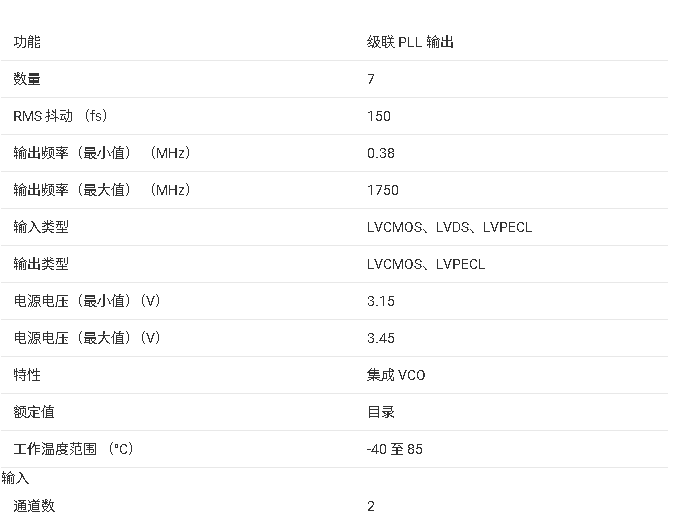

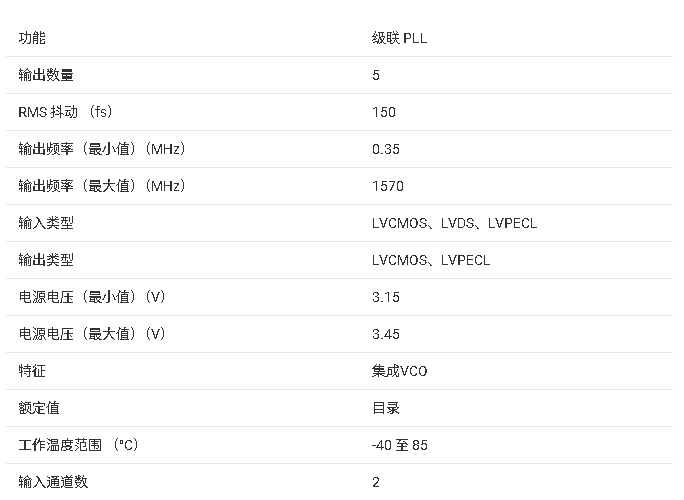

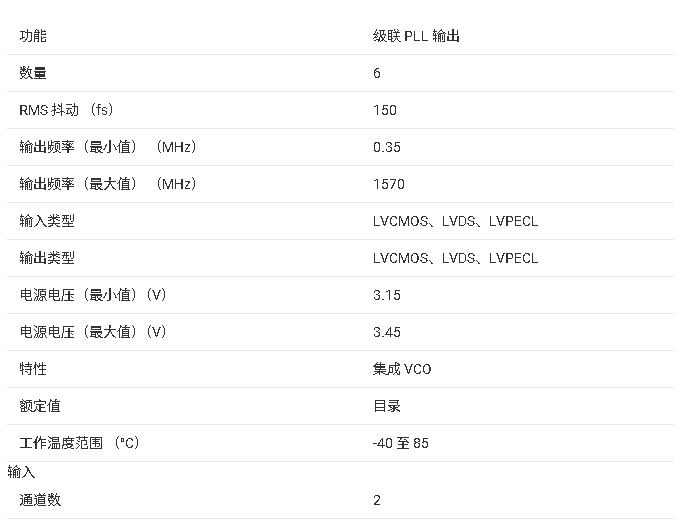

参数

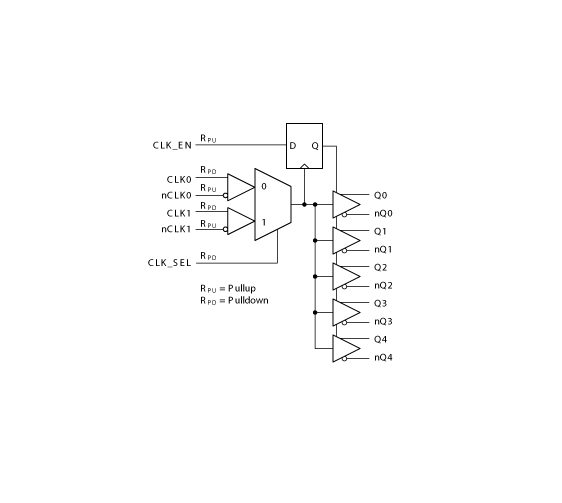

方框图

1. 产品概述

LMK00725是德州仪器(TI)推出的高性能低偏移时钟扇出缓冲器,可将1路差分输入转换为5路3.3V LVPECL输出,适用于对时序精度要求严苛的应用场景。其核心特性包括:

- 超低抖动:典型附加抖动43 fs RMS(312.5 MHz时)

- 低噪声:噪声底限-158 dBc/Hz(1 MHz偏移)

- 高频率支持:最大输出频率650 MHz

- 低延迟:最大传播延迟0.37 ns

- 宽温支持:工业级温度范围(-40°C至+85°C)

2. 关键特性

- 输入灵活性:支持LVPECL、LVDS、HCSL、SSTL等多种差分或单端输入信号

- 同步使能:时钟使能(CLK_EN)功能可消除输出端的毛刺

- 低偏移控制:输出偏移最大35 ps,器件间偏移最大100 ps

- 封装:20引脚TSSOP封装

3. 典型应用

- 无线/有线通信基础设施

- 网络与数据通信设备

- 服务器及高性能计算

- 医疗成像设备

- 高端音视频系统

4. 功能架构

- 双差分输入通道(CLK0/nCLK0、CLK1/nCLK1),通过CLK_SEL引脚选择

- 五组LVPECL输出对(Q0/nQ0至Q4/nQ4)

- 内部集成同步使能逻辑和输入偏置电阻(RPU/RPD)

5. 电气特性

6. 设计注意事项

- 热管理:建议通过多层PCB、增加铜厚和散热过孔控制结温

- 电源滤波:推荐每电源引脚配置0.1μF去耦电容,必要时添加磁珠隔离

- 未用引脚处理:输入引脚需按规范偏置,输出引脚可悬空或端接

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

缓冲器

+关注

关注

6文章

2236浏览量

49050 -

引脚

+关注

关注

16文章

2120浏览量

56025 -

偏置电阻

+关注

关注

1文章

44浏览量

8902 -

LVPECL

+关注

关注

2文章

77浏览量

18900

发布评论请先 登录

相关推荐

热点推荐

当LMK00725的输入为LVPECL电平时,由于芯片输入管脚内部存在51KOhm上下拉,在芯片外部是否还需要增加上下拉偏置电阻呢?

请教一个问题,当LMK00725的输入为LVPECL电平时,由于芯片输入管脚内部存在51KOhm上下拉,那在芯片外部是否还需要增加上下拉偏置电阻呢?

我目前参考的是手册中的典型应用电

发表于 11-11 07:07

LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?

您好,目前我正在使用LMK05318+LMK00725的方案进行≥10路的时钟生成与FANOUT;前者LMK05318的LVDS与LVPECL输出均为AC耦合,

而LMK00725手册中

发表于 11-11 07:42

基于JESD204B的LMK04821芯片项目开发

LMK0482X系列是德州仪器推出的高性能时钟调节芯片系列,该芯片目前有三种,分别为LMK04821、LMK04826以及

LMK00725低电压正射极耦合逻辑(LVPECL)扇出缓冲器数据表

电子发烧友网站提供《LMK00725低电压正射极耦合逻辑(LVPECL)扇出缓冲器数据表.pdf》资料免费下载

发表于 08-23 11:16

•0次下载

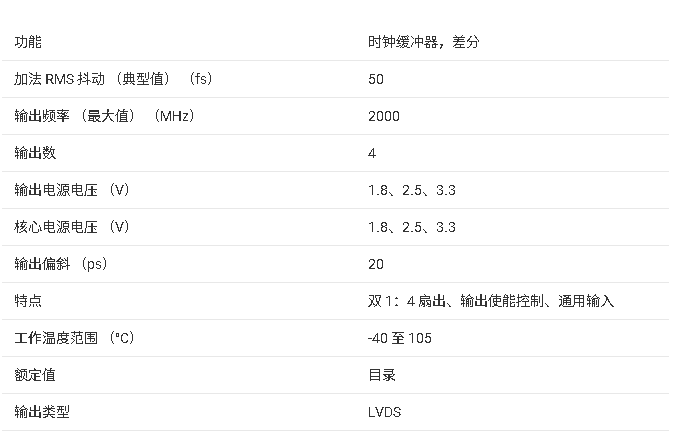

LMK1D2104L 系列超低附加抖动LVDS缓冲器技术文档总结

LMK1D210xL 是一款低噪声双时钟缓冲器,可将一个输入分配给最多 2 (LMK1D2102L)、4 (LMK1D2104L)、6 (LMK1D2106L) 或 8 (

LMK1D210xL系列超低附加抖动LVDS缓冲器技术文档总结

LMK1D210xL 是一款低噪声双时钟缓冲器,可将一个输入分配给最多 2 (LMK1D2102L)、4 (LMK1D2104L)、6 (LMK1D2106L) 或 8 (

LMK05318B-Q1 芯片技术文档总结

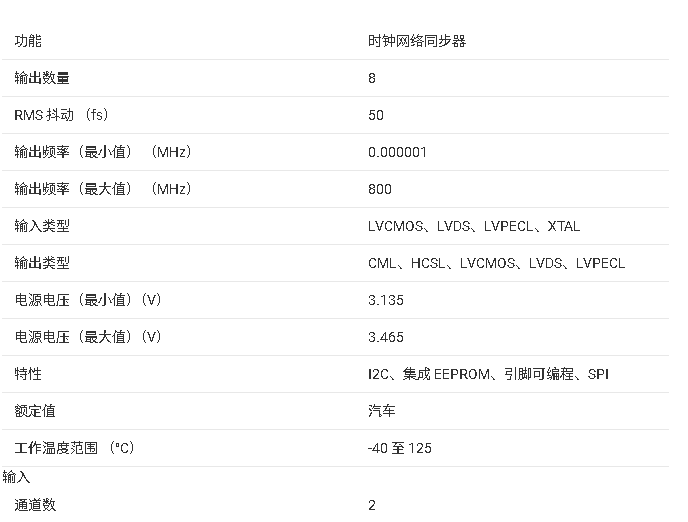

LMK05318B-Q1 是高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格定时要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

LMK04906 超低噪声时钟抖动消除器与倍频器技术文档总结

该LMK04906是业界性能最高的时钟抖动衰减器,具有卓越的时钟抖动清除、生成和分配功能,具有先进的功能,可满足高性能时序应用需求。

该LMK04906接受 3 个 1 kHz 至 500

LMK04111芯片技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

LMK04131 抖动清除器技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

LMK04102 抖动清除器技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

LMK01801双时钟分频缓冲器技术文档总结

该LMK01801是一种非常低噪声的解决方案,适用于需要精密时钟分配和频分的时钟系统。

该LMK01801具有极低的残余噪声、频分、数字和模拟延迟调节以及十四 (14) 个可编程差分输出:LVPECL、LVDS 和 LVCMOS(每个差分输出 2 个输出)。

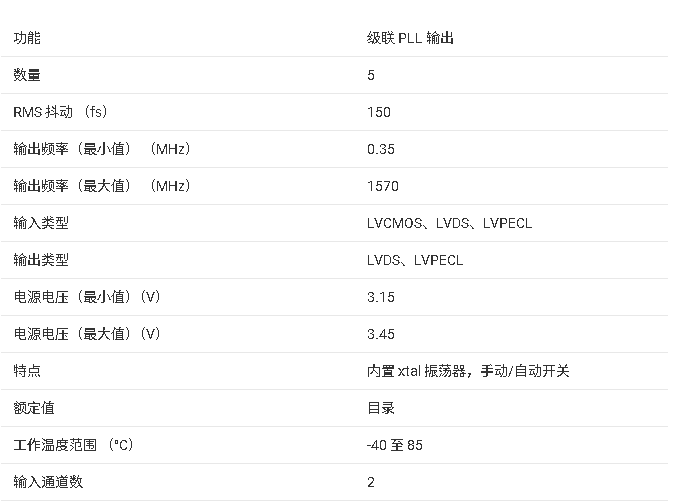

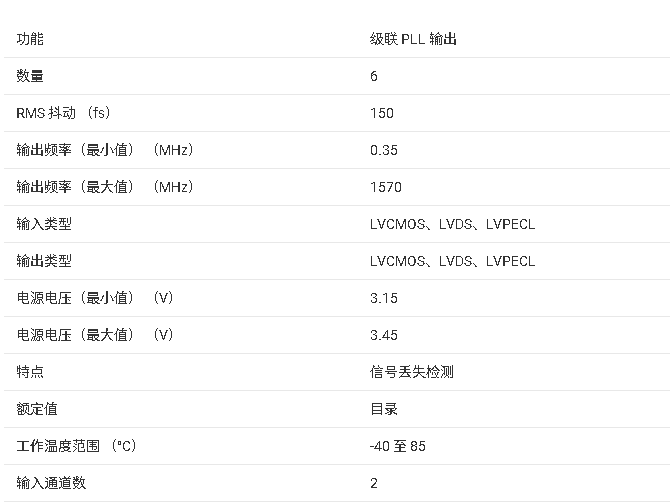

LMK04000系列低噪声时钟抖动清除器技术文档总结

LMK04000系列精密时钟调节器提供低噪声抖动清除、时钟乘法和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

LMK04011 低噪声时钟抖动清除器技术文档总结

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

LMK04031 低噪声时钟抖动清除器技术文档总结

LMK04000系列精密时钟调理器提供低噪声抖动清除、时钟倍增和分配,无需高性能压控晶体振荡器 (VCXO) 模块。LMK04000 系列采用级联 PLLatinum 架构,结合外部晶体和变容二极管,提供低于 200 飞秒 (fs) 的均方根 (RMS) 抖动性能。

LMK00725 芯片技术文档总结

LMK00725 芯片技术文档总结

评论