LMK05318B-Q1 是高性能网络同步器时钟器件,可提供抖动清除、时钟生成、高级时钟监控和卓越的无中断开关性能,以满足通信基础设施和工业应用的严格定时要求。该器件的超低抖动和高电源噪声抑制 (PSNR) 可降低高速串行链路中的误码率 (BER)。

*附件:lmk05318b-q1.pdf

特性

- 符合 AEC-Q100 标准,适用于汽车应用

- 温度等级 2:–40°C 至 105°C

- 基于超低抖动 BAW VCO 的以太网时钟

- 312.5MHz时为50fs典型RMS抖动

- 156.25MHz时为60fs典型RMS抖动

- 一个高性能数字锁相环 (DPLL) 与两个模拟锁相环 (APLL) 配对:

- 可编程 DPLL 环路带宽

- < 1 ppt DCO 频率调整步长

- 两个差分或单端 DPLL 输入

- 1Hz (1-PPS) 至 800MHz 输入频率

- 数字保持和无中断开关

- 八个差分输出,具有可编程 HSDS/LVPECL、LVDS、HSCL 和 1.8V LVCMOS 输出格式。

- 多达六个不同的输出频率

- 1Hz (1-PPS) 至 1250MHz 输出频率

- 符合 PCIe Gen 1 至 6 标准

- I2C 或 SPI 寄存器控制总线

- EEPROM 用于启动时的自定义系统配置

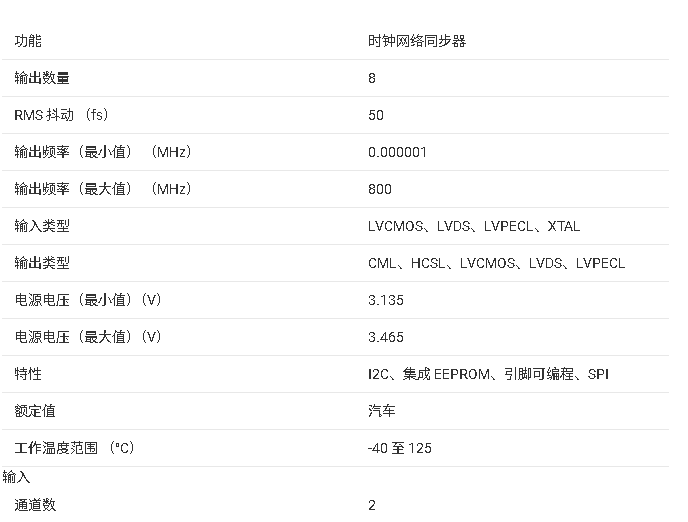

参数

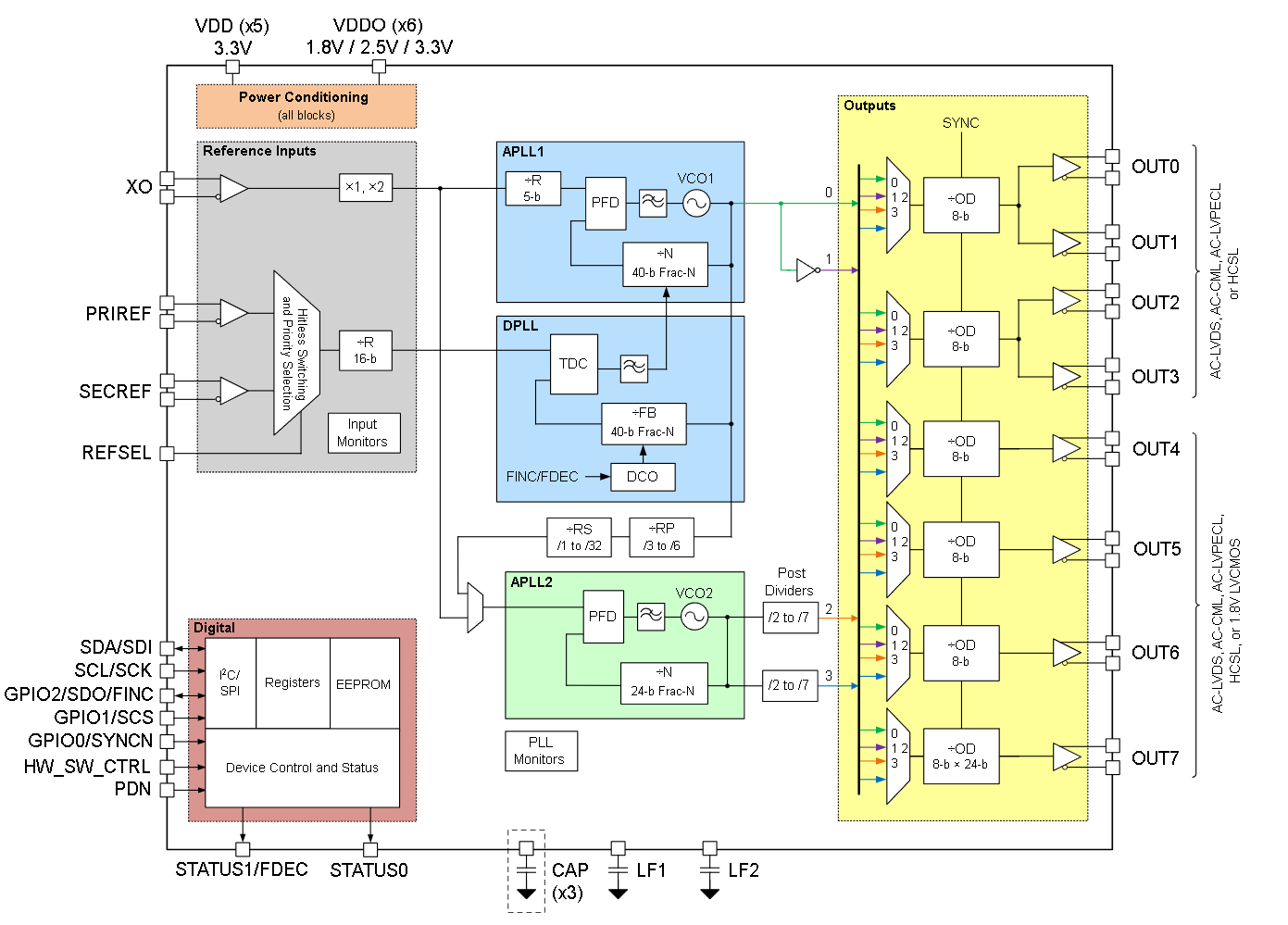

方框图

1. 产品概述

LMK05318B-Q1 是德州仪器(TI)推出的超低抖动网络同步器和时钟发生器,专为汽车及工业应用设计,集成BAW VCO技术。关键特性包括:

- AEC-Q100汽车级认证(-40°C至105°C工作温度)

- 超低抖动性能:典型RMS抖动50fs@312.5MHz,60fs@156.25MHz

- 多PLL架构:1个数字PLL(DPLL)+2个模拟PLL(APLL),支持可编程带宽和<1ppt频率调节步进

- 输入/输出灵活性:2路差分/单端参考输入(1Hz至800MHz),8路差分输出(支持LVDS/LVPECL/HCSL/1.8V LVCMOS,最高1250MHz)

2. 主要应用场景

- 高速通信:56G/112G PAM-4 PHY、ASIC/FPGA/SoC时钟生成

- 汽车电子:ADAS传感器融合、车载信息娱乐系统(Infotainment)、区域控制器

- 网络同步:SyncE(G.8262)、SONET/SDH(Stratum 3)、IEEE 1588 PTP二级时钟

- 测试与医疗设备:高精度时钟需求场景

3. 核心功能模块

- 时钟输入:支持XO/TCXO/OCXO输入(10-100MHz),双参考输入(PRIREF/SECREF)

- PLL系统:

- 输出管理:8路可编程输出,支持同步(SYNC)和自动静音(Auto-Mute)

4. 关键性能参数

- 电源要求:核心电压3.3V,输出电源1.8V/2.5V/3.3V可选

- 相位噪声:

- APLL1输出:50fs RMS(12kHz-20MHz,625MHz)

- APLL2输出:130fs RMS(级联模式)

- 封装:48引脚VQFN(7mm×7mm),带裸露焊盘散热

5. 控制与配置

- 接口:支持I2C/SPI控制,内置EEPROM存储自定义配置

- 监控功能:输入时钟质量检测(幅度/频率/脉冲丢失)、PLL锁相状态指示

- DCO模式:支持<0.001ppb步进的精密频率调节,适用于IEEE 1588时钟同步

6. 设计支持

- 推荐使用TICS Pro软件生成寄存器配置

- 提供热优化布局指南(如5×5过孔阵列接地)

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟器件

+关注

关注

0文章

16浏览量

8233 -

同步器

+关注

关注

1文章

117浏览量

15702 -

噪声抑制

+关注

关注

0文章

36浏览量

12542 -

串行链路

+关注

关注

0文章

13浏览量

8392

发布评论请先 登录

相关推荐

热点推荐

LMK05318是否可以对Switch输出的1588 clock进行同步锁频、锁相?

我们现在想做一个相对简化的1588同步方案,打算使用TI的LMK05318这个方案,有以下几个问题需要咨询

下图是我们方案的框图,我们的目的是使这样的N个设备通过1588同步起来

我个人的理解

发表于 11-08 10:50

LMK05318配置0x65.tcs,得出的OUT2和OUT4端口均无输出,为什么?

按照如下文件的TICS Pro软件配置:

LMK05318配置0x65.tcs

但是得出的OUT2和OUT4端口均无输出,其余端口正常,下面是电路原理图:

请问一下是否是我的配置错误,导致OUT2和OUT4无输出信号。

发表于 11-11 07:40

LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?

您好,目前我正在使用LMK05318+LMK00725的方案进行≥10路的时钟生成与FANOUT;前者LMK05318的LVDS与LVPECL输出均为AC耦合,

而LMK00725手册中

发表于 11-11 07:42

LMK05318在TICS Pro中怎样设置,可以加快同步的速度,实现几分钟之内相位同步?

使用芯片LMK05318,参考输入1PPS,目标输出1PPS和6路2MHz时钟与参考输入同步。参考1PPS来自GPS接收模块。目前测试发现

发表于 11-12 06:46

BAW谐振器技术的优势

什么是BAW技术?BAW谐振器技术的优势TI 突破性BAW技术芯片无外置石英晶振的无线MCU——CC2652RB网络同步器时钟——LMK05318

发表于 01-25 06:59

LMK04832-SP时钟抖动清除器

-8191 SYSREF分频器SYSREF时钟的25ps步进模拟延迟设备时钟和SYSREF的数字延迟和动态数字延迟PLL1的保持模式PLL1或PLL2的0延迟环境温度范围:–55°C至125°CLMK5C33216LMK04816LMK

发表于 03-24 16:13

LMK05318的ITU-T G.8262一致性测试结果

电子发烧友网站提供《LMK05318的ITU-T G.8262一致性测试结果.pdf》资料免费下载

发表于 09-20 11:21

•0次下载

LMK00725 芯片技术文档总结

该LMK00725是一款低偏斜、高性能时钟扇出缓冲器,可从两个输入之一分配多达五个3.3V LVPECL输出,该输入可接受差分或单端输入。时钟使能输入在内部同步,以消除时钟使能引脚置位或取消置位

LMK04111芯片技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

LMK05318B-Q1:高性能网络同步器的深度解析

LMK05318B-Q1:高性能网络同步器的深度解析 在当今高速发展的电子领域,以太网网络应用对时钟同步和抖动控制提出了极高要求。LMK05318B-Q1作为一款高性能网络同步器和抖动清理器,专为

探索LMK05318B:以太网网络同步的卓越之选

探索LMK05318B:以太网网络同步的卓越之选 在当今高速发展的以太网网络应用领域,对于高性能网络同步器和抖动清除器的需求日益增长。LMK05318B作为一款专为满足以太网网络应用严格要求而设

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器

LMK00804B-Q1:高性能时钟扇出缓冲器与电平转换器 在电子设计领域,时钟信号的精确分配和转换至关重要。今天要给大家介绍的是德州仪器(TI)的 LMK00804B-Q1,一款高性能的时钟扇出

深入解析LMK05318:高性能网络同步器的强大功能与应用实践

,凭借其卓越的性能和丰富的功能,成为众多工程师的首选。今天,我们就来深入剖析LMK05318的特点、应用以及设计要点。 文件下载: lmk05318.pdf 一、LMK05318的核心特性 1

LMK05318B-Q1 芯片技术文档总结

LMK05318B-Q1 芯片技术文档总结

评论