声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADI

+关注

关注

151文章

46125浏览量

280759 -

pll

+关注

关注

6文章

990浏览量

138376 -

杂散信号

+关注

关注

1文章

5浏览量

7375

发布评论请先 登录

相关推荐

热点推荐

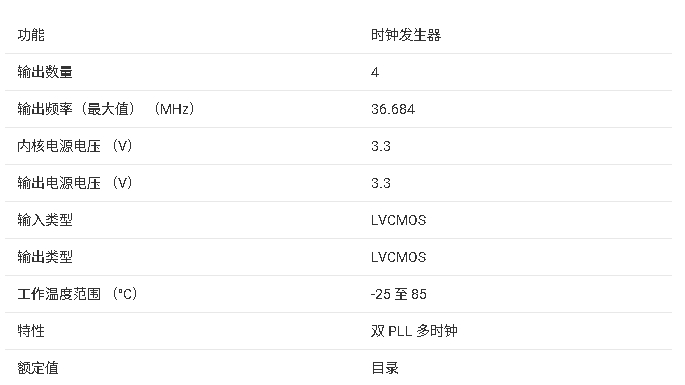

PLL1707/PLL1708 双PLL多时钟发生器技术文档总结

PLL1707成本低、锁相 环路 (PLL) 多时钟发生器。PLL1707和 PLL1708可以从 27 MHz 生成四个系统时钟 参考输入频率

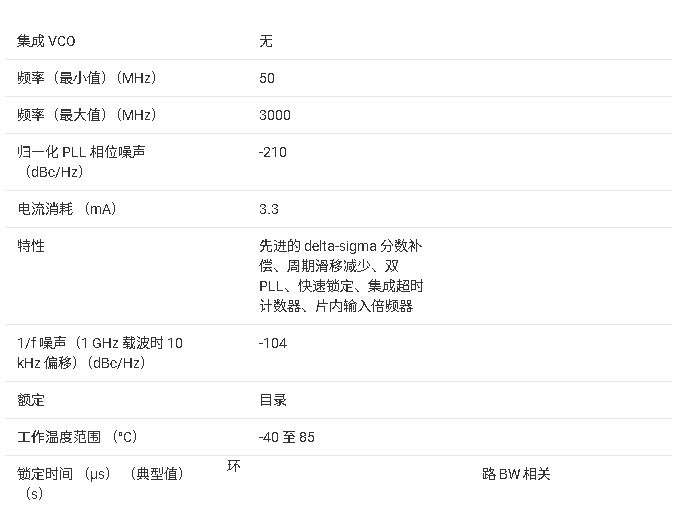

LMX2485E 用于射频个人通信的 50 MHz 至 3 GHz Δ-Σ 低功耗双通道 PLL技术手册

架构,在较低失调频率下推动分数杂散 到环路带宽之外的更高频率。能够接近杂散噪声和相位噪声 能量

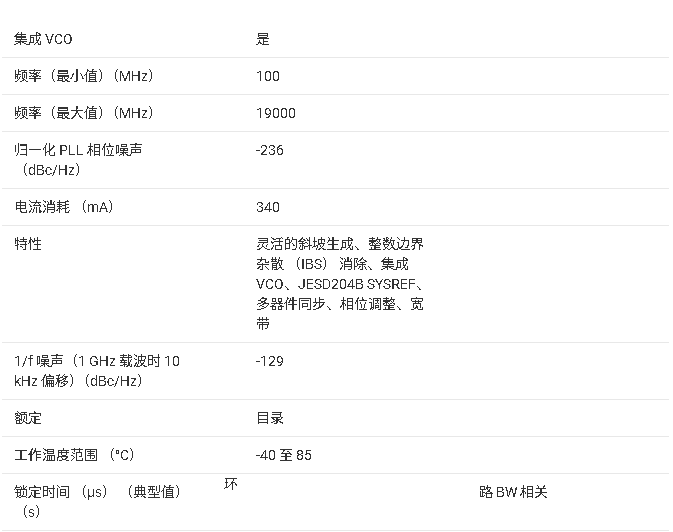

LMX2595 20-GHz宽带PLLATINUM™射频合成器技术文档总结

LMX2595高性能宽带合成器,可生成 10 MHz 至 20 GHz 的任何频率。集成倍频器用于 15 GHz 以上的频率。具有–236 dBc/Hz品质因数和高相位检测器频率的高性

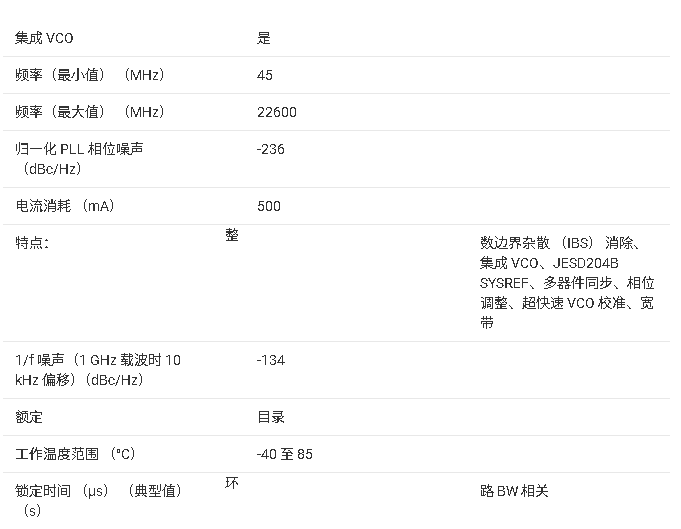

LMX2820 22.6 GHz宽带PLLatinum™射频合成器技术文档总结

和集成抖动。高速N分频器没有预分频器,因此显著降低了杂散的幅度和数量。还有一个可编程输入乘法器,用于减轻整数边界杂散。

原厂方案:利用力科示波器设置PLL参数

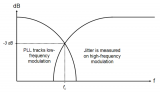

。由锁相环(PLL)跟踪到的低频率信号边缘变化不被视为抖动,因为它们被PLL有效去除。相反,没有被PLL跟踪到的高

发表于 06-05 19:29

•864次阅读

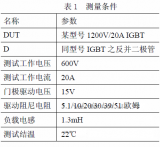

IGBT功率模块动态测试中夹具杂散电感的影响

在IGBT功率模块的动态测试中,夹具的杂散电感(Stray Inductance,Lσ)是影响测试结果准确性的核心因素。杂散电感由测试夹具的layout、材料及连接方式引入,会导致开关

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc

电子发烧友网为你提供()无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器相关产品参数、数据手册,更有无杂散、50 M

发表于 05-23 18:30

ADC采样率与信号频率:关键概念与设计要点

在模数转换器(ADC)的设计与应用中,采样率与信号频率的关系是影响系统性能的核心因素。采样率是指ADC对模拟输入进行采样的速度,通常由外部时钟或内部锁相环(PLL)提供。现代高速ADC常采用

发表于 05-13 09:53

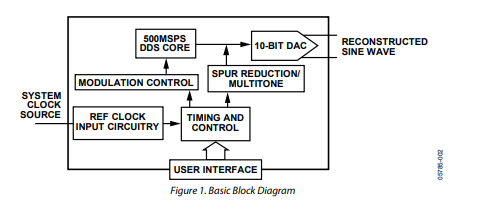

AD9911 500 MSPS直接数字频率合成器,内置10位DAC技术手册

AD9911是一款完整的直接数字频率合成器(DDS)。该器件内置具有出色宽带和窄带无杂散动态范围(SFDR)以及三个辅助DDS内核的高速DAC,而未分配数模转换器(DAC)。这些辅助通道用于

杂散电感对IGBT开关过程的影响(2)

为验证对主回路杂散电感效应的分析并考察不同电感量以及门极驱动情况下的实际情况,我们人为对Lp 大小进行了干预,其具体方法是在D 的阴极与电路PCB 之间(即Lp2 与Lc1之间)加入长度可调的导线,用试凑办法得到期望的附加电感量。

用于杂散信号消除的PLL频率规划

用于杂散信号消除的PLL频率规划

评论