PLL1707成本低、锁相 环路 (PLL) 多时钟发生器。PLL1707和 PLL1708可以从 27 MHz 生成四个系统时钟 参考输入频率。的时钟输出 PLL1707可以通过采样频率控制来控制 引脚和PLL1708的引脚可以通过 串行模式控制引脚。该设备为客户提供 通过消除外部 组件并使客户能够实现非常 高性能音频所需的低抖动性能 DAC 和/或 ADC。PLL1707和PLL1708是理想的 适用于使用 27 MHz 主站的 MPEG-2 应用 时钟,例如 DVD 刻录机、HDD 刻录机、DVD 用于多媒体 PC、数字高清电视系统的附加卡、 和机顶盒。

*附件:pll1708.pdf

特性

- 27 MHz主时钟输入

- 生成的音频系统时钟 (PLL1707):

- SCKO0:768 华氏度

S(fS= 44.1 kHz) - SCKO1:768 华氏度

S, 512 楼S(fS= 48 kHz) - SCKO2:256 华氏度

S(fS= 32、44.1、48、64、88.2、96 kHz) - SCKO3:384 华氏度

S(fS= 32、44.1、48、64、88.2、96 kHz)

- SCKO0:768 华氏度

- 生成的音频系统时钟 (PLL1708):

- SCKO0:768 华氏度

S(fS= 44.1 kHz) - SCKO1:768 华氏度

S, 512 楼S, 384 楼S, 256 楼S(fS= 48 kHz) - SCKO2:256 华氏度

S(fS= 16、22.05、24、32、44.1、48、64、88.2、96 kHz) - SCKO3:384 华氏度

S(fS= 16、22.05、24、32、44.1、48、64、88.2、96 kHz)

- SCKO0:768 华氏度

- 零 PPM 误差输出时钟

- 低时钟抖动:50 ps(典型值)

- 多采样频率 (PLL1707):

- f

S= 32、44.1、48、64、88.2、96 kHz

- f

- 多采样频率 (PLL1708):

- f

S= 16、22.05、24、32、44.1、48、64、88.2、96 kHz

- f

- 3.3V 单电源

- PLL1707:并行控制

PLL1708:串行控制 - 封装:20引脚SSOP (150 mil),无铅产品

- 应用

- HDD + DVD刻录机

- DVD刻录机

- 硬盘录像机

- DVD播放机

- 用于多媒体 PC 的 DVD 附加卡

- 数字高清电视系统

- 机顶盒

参数

1. 产品概述

- 型号:PLL1707(并行控制)与PLL1708(串行控制),基于相同芯片设计,电气特性一致,仅控制模式不同。

- 核心功能:从27 MHz主时钟生成4个系统时钟(SCKO0-3)和2个缓冲27 MHz时钟(MCKO1-2),专为音频系统设计。

- 优势:零PPM误差、低抖动(典型50 ps)、支持多种采样频率,节省外部元件成本。

2. 关键特性

- 时钟输出配置:

- SCKO0:固定768×fS(如fS=44.1 kHz时为33.8688 MHz)。

- SCKO1:可编程为768×fS、512×fS(PLL1708额外支持384×fS、256×fS)。

- SCKO2/SCKO3:分别输出256×fS和384×fS,支持16-96 kHz采样率(PLL1708覆盖更广)。

- 采样频率支持:

- PLL1707:32/44.1/48/64/88.2/96 kHz。

- PLL1708:扩展至16/22.05/24 kHz等半采样频率。

- 电源与封装:3.3 V单电源供电,20引脚SSOP封装(符合RoHS)。

3. 控制模式差异

4. 应用场景

- 典型设备:DVD/HDD录像机、数字HDTV、机顶盒、多媒体PC扩展卡。

- 核心价值:为MPEG-2编解码器、音频DAC/ADC提供低抖动时钟,替代外部元件。

5. 电气与可靠性

- 工作温度:-25°C至85°C。

- ESD防护:需严格遵循防静电操作规范。

- 启动时间:典型3 ms至稳定输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dac

+关注

关注

44文章

2684浏览量

196401 -

pll

+关注

关注

6文章

976浏览量

137585 -

时钟发生器

+关注

关注

1文章

268浏览量

69885 -

引脚

+关注

关注

16文章

2088浏览量

55136 -

串行模式

+关注

关注

0文章

2浏览量

6798

发布评论请先 登录

相关推荐

热点推荐

基于FPGA 的新的DDS+PLL时钟发生器

针对直接数字频率合成(DDS)和集成锁相环(PLL)技术的特性,提出了一种新的DDS 激励PLL 系统频率合成时钟发生器方案。且DDS 避免正弦查找表,即避免使用ROM,采用滤波的方法

发表于 12-14 10:22

•36次下载

评估低抖动PLL时钟发生器的电源噪声抑制性能

评估低抖动PLL时钟发生器的电源噪声抑制性能

本文介绍了电源噪声对基于PLL的时钟发生器的干扰,并讨论了几种用于评估确定性抖动(DJ)的技术

发表于 09-18 08:46

•1840次阅读

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

概述

MAX3625B是一款低抖动、精密时钟发生器,优化用于网络设备。器件内置晶体振荡器和锁相环(

发表于 03-01 08:56

•1598次阅读

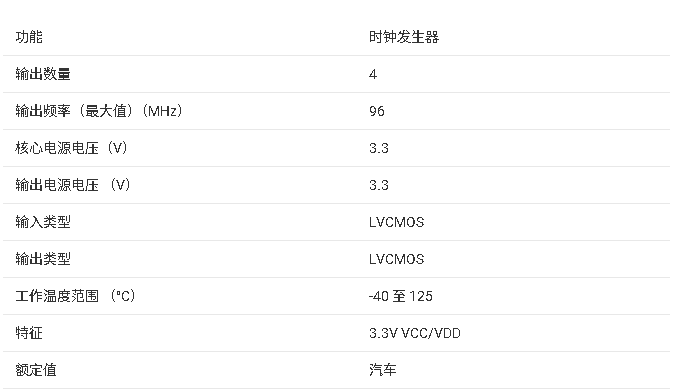

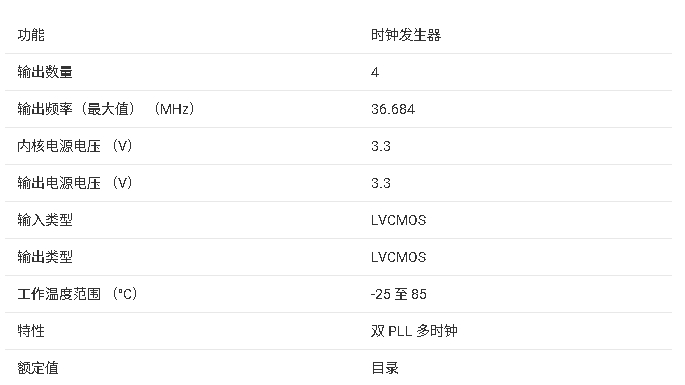

PLL1708 3.3V 双路 PLL 多时钟发生器

电子发烧友网为你提供TI(ti)PLL1708相关产品参数、数据手册,更有PLL1708的引脚图、接线图、封装手册、中文资料、英文资料,PLL1708真值表,PLL1708管脚等资料,

发表于 11-02 19:33

HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表

HMC1031:0.1 MHz至500 MHz时钟发生器,带整数N PLL数据表

发表于 04-23 20:15

•6次下载

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

AD9573:PCI-Express时钟发生器IC,PLL内核,分频器,双输出数据表

发表于 05-08 20:05

•5次下载

评估低抖动PLL时钟发生器的电源噪声抑制

本文讨论电源噪声干扰对基于PLL的时钟发生器的影响,并介绍几种用于评估由此产生的确定性抖动(DJ)的测量技术。派生关系显示了如何使用频域杂散测量来评估时序抖动行为。实验室台架测试结果用于比较测量

时钟发生器由哪些部分组成?锁相环pll的特点是什么?

时钟发生器由哪些部分组成?锁相环pll的特点是什么?如何用硬件配置pll 时钟发生器是指通过特定的电路设计产生适合各种电子设备使用的时钟信

PLL1705/PLL1706双通道PLL多时钟发生器数据表

电子发烧友网站提供《PLL1705/PLL1706双通道PLL多时钟发生器数据表.pdf》资料免费下载

发表于 08-22 11:32

•0次下载

PLL1707/PLL1708 3.3V双通道PLL多时钟发生器数据表

电子发烧友网站提供《PLL1707/PLL1708 3.3V双通道PLL多时钟发生器数据表.pdf》资料免费下载

发表于 08-22 10:06

•0次下载

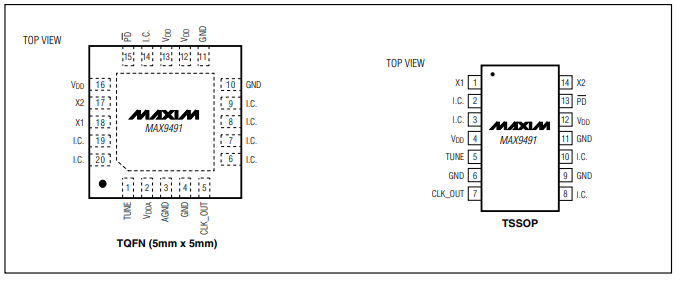

MAX9491工厂可编程、单PLL时钟发生器技术手册

MAX9491是多时钟发生器,非常适合通信应用。该器件提供工厂编程PLL输出,可调节到4MHz至200MHz之间的任意频率。MAX9491使用一次性可编程(OTP) ROM设置PLL输出

PLL1708双PLL多时钟发生器技术文档总结

PLL1708双PLL多时钟发生器技术文档总结

评论