上篇文章提到用于 IC 封装的再分布层(RDL)技术Redistribution layer, RDL 的基本概念是将 I/O 焊盘的位置分配到芯片的其他位置,即用RDL转接到锡球焊接的着陆焊盘位置,如下图所示:

以下一种或多种情况可能需要这样做:

a) I/O 焊盘可能太小或太紧而无法放置可靠的焊接连接;

b) I/O 焊盘可能需要放置在更靠近芯片中心的位置以减少热应力;

c) 其他几何要求(如将非对称 I/O 布局转换为对称焊盘布局)可能需要 RDL。

RDL 的基本制造流程非常简单,包括:

a) 创建嵌入 PI 材料中的铜引线,以将 I/O 焊盘重新布线到其着陆焊盘位置,这里主要有三步:

1)在晶圆表面顶部形成第一介电(永久)层,该层仅在 I/O 焊盘上方打开。通常,使用聚合物薄膜,例如BCB或聚酰亚胺(PI)作为绝缘体。

2)创建从 I/O 焊盘到着陆焊盘的铜引线。这将需要创建一个种子层,通常是TiW和Cu,通过临时光刻胶创建“电镀模板”,然后电化学沉积(ECD)铜引线,最后剥离光刻胶并蚀刻种子层。

3)创建第二个介电层。该层用于保护裸露的铜免受腐蚀,并定义着陆焊盘。

b) 在着陆焊盘顶部创建微凸块(ubump, UBM),以创建与焊料的可靠连接,通常使用各种金属和这些金属的堆叠,如 Ti、Cu、Ni、Pd、Ag、Au、它主要作为焊料向金属再分布层的扩散阻挡金属。这些金属可以通过ECD或溅射产生。无论哪种方式,都需要通过临时光刻胶创建“电镀模板”或“蚀刻模板”;

c) 最后,将可焊接金属放在 UBM 顶部。可焊接金属,如 SnAgCu、AuSn、PbSn,可以在 UBM 顶部形成。这可以通过 ECD 或焊球(Ball drop,BG)来完成。

窄间距RDL(Redistribution Layer)技术是一种在集成电路封装中常用的技术,用于实现芯片与封装之间的连接。RDL层通常由金属线构成,其主要功能是将芯片上的信号和电源引脚布线映射到封装上的引脚,以满足高密度、高性能应用的需求。

窄间距RDL技术的特点是在芯片和封装之间采用了非常小的间隔距离进行布线,可以实现更高的引脚密度和较短的电信号传输路径,从而提高了电路性能和可靠性。

窄间距RDL技术主要包括以下几个方面的关键技术:

- 多层金属线:通过在RDL层中使用多层金属线,可以实现更多的引脚布线和更高的信号密度。

- 超细线宽和间距:采用先进的制造工艺,使得RDL层的金属线宽度和间距可以达到亚微米级别,从而实现更高的集成度。

- 低介电常数材料:选择低介电常数的材料作为RDL层的绝缘材料,可以减小信号传输的延迟和损耗,提高电路性能。

- 高密度布线规则:通过优化布线规则和算法,实现更高的引脚密度和更紧凑的布线结构,使得整个系统的功耗、面积和性能得到优化。

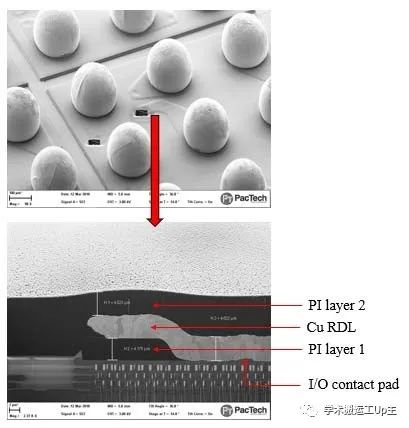

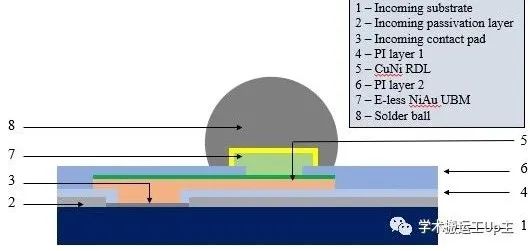

下图显示了窄间距RDL的横截面示意图:

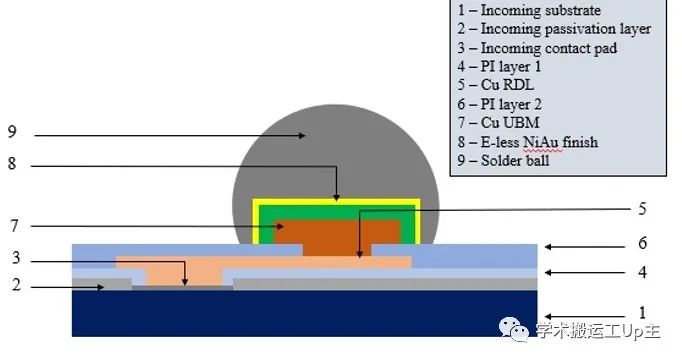

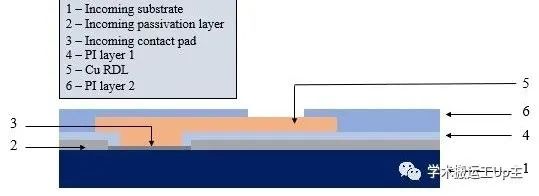

有三种不同的方案可以实现窄间距RDL,并且UBM之前工艺和标准流程相同,在UBM之前完成的工艺截面图如下图所示:

1)Cu BUM & 锡球焊

按照与前面介绍类似的工艺流程创建Cu UBM,通过成锡球阵列焊或锡球喷射在其上焊锡球都可行。锡球焊,如下图所示,无论是单独完成(滚珠喷射)还是在传质过程中完成,都被称为实现紧密间距的可靠和快速过程。使用锡球焊的另一个好处是,几乎任何可以形成焊球的金属,包括三元金属;

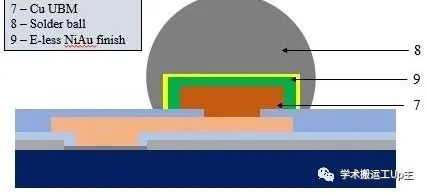

2) Cu UBM & 化学镀NiAu & 锡球焊

在Cu UBM顶部沉积化学镀的NiAu,首先要对Cu UBM表面进行预处理。首先,氧化铜被铜蚀刻剂去除,并沉积一层薄薄的钯 (Pd) 种子层。然后,Cu UBM化学镀上一层Ni(自催化),然后通过氧化还原反应机制浸入Au。

随着化学镀镍在横向以及高度或厚度上的生长,原来的Cu UBM直径会略有扩大,UBM直径的扩大可以估计为镍高度的2倍。这为满足回流焊后所需的焊球高度提供了一定的灵活性。通过控制 Ni 厚度来调整化学镀 Ni 直径,可以创建不同的 UBM 直径,从而影响焊接高度。完成化学镀 NiAu 表面处理后,使用相同的方法将助焊剂和焊球放置在 UBM 顶部,即 GBP 或焊料喷射。

与1)相比,方案2)中的Cu UBM覆盖有NiAu层,并为Cu UBM提供了防腐蚀保护的额外好处,如下图所示:

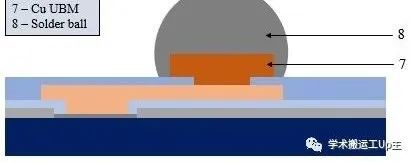

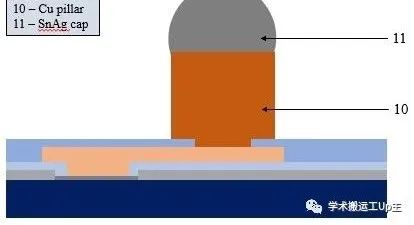

3)Cu柱 & SnAg cap

在焊盘的顶部创建带有锡银(SnAg cap)盖帽的铜柱,如下图所示。其中Cu柱和SnAg帽是在同一电镀工具中通过电镀工艺完成的。使用此方案,可以省略化学镀 NiAu 和锡球焊的过程。此方案也适用于相对较小的铜柱直径和小间距应用,且需要更厚的临时光刻胶,因为整体柱的高度可达 100 μm。

该方案的缺点是焊料合金选择的限制。SnAg合金中的Ag百分比通常通过改变SnAg电解液中的Ag浓度或SnAg镀层电流密度将其控制在1.5%至2.5%的范围内。

窄间距RDL技术在高性能芯片封装中起着重要的作用,它可以支持更高的带宽、更低的延迟和更高的集成度。这些特点使得窄间距RDL技术在高速通信、人工智能、云计算等领域得到广泛应用。

-

芯片

+关注

关注

462文章

53534浏览量

459079 -

集成电路

+关注

关注

5446文章

12465浏览量

372681 -

半导体

+关注

关注

336文章

29977浏览量

258201 -

IC封装

+关注

关注

4文章

193浏览量

27532 -

晶圆级封装

+关注

关注

5文章

44浏览量

11775

发布评论请先 登录

晶圆级封装中的窄间距RDL技术

晶圆级封装中的窄间距RDL技术

评论