从赋能聊天机器人快速生成回答的生成式人工智能工具,到支持金融预测和天气建模的高性能计算(HPC)应用,我们对处理能力的需求显然达到了新的高度。面对这些计算密集型工作负载,单片SoC已不再能够满足当今的处理需求。为此,我们不断创新工程技术,Multi-Die系统也应运而生。这种在单一封装中实现异构集成的技术突破,不仅带来了更优越的系统功耗和性能,还提高了产品良率,加速了更多系统功能的整合。

Multi-Die系统承担着如此重要的角色,那开发者又该如何确保它们在整个生命周期内稳健可靠呢?

芯片测试对于任何芯片设计而言都至关重要。Multi-Die系统更是如此,需要对裸片到系统级执行全面测试,其中包括将各组件连接在一起的所有互连技术,例如通用芯粒互连技术(UCIe)。在这篇文章中,我们将深入探讨Multi-Die系统的独特问题,以及如何通过测试和芯片生命周期管理来确保这些复杂的设计能够按预期可靠地工作。开发者如需获得更多见解,还可以观看我们的网络研讨会系列:“成功实现Multi-Die系统所需具备的条件”(共六个部分)。该系列网络研讨会介绍了Multi-Die系统的趋势和挑战、早期架构设计、协同设计和系统分析、Die-to-Die连接、验证及系统健康状况等等。

从裸片到系统的全面芯片测试

许多因素都会影响芯片的性能,温度、老化和退化只是其中的一部分。对于Multi-Die系统来说,老化风险甚至更高,因为一个裸片发生故障可能会导致整个系统失效,造成巨大的经济损失。在裸片层面排除缺陷是一个很好的开始。每个生产的裸片都将经历专门的测试流程,以确保百万分比缺陷率(DPPM)非常低。测试自动化流程负责测试和诊断器件的数字、内存和模拟部分。这其中的挑战在于找到所需测试向量数量和相关成本之间的平衡点,以期获得理想结果。

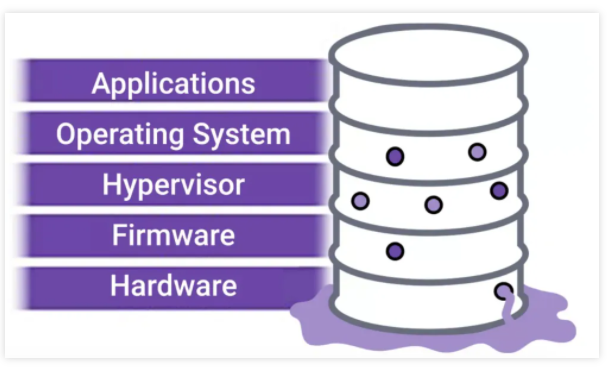

检查每个裸片很重要,在系统层面评估整个系统也很重要。Multi-Die系统可以将不同工艺节点、不同用途的裸片或芯粒组合在一起。因此,一个系统可能包含运行温度或散热水平不同的多个裸片。此外,裸片之间的电磁干扰以及电迁移也可能造成问题。

对于Multi-Die系统,全面而彻底的预组装测试环节,可以筛选出已知良好裸片(KGD)。设计模块内置的高级可测性设计(DFT)功能可以评估裸片。对各个裸片进行测试,并在必要时进行修复后,设计就进入了组装和键合阶段。部分或全部键合内存和逻辑芯片之后,就可以测试互连了。

降低芯粒互连的功耗并提升其性能

Die-to-Die接口使裸片可以并排放置,为了进一步提高密度,还可以堆叠在2.5D或3D封装中。如果两个裸片之间提供数据接口的功能块(即接口),可以兼具高带宽、低功耗和低延迟特性,系统性能就能得到提升。

Die-to-Die连接通常基于高速接口,例如UCIe,该接口有望成为Multi-Die系统的优选互连标准,也是行业唯一具有完整的Die-to-Die接口工具套件的标准。UCIe适用于2D、2.5D未来的3D封装,支持目前每引脚8 Gbps到16 Gbps的大部分设计,非常适合从网络连接到超大规模数据中心的高带宽应用。对于3D设计,由于互连更短,使得硅通孔(TSV)更加脆弱,因此互连级风险更高。

Multi-Die系统开发者需要避免互连中的固定型故障、开路或短路,同时确保时序和电压方面的行为正确。由于涉及超高速信号,信号完整性成为了指示裸片间数据共享有效性的重要参数,所以通过测量和监控来检测信号衰减水平非常重要。UCIe要求在PHY的两侧之间提供冗余通道,从而支持通过这些额外的通道实现故障修复。基于UCIe系统中的所有裸片都必须通过UCIe通道进行访问、测试和修复,以便能够监控裸片中正在发生的问题。

键合后测试可以解决一些要求切换互连通道的互连层面问题,还可以通过算法测试来评估互连缺陷。2.5D和3D互连有不同的算法集,而且测试是基于互连的缺陷。故障模型将决定所要应用的算法测试。

贯穿系统生命周期的智能监控和分析

Multi-Die系统具有微小的微凸块,这些微凸块彼此非常靠近,因此无法通过物理探测进行测试。例如,对于UCIe,微凸块的间距为25至55微米,而探测距离通常为90微米。更好的办法是通过内置自测(BIST)进行电子探测,从而检测那些需要采取纠正措施的软错误或硬错误。或者也可以使用在预组装阶段集成的专用晶圆测试焊盘。

当系统处于开发阶段以及在现场使用时,芯片生命周期管理(SLM)方法就很有用。这种方法通过在芯片上集成传感器和监控器来评估各种参数,例如温度、电压、老化和退化程度。集成SLM IP技术与分析智能后,可以将从器件传感器和监控器收集的大量数据转化为可操作的系统优化洞察。

那么SLM技术如何识别热问题呢?无论是单个裸片还是Multi-Die系统,热管理问题都不容忽视。在设计阶段,由于没有实际工作负载,开发者很难评估这些问题。再加上2.5D或3D架构的复杂性后,更是很难得到最终设计的热曲线。以下是SLM能发挥作用的情况。布置在裸片重点位置的片上监控器让开发者有机会深入了解和分析裸片的热特性,并且可以在需要调整布局以解决散热问题时提供指示信号。同样,深入了解热效应还可能促使开发者做出降低系统高带宽内存(HBM)组件数据速率的决策。或者,可能还可以通过软件来缓解散热问题。借助监控器提供的数据,开发者可以分析并确定更优纠正方案。

SLM技术还提供可追溯性,即无论最终产品在生命周期中何时出现问题,它都能追溯到问题的根源。例如,假设在试制过程的某个环节发现良率异常,此时准确定位问题来源至关重要。我们需要判断问题是出在某个特定晶圆或裸片上,还是影响了某一时期内生产的所有晶圆或裸片,抑或是源于晶圆厂本身。这种追溯能力在Multi-Die系统中尤为重要,因为此类系统的封装成本可能非常高。越快发现问题,开发者就能越快让产品进入市场并降低成本。良好的SLM解决方案应该能够在几分钟内识别根本原因,而手动方法可能需要花费几天或几周时间。

可追溯性还适用于以下情况:最终产品已部署到现场,但开始出现意外甚至灾难性的故障,可能需要召回。这种退货授权(RMA)情况可以利用SLM和整个测试生态体系,追溯制造过程,找出根本原因。同时,还能找出现场中可能存在相同问题的同类器件,以便在故障发生前主动召回,或者通过调整器件的电压或频率来延长其使用寿命。

测试的最后阶段针对堆叠本身进行。“已知良好系统”是此阶段的核心,因为测试团队的目标是确定其Multi-Die系统能否稳定可靠地运行,并在需要时找到监控、分析和解决问题的方法。IEEE Std 1838-2019提供了一种模块化测试访问架构,可支持测试裸片以及相邻堆叠裸片之间的互连层。

对于堆叠架构,有些测试需要在下游进行,而更智能的测试仍然留在流程的上游。例如,在裸片层面评估高温性能是不可行的。相反,在堆叠后进行Multi-Die系统的温度测试最有效,此时发现的故障可以根据其位置进行修复。在晶圆层面进行温度测试也是可行的,不过这可能相当昂贵。高端系统的开发者可能会选择执行这些测试。监控和收集这些重要数据,能够让设计、制造和测试团队确定如何提高结果质量。

自动化和智能化进一步提高Multi-Die系统的质量

为了满足我们所讨论的需求并推动下一波半导体创新,新思科技推出了Multi-Die解决方案,以加速单一封装中的异构集成。这套全面的解决方案涵盖了系统全生命周期的各个关键环节,包括测试、诊断、修复、校准以及持续优化各项性能指标。针对设计、试制、生产和现场优化的可追溯性和分析能力可以提高良率、质量和可靠性,并降低成本。此外,我们的AI驱动芯片设计套件Synopsys.ai具备业界少有的半导体测试自主AI应用程序。新思科技TSO.ai优化了复杂设计中的测试程序生成过程,能以更少的测试向量实现尽可能高的缺陷覆盖率。

为了满足计算密集型工作负载对高带宽和高性能的需求,Multi-Die系统正迅速成为芯片设计的主流。自动化测试流程和分析智能有助于提高上述系统的质量和可靠性水平,而这更是为生成式人工智能和高性能计算(HPC)等造福全世界的应用带来了曙光。

-

芯片测试

+关注

关注

6文章

182浏览量

21179 -

人工智能

+关注

关注

1820文章

50325浏览量

266961 -

新思科技

+关注

关注

5文章

979浏览量

52989 -

HPC

+关注

关注

0文章

350浏览量

25073

原文标题:从GenAI到HPC,Multi-Die系统如何满足现代计算需求?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

新思科技携手Socionext实现3DIC芯片成功流片

新思科技发布全新软件定义硬件辅助验证解决方案

MULTI-BEAM Plus电源连接器有何特点?-赫联电子

新思科技Multi-Die方案助力车企迈向汽车电子新时代

新思科技助力UCIe 3.0快速落地

新思科技以AI驱动EDA加速Multi-Die创新

新思科技斩获2025年台积公司开放创新平台年度合作伙伴大奖

面向芯粒设计的最佳实践

为何硬件安全与软件安全在现代系统中同等重要

新思科技UCIe IP解决方案实现片上网络互连

新思科技网页端虚拟原型工具的工作流程

新思科技Multi-Die系统如何满足现代计算需求

新思科技Multi-Die系统如何满足现代计算需求

评论