引言

人工智能(AI)和机器学习(ML)技术的需求正以惊人的速度增长,远超摩尔定律的预测。自2012年以来,AI计算需求以每年4.1倍的速度指数增长,为半导体制程缩放和集成带来重大挑战。为应对这些需求,业界采用了基于Chiplet的设计方法,将较大系统分解为更小、更易于管理的组件,这些组件可以分别制造并通过先进封装技术进行集成[1]。

先进封装技术

先进封装技术可以大致分为2D、2.5D和3D方法。2.5D集成技术,包括晶圆级芯片堆叠(CoWoS)和集成扇出型封装(InFO),在高性能计算应用中获得了显著发展。

图1:台积电3D Fabric技术组合,展示了包括CoWoS、SoIC和InFO平台在内的各种封装选项,满足不同集成需求。

CoWoS技术提供三种主要变体:

1. CoWoS-S:采用硅中介层实现密集金属布线

2. CoWoS-R:在有机中介层中使用重布线层

3. CoWoS-L:结合-R和-S两种方案的优势

InFO平台已从移动应用发展到高性能计算,提供多种选项,包括局部硅桥接和嵌入式去耦电容,以实现更好的供电性能。

芯片间互连应用

芯片封装的演进带来了各种凸点间距缩放选项,从传统MCM封装(110-130μm间距)到先进的2.5D封装(40μm间距)和3D集成(9μm或更小间距)。

图2:凸点间距缩放视角,展示了从MCM到先进封装技术的演进,随着间距减小带宽密度不断提高。

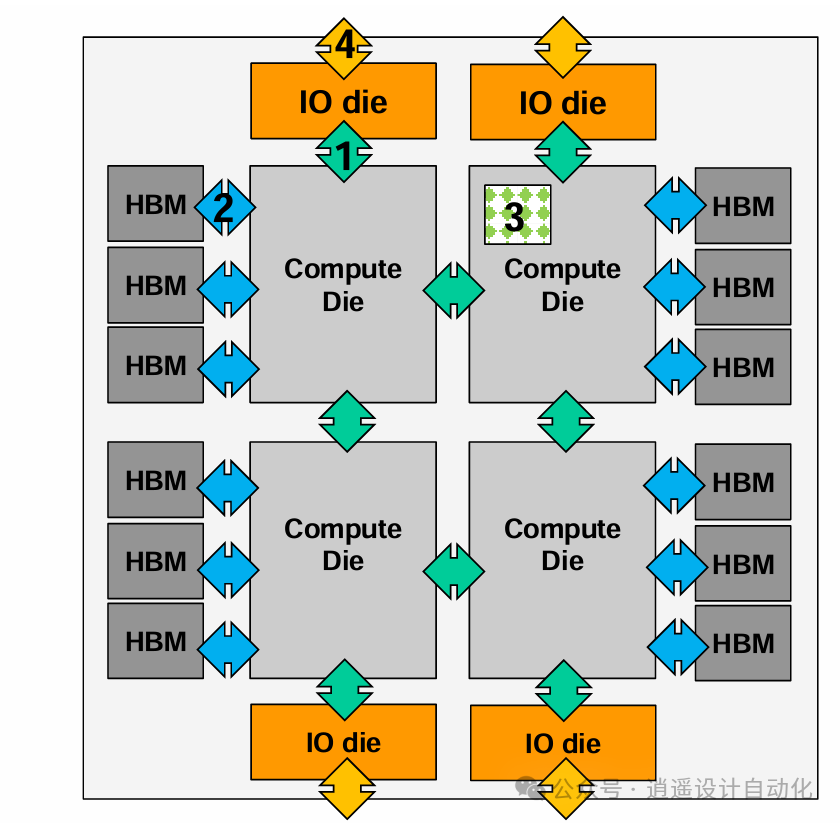

现代Chiplet系统中使用不同的互连技术服务于不同目的:

计算到计算及IO连接使用UCIe PHY

计算到内存连接使用HBM PHY

计算到SRAM连接通过3D堆叠实现

IO chiplet到外部IO使用XSR-SerDes

图3:芯片间互连应用,展示了计算芯片、内存和IO组件之间的不同类型连接。

设计考虑和挑战

通道优化在实现最佳信号完整性和可布线性方面发挥关键作用。设计人员必须平衡各种因素,包括介电层厚度、金属间距、层厚度和过孔封装规则。

图4:通道可布线性和信号完整性优化,展示了中介层子部分设计和相应的信号完整性测量。

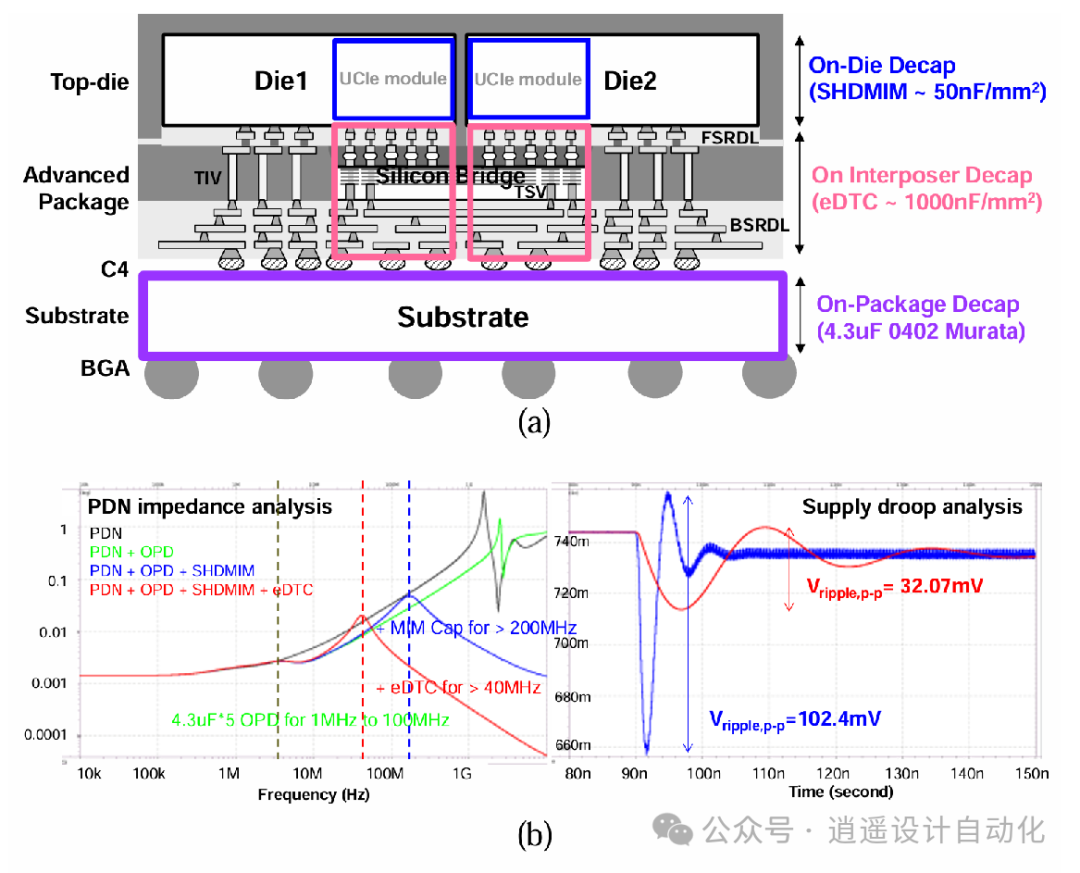

供电代表另一个关键挑战,尤其是在电流密度不断增加的情况下。现代解决方案包含多级去耦电容:

图5:供电网络的去耦电容策略,展示了不同类型电容及其在系统中的布置。

未来趋势和发展

业界持续追求更高的带宽密度和能源效率。技术制程缩放在实现这些改进方面发挥核心作用。

图6:技术和带宽缩放趋势,展示了数据速率、凸点间距和制程节点之间的关系。

对于更大规模集成,晶圆级封装变得越来越重要。这种方法允许超越传统光罩尺寸限制的集成。

图7:晶圆级系统扩展示意图,展示了多个Chiplet和HBM内存在晶圆级系统中的集成。

结论

高带宽Chiplet互连是下一代计算系统的核心技术。通过仔细考虑封装技术、互连架构和设计优化,这些系统能够为要求严格的AI和ML应用提供所需的性能。随着行业不断发展,供电、散热和系统集成方面的新挑战将推动该领域的进一步创新。

参考文献

[1] S. Li, M. Lin, W. Chen and C. Tsai, "High-bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions," IEEE Open Journal of the Solid-State Circuits Society, 2024, doi: 10.1109/OJSSCS.2024.3506694

-

CoWoS

+关注

关注

0文章

170浏览量

11536 -

chiplet

+关注

关注

6文章

499浏览量

13650 -

先进封装

+关注

关注

2文章

563浏览量

1062

原文标题:TSMC | 高带宽Chiplet互连的技术、挑战与解决方案

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cadence陈会馨:PCIe技术演进与AI时代的IP解决方案

多Chiplet异构集成的先进互连技术

创新的高带宽DRAM解决方案

Amphenol LTW:严苛环境下的卓越互连解决方案

Amphenol Multi-Trak™:下一代高速互连解决方案

Amphenol DisplayPort 2.1 Connector:超高清视频音频互连解决方案

Amphenol LTW:数据中心互连解决方案的创新先锋

Amphenol LTW:数据中心互连解决方案的创新先锋

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

Chiplet封装设计中的信号与电源完整性挑战

长电科技光电合封解决方案降低数据互连能耗

中航光电推出车载摄像头互连解决方案

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

新思科技UCIe IP解决方案实现片上网络互连

分享两种前沿片上互连技术

高带宽Chiplet互连的技术、挑战与解决方案

高带宽Chiplet互连的技术、挑战与解决方案

评论