随着半导体工艺逐渐逼近物理极限,单纯依靠制程微缩已难以满足人工智能、高性能计算等领域对算力与能效的持续增长需求。在此背景下,Chiplet作为一种“后摩尔时代”的异构集成方案应运而生,它通过将不同工艺、功能的模块化芯片进行先进封装集成,成为应对高带宽、低延迟、低功耗挑战的核心路径。

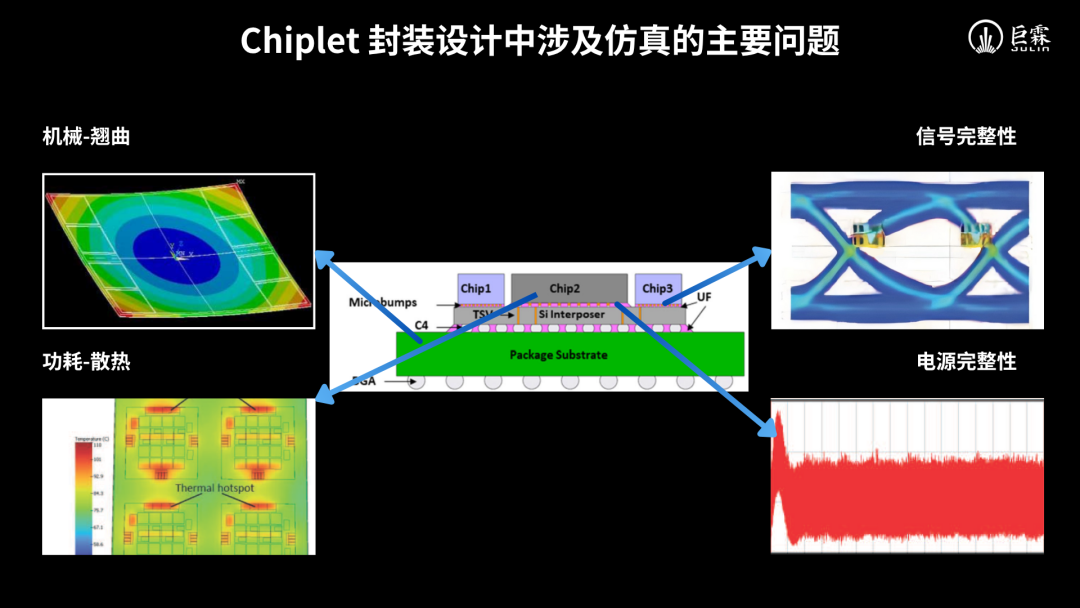

然而,这种架构也将设计的复杂性从单一的硅晶圆扩展至整个封装系统,使得机械应力、热管理、信号完整性及电源完整性等多物理场问题相互交织,构成了前所未有的仿真与验证挑战。

多物理场问题凸显封装设计复杂性

Chiplet的2.5D、3D等先进封装结构,在提升集成度的同时,也引入了显著的多物理场耦合效应。

机械翘曲问题因封装尺寸增大、材料种类繁多及热应力集中而加剧,其仿真精度高度依赖于对生产工艺和材料属性的精确建模。

热管理挑战则源于多芯片功耗叠加与局部热密度过高,仿真需精确构建从芯片内部模块到系统级散热路径的完整热阻网络。这些机械与热效应会进一步改变传输线的电气特性,使得纯粹的信号分析必须让位于多物理场协同仿真。

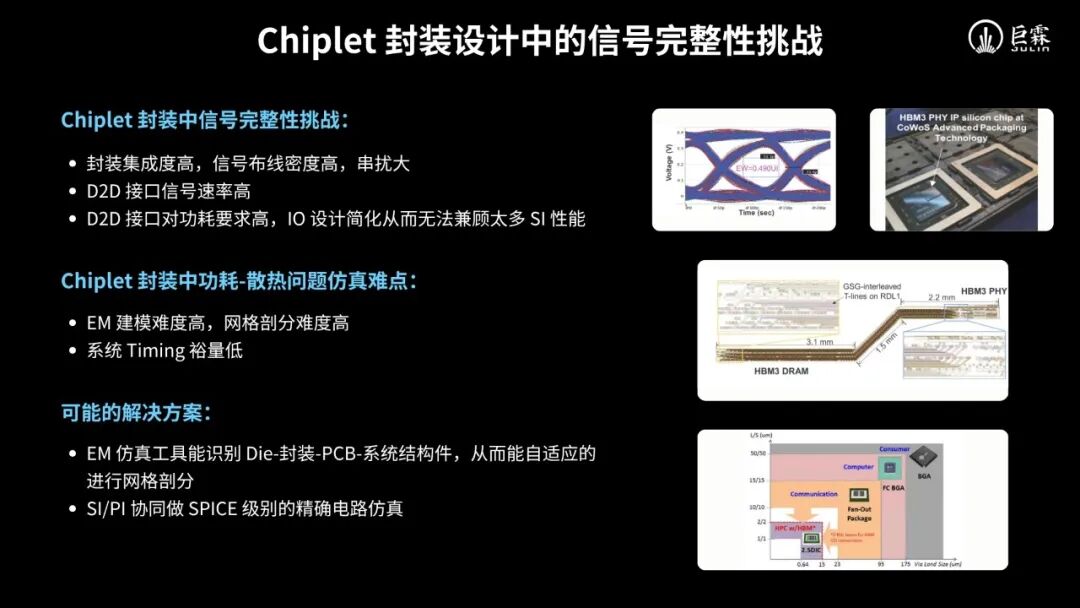

在所有这些挑战中,信号完整性问题因其直接关系到系统稳定性而尤为关键。其首要挑战在于跨尺度电磁建模难度。同一封装内,互连结构尺寸从亚微米级别的硅中介层布线,跨越至数十微米级别的有机基板走线,这种尺度差异对电磁仿真工具的网格剖分与算法精度构成了极限考验。

与此同时,Die-to-Die接口的数据速率正持续攀升。在高布线密度下,严重的串扰与传输损耗,结合为追求低功耗而简化的IO设计,使得信号时序裕量被极度压缩。这要求仿真工具不仅需提供SPICE级别的电路仿真精度,还必须具备SI/PI协同分析能力,以精确评估电源噪声对敏感时序的影响。

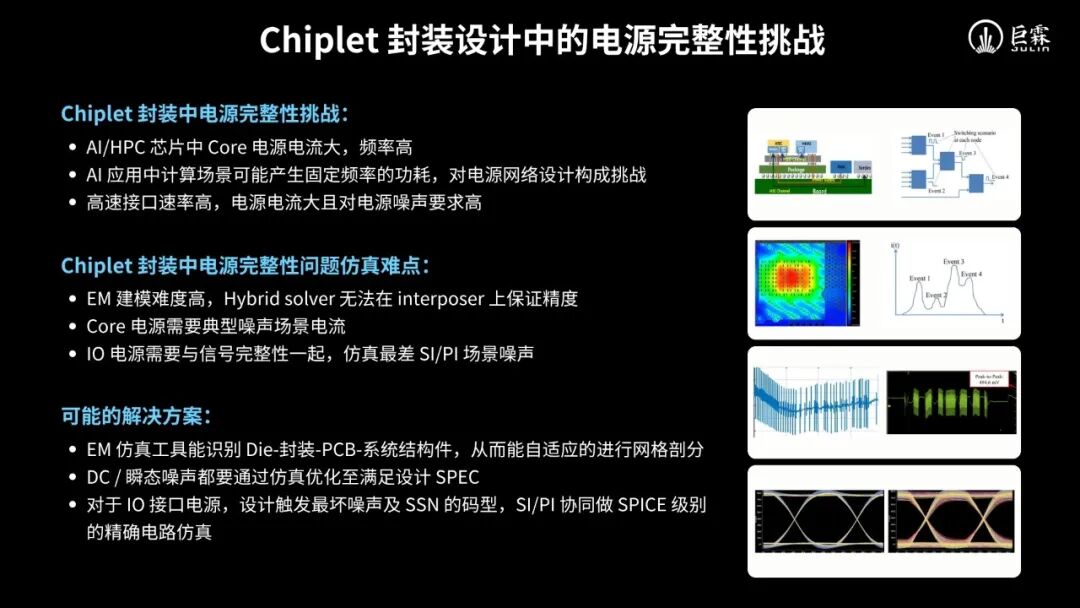

电源完整性同样面临严峻考验。AI等应用中的计算单元会产生特定频率的突发电流,对电源网络构成周期性冲击。而高速接口的核心与IO电源则需在承受大电流的同时,维持极低的噪声水平。

仿真难点在于,电源网络的电磁建模面临与信号网络类似的跨尺度挑战,且需在时域中模拟最恶劣的工作场景电流。成功的电源完整性仿真依赖于对电源分配网络频域阻抗的精准优化,以及通过瞬态仿真对负载突变引发的电压波动进行充分验证。

精度与效率的再平衡,驱动工具链演进

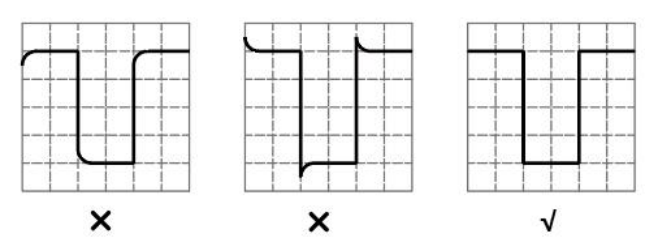

目前,行业正面临长瞬态仿真与统计仿真的取舍困境。长瞬态仿真可真实反映物理特性,是精度验证的基线,但其计算成本随着信号速率与信道长度的增加而变得难以承受。统计眼图算法虽能将仿真时间从数周缩短至分钟级,但其固有的系统性误差在Chiplet对时序裕量要求极高的背景下已不容忽视。

应对这些挑战,需要仿真技术栈的整体演进。行业参与者正在探索相应的技术路径,例如通过高保真电路模型、高精度电磁场模拟及混合求解器来应对跨尺度建模问题。以巨霖科技的SIDesigner平台为例,通过集成电路级与统计仿真求解器,旨在平衡SI/PI协同仿真时的精度与效率需求,以解决传统工具在网格剖分适应性与统计眼图精度等方面的具体痛点。

结语

Chiplet技术将芯片设计的战场从单一的晶圆扩展到整个封装系统。在此背景下,信号与电源完整性已不再是孤立的设计环节,而是与机械、热等因素深度耦合的系统级问题。突破跨尺度电磁建模、实现高效高精度的多物理场协同仿真,已成为推动Chiplet技术持续演进、释放其全部性能潜力的关键所在。业界对新一代EDA工具的期待,正聚焦于其能否在更严苛的签核标准下,真正打通从芯片到封装乃至系统的全链路仿真。

-

仿真

+关注

关注

55文章

4536浏览量

138670 -

封装设计

+关注

关注

2文章

49浏览量

12188 -

chiplet

+关注

关注

6文章

499浏览量

13650

原文标题:Chiplet封装设计面临多维仿真挑战,信号与电源完整性成关键技术瓶颈

文章出处:【微信号:巨霖,微信公众号:巨霖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IDT信号完整性产品:解决高速信号传输难题

PK6350无源探头在高速数字总线信号完整性测试中的应用案例

是德DSOX1204A示波器在电源完整性测试中的关键优势

了解信号完整性的基本原理

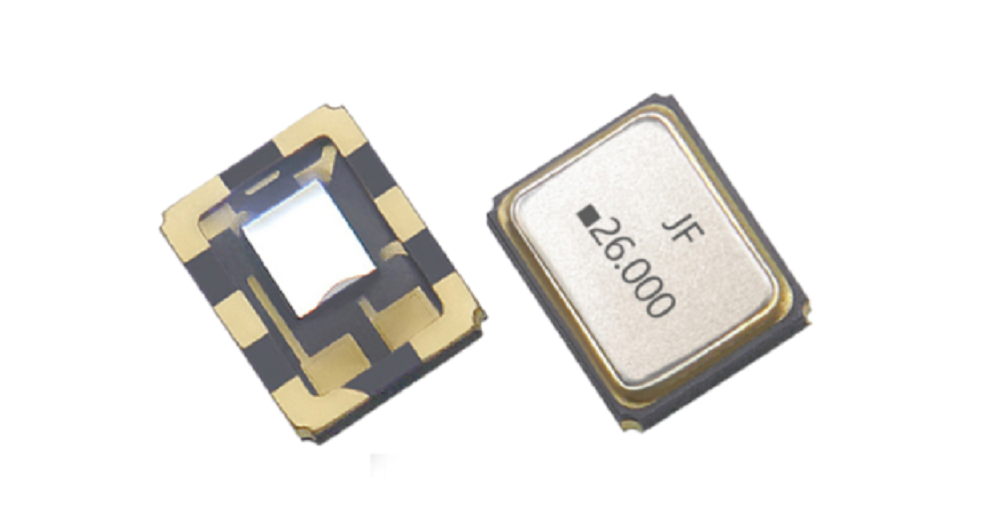

高频晶振的信号完整性挑战:如何抑制EMI与串扰

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

Chiplet封装设计中的信号与电源完整性挑战

Chiplet封装设计中的信号与电源完整性挑战

评论