基于XC7A100T的PCIe千兆电口以太网收发卡

一、板卡概述

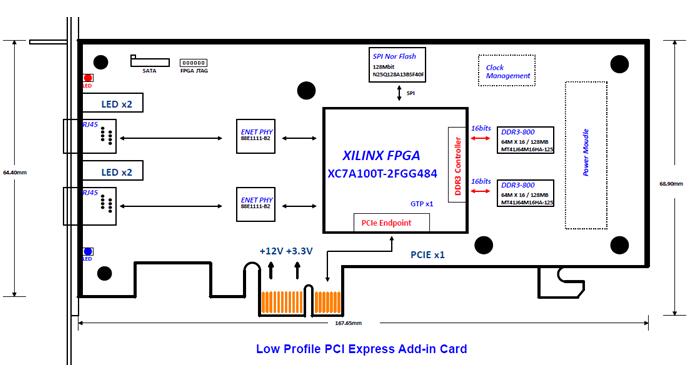

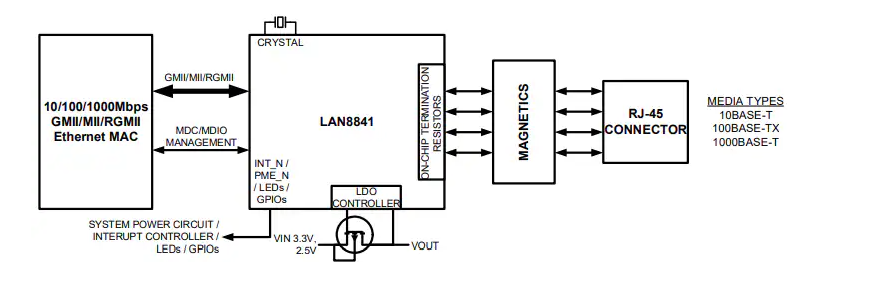

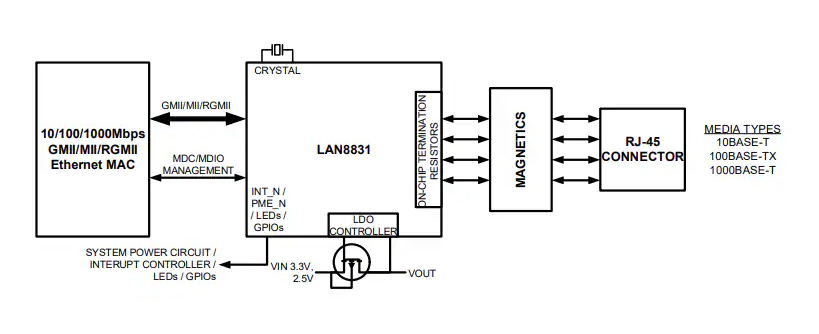

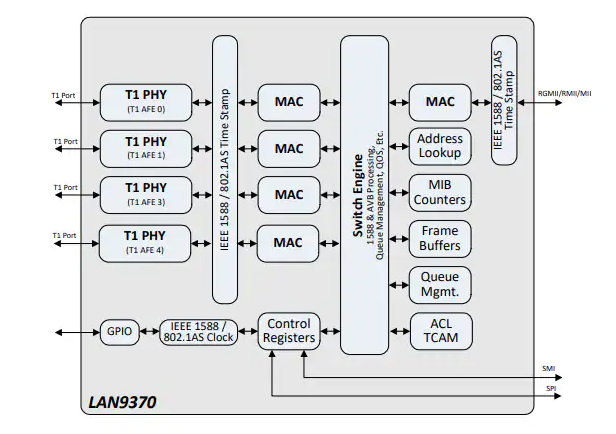

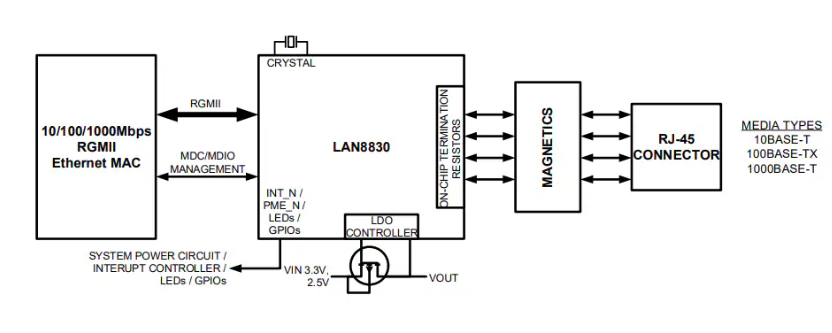

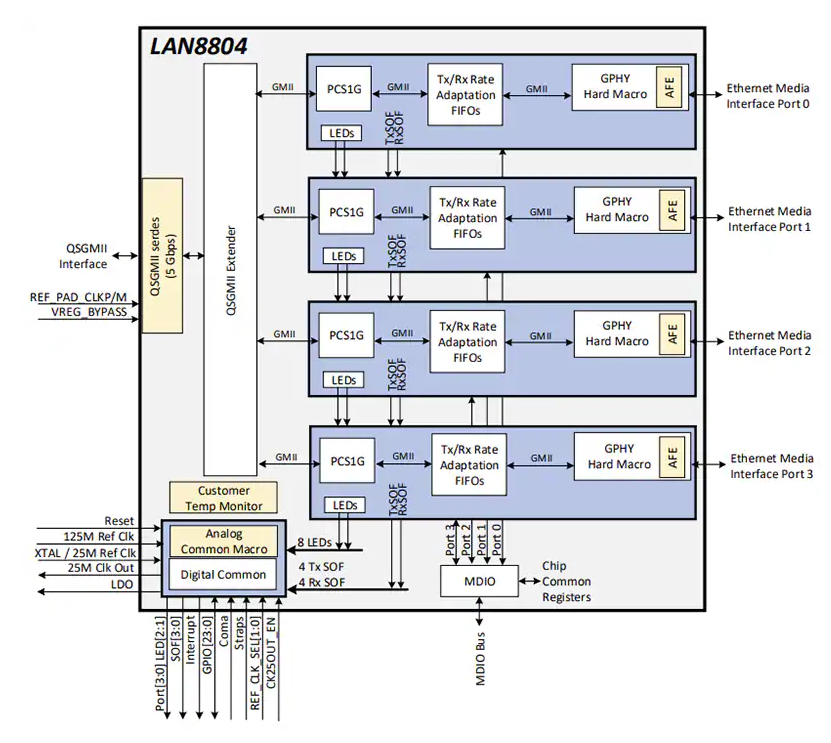

本板卡采用Xilinx公司的Artix7系列的XC7A100T-2FGG484芯片作为主处理器。北京太速科技板卡包含双路千兆电口网络,双组DDR,PCIeX1V1.1接口,板卡设计满足工业级要求。

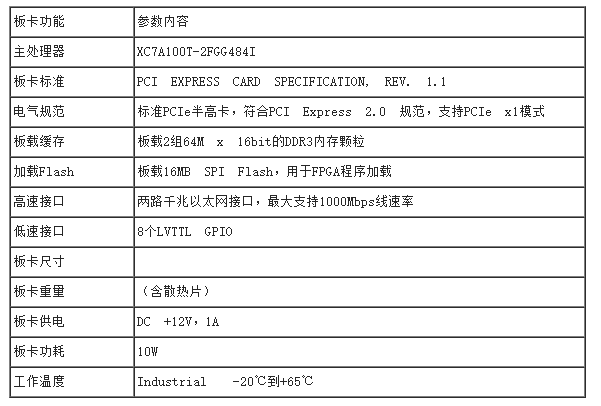

二、功能和技术指标:

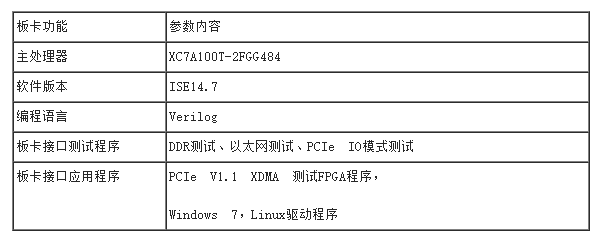

三、接口测试软件:

板卡功能

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

以太网

+关注

关注

41文章

6177浏览量

181530 -

光电

+关注

关注

8文章

858浏览量

83222 -

脉冲

+关注

关注

20文章

911浏览量

100050 -

板卡

+关注

关注

3文章

178浏览量

17510

发布评论请先 登录

相关推荐

热点推荐

数据采集IO卡设计原理图:136-KC705E增强版基于FMC接口的 Kintex-7 XC7K325T PCIeX8 接口卡

FMC子卡模块, Kintex-7 XC7K325T板卡, 高速信号处理, 软件无线电处理平台, 数据采集IO卡

6UCPCI板卡设计方案:8-基于双TMS320C6678 + XC7K420T的6U CPCI Express高速数据处理平台

C6678, C6678板卡, C6678图像处理板, 高速数据处理平台, XC7K420T处理板

DP83847 DsPHYTER II:单10/100以太网收发器的全面解析

DP83847 DsPHYTER II:单10/100以太网收发器的全面解析 在当今的网络通信领域,以太网收发器扮演着至关重要的角色。DP8

一代蜂鸟E203移植普通Artix7核心板中IDE的cfg配置文件修改

XC7A100T的核心板;

在调整好PL蜂鸟SoC的工程后(注释部分无效代码,适配对应时钟,修正引脚约束等),本文中不做展开。然后打开NucleiStudio,新建工程,找到工程中的cfg文件

发表于 10-29 06:45

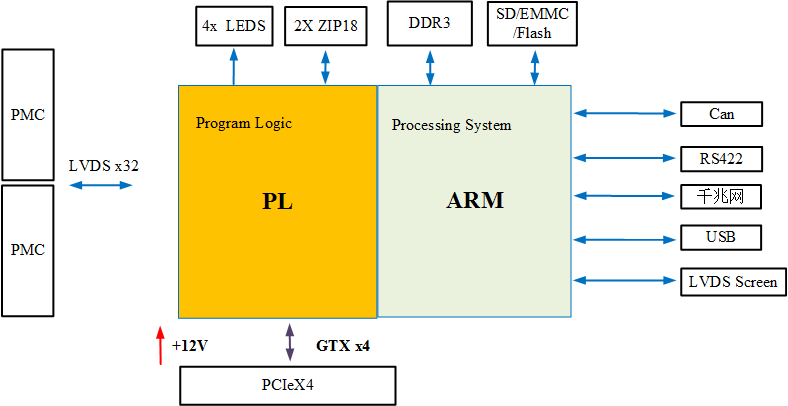

PCIe接口卡设计原理图:124-基于XC7Z015的PCIe低速扩展底板

板卡由SoC XC7Z015芯片来完成卡主控及数字信号处理,XC7Z015内部集成了两个ARM Cortex-A9核和一个Artix 7的F

fpga开发板 璞致Artix-7系列之PA-Starlite Artix7 A735T 75T 100T 200T开发板用户手册-学习板

方式(USB Type-C或40P扩展口)。板载包括:1GB DDR3、128Mb QSPI Flash、64Kbit EEPROM、千兆以太网、HDMI输出、MIPI接口(除PA35T

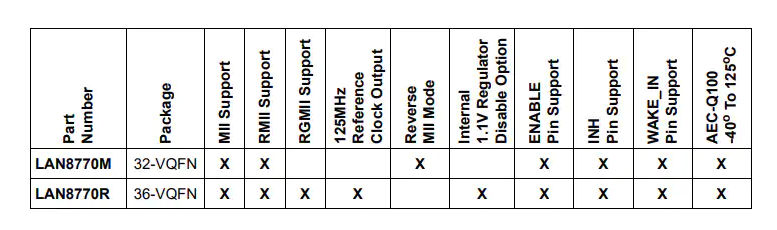

LAN8770 100BASE-T1以太网PHY收发器技术解析

Microchip Technology LAN 8770100 BASE-T1 以太网 PHY 收发器是紧凑型、高性价比、单端口器件,符合 IEEE 802.3bw-2015 规范。LAN8770通过单个非屏蔽双绞线 (UTP

VPX处理板设计原理图:9-基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信号处理卡 C6678板卡, XC7VX690T板卡, VPX处理板

AI边缘计算,, C6678板卡, PCIe信号, VPX处理板, XC7VX690T板卡

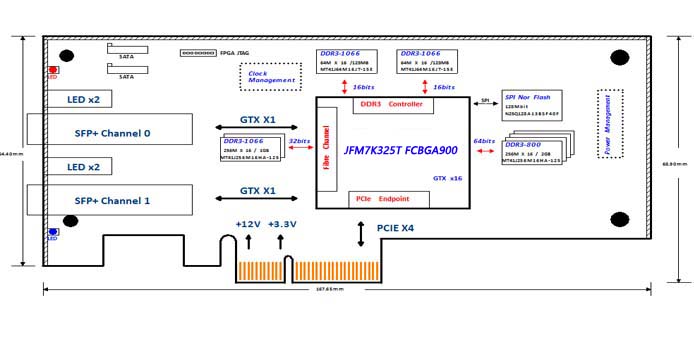

国产化板卡设计原理图:2295-基于 JFM7K325T的半高PCIe x4双路万兆光纤收发卡

JFM7K325T, JFM7VX690T板卡, Ultrasacle万兆网络光纤, 高速数据采集系统, 光纤隔离网闸

XC7A100T板卡设计原理图:297-基于XC7A100T的PCIe千兆电口以太网收发卡

XC7A100T板卡设计原理图:297-基于XC7A100T的PCIe千兆电口以太网收发卡

评论