来源:科学之邦

【研究背景】

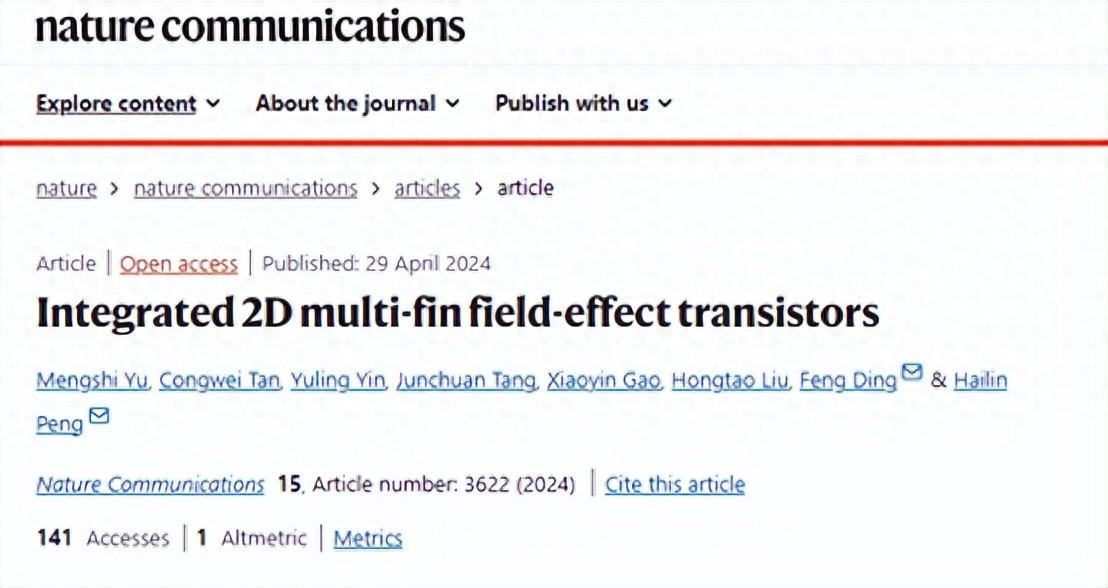

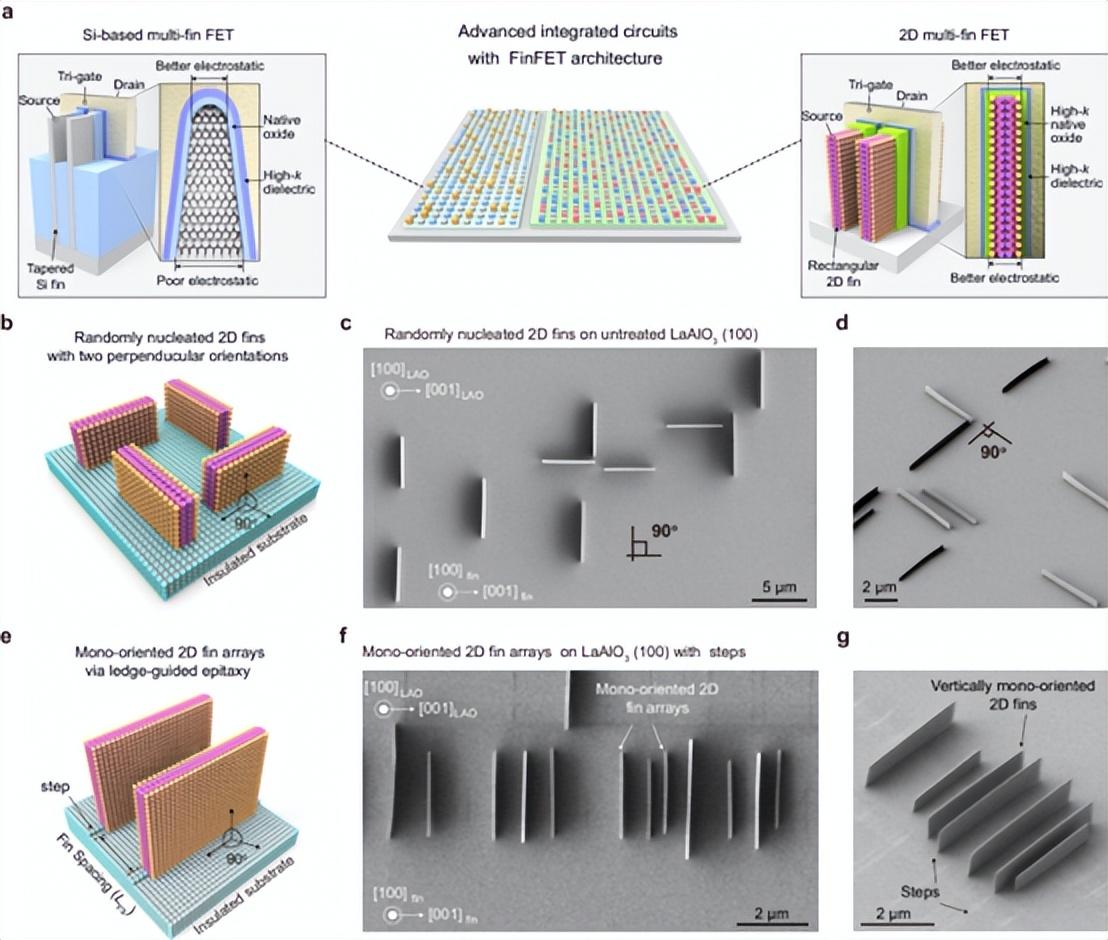

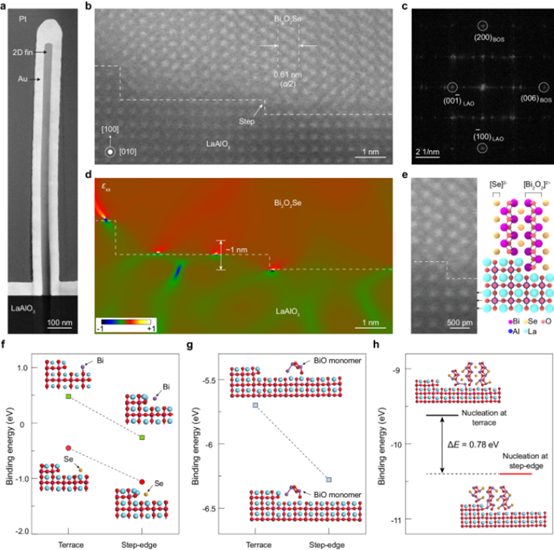

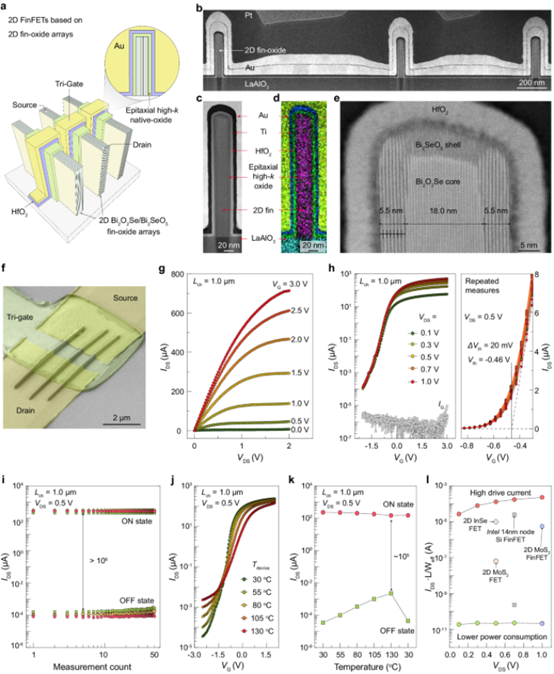

随着摩尔定律的推进,传统基于三维半导体的场效应晶体管(FETs)不断缩小,这导致了设备性能的提升和晶体管密度的增加。然而,随着尺寸的进一步缩小,传统FETs面临着诸多挑战,包括短通道效应、界面缺陷和非均匀静电控制等问题。为了应对这些挑战,学术界和产业界开始关注二维(2D)半导体材料的潜力,这些材料具有原子平坦的表面和优异的电子特性。在此背景下,研究人员开始探索利用2D材料构建3D晶体管结构,特别是垂直2D FinFETs。这种结构具有优越的静电控制和更低的能耗,但传统基于硅的FinFETs在继续缩小尺寸时遇到了困难,如短通道效应和鳍形状导致的非均匀静电控制。因此,研究人员开始关注使用2D半导体构建垂直2D FinFETs,以克服这些挑战。然而,过去的研究主要集中在单鳍FETs上,对于实现高密度集成和更高性能的多鳍FETs仍存在挑战。因此,本研究的背景是要解决如何在多鳍FETs中实现高密度的2D鳍阵列生长的问题。针对这一挑战,北京大学化学与分子工程学院教授和课题组长、国家杰出青年科学基金获得者彭海琳教授、深圳理工大学/中科院深圳先进技术研究院丁峰教授研究团队合作并提出了一种搭台引导外延的方法,可以在各种绝缘基底上生长高密度、单向的2D鳍阵列,从而实现集成2D多鳍FETs。这种方法通过控制核结合能量和基底对称性,实现了高密度平行的2D鳍阵列的生长,最小鳍间距可达亚20纳米。

二、【研究亮点】

1.本文首次提出了一种 ledge-guided epitaxy 方法,成功在不同绝缘基底上生长了高密度、单向的二维(2D)鳍阵列,用于制造集成的2D多鳍场效应晶体管(FETs)。2.通过此方法,研究人员能够控制2D Bi2O2Se鳍阵列的成核位置和方向,实现了最小鳍间距为亚20纳米的高密度平行2D鳍阵列的生长。3.实验结果表明,采用 ledge-guided epitaxy 方法生长的2D Bi2O2Se鳍阵列具有独特的单向性,且与基底的对称性无关,与最近报道的缺陷诱导外延方法有所不同。4.此外,预先创建的对齐台阶有助于降低在台阶边缘的核结合能量,进而控制2D鳍阵列的成核位置和方向。5.利用这一方法制备的2D Bi2O2Se鳍阵列被成功集成到多通道2D FinFETs中,并与高介电常数的天然氧化物Bi2SeO5进行了集成,展现出优越的电性能和良好的耐久性,包括低关态电流(IOFF)、大通/关电流比(ION/IOFF)超过106和高通态电流(ION)。

图1:垂直2D鳍阵列的搭台引导外延生长,用于2D多鳍场效应晶体管(FETs)。

图2. 通过搭台引导外延生长的垂直2D鳍的结构表征和成核机制。

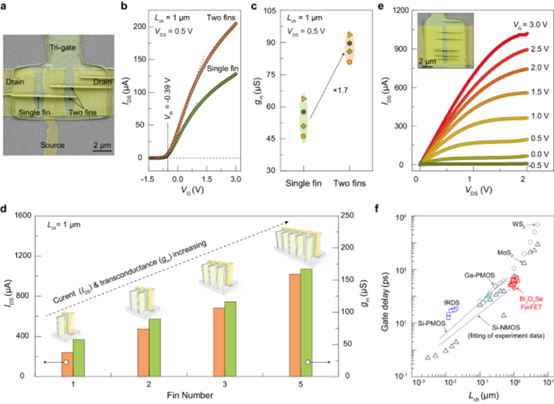

图3.在步骤的帮助下,引导生长单向高密度2D鳍阵列,用于2D多鳍FETs。

图4.基于排列的2D Bi2O2Se-Bi2SeO5鳍氧化物阵列的2D多鳍FinFETs的电性能。

图5:具有不同数量鳍的2D FinFETs的电性能比较。

三、【研究结论】

总的来说,作者开发了搭台引导外延作为一种多功能的方法,用于在各种绝缘基底上制备高密度单向的2D Bi2O2Se鳍阵列。作者证明了生长基底的原子级锐利步边在控制垂直2D Bi2O2Se鳍的成核位置和平面取向中起着至关重要的作用。基于外延集成的2D Bi2O2Se/Bi2SeO5鳍-氧化物阵列制成的2D多鳍FETs表现出高通态电流和显著的器件耐久性,即使在重复测量和高工作温度下也是如此。通过进一步优化通过离子束刻蚀实现的高密度对齐台阶的制备,以及精确控制台阶间距,可以实现有序的更高密度2D Bi2O2Se鳍阵列。这一进步将促进2D多鳍FETs的大规模集成,从而进一步推动2D晶体管的尺寸缩放。原文详情:Yu, M., Tan, C., Yin, Y. et al. Integrated 2D multi-fin field-effect transistors. Nat Commun 15, 3622 (2024).

https://doi.org/10.1038/s41467-024-47974-2

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!诚邀您报名参会:https://w.lwc.cn/s/n6FFne

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇

-

场效应晶体管

+关注

关注

6文章

425浏览量

20706 -

半导体材料

+关注

关注

11文章

579浏览量

30907

发布评论请先 登录

高密度配线架面板

MPO分支光缆:高密度光纤布线的核心组件

高密度配线架特殊场景与前沿趋势

法动科技EDA工具GrityDesigner突破高密度互连难题

高密度光纤布线:未来的数据通信解决方案

EMI滤波高密度D-Sub连接器技术解析与应用指南

哪种工艺更适合高密度PCB?

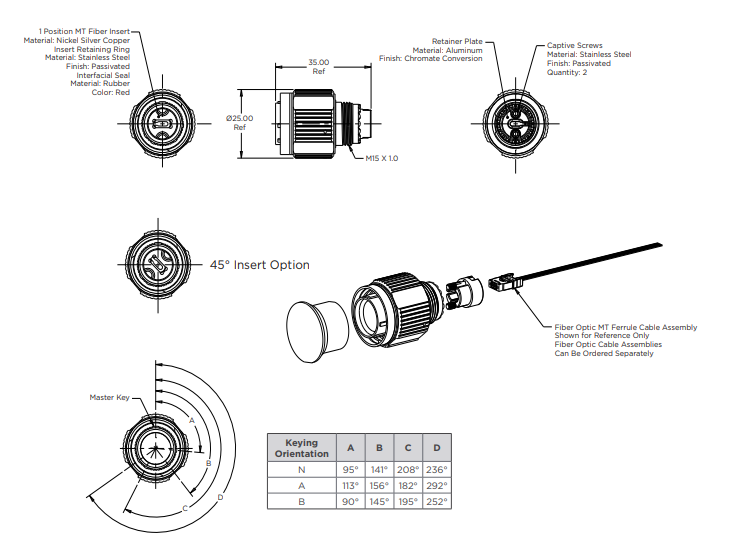

基于TE Connectivity VITA 87高密度圆形MT连接器的技术解析与应用指南

简仪科技高密度多物理量自动化测试解决方案

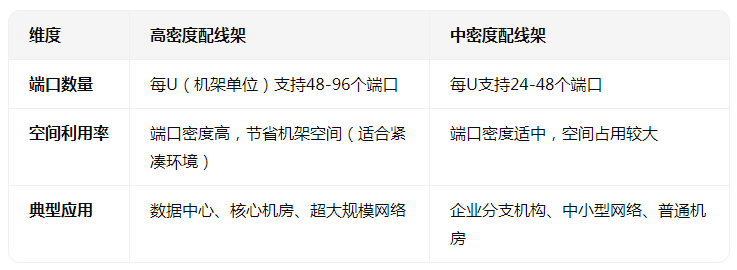

高密度配线架和中密度的区别有哪些

白城LP-SCADA工业产线高密度数据采集 实时响应无滞后

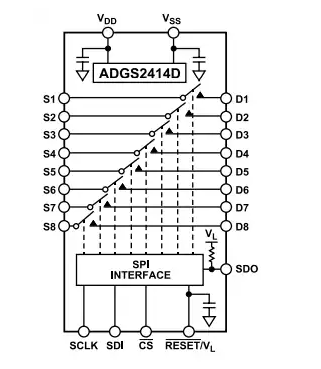

Analog Devices Inc. ADGS2414D高密度开关数据手册

2D多鳍FETs的高密度集成,搭台引导外延的科技突破!

2D多鳍FETs的高密度集成,搭台引导外延的科技突破!

评论