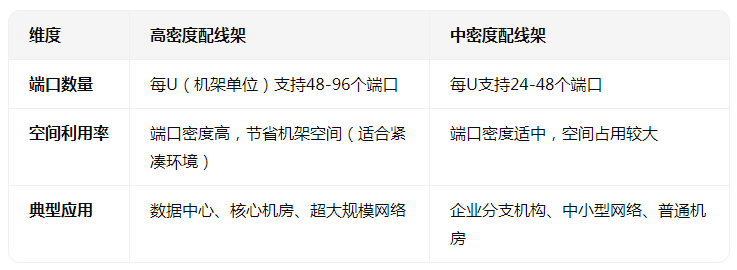

高密度配线架与中密度配线架的核心区别体现在端口密度、空间利用率、应用场景适配性、成本结构及扩展能力等方面,以下为具体分析:

一、端口密度与空间利用率

高密度配线架

端口密度:每单位空间(如1U机架高度)可集成数百个光纤或铜缆端口(如MPO高密度配线架支持1U/96芯以上)。

空间利用率:通过模块化设计(如MPO连接器集成多芯光纤)和紧凑结构,显著提升机柜空间利用率,适合数据中心等对空间敏感的场景。

中密度配线架

端口密度:每单位空间端口数量较少(如1U/48芯或更低),通常为标准双绞线配线架或低密度光纤配线架。

空间利用率:端口布局较稀疏,空间占用相对较大,适合对端口密度要求不高的场景。

二、应用场景与性能需求

高密度配线架

适用场景:数据中心、大型机房、云计算中心等需要高带宽、低延迟且端口密集的场景。

性能需求:支持高速数据传输(如40G/100G/400G以太网),满足高密度布线需求,同时需配备完善的线缆管理系统(如理线器、标识系统)以应对复杂布线环境。

中密度配线架

适用场景:中小型企业网络、办公室、学校等布线规模较小、对端口密度要求不高的场景。

性能需求:满足基础网络传输需求(如1G/10G以太网),布线复杂度较低,维护管理相对简单。

三、成本与扩展性

高密度配线架

成本:初期投资较高(因材料、工艺及模块化设计),但长期来看可降低空间占用成本和运维成本。

扩展性:模块化设计支持灵活扩展(如单独更换模块),但需预留足够机柜空间以应对未来扩容需求。

中密度配线架

成本:初期投资较低,适合预算有限的场景。

扩展性:扩展能力有限,若需增加端口数量,可能需要更换整个配线架或占用额外机柜空间。

四、结构设计与维护管理

高密度配线架

结构设计:采用模块化设计,支持热插拔和快速更换,便于维护和升级。

维护管理:需配备专业工具和培训人员,以应对高密度布线带来的复杂性。

中密度配线架

结构设计:通常为一体式设计,端口布局固定,维护管理相对简单。

维护管理:无需专业工具,普通技术人员即可完成日常维护。

审核编辑 黄宇

-

配线架

+关注

关注

0文章

286浏览量

9112

发布评论请先 登录

高密度配线架面板

高密度布线在数据中心建设中的挑战与应对策略

MPO分支光缆:高密度光纤布线的核心组件

高密度配线架特殊场景与前沿趋势

光纤配线架密度演进路程

高密度PCBA洗板工艺全解析,这些细节决定成败!

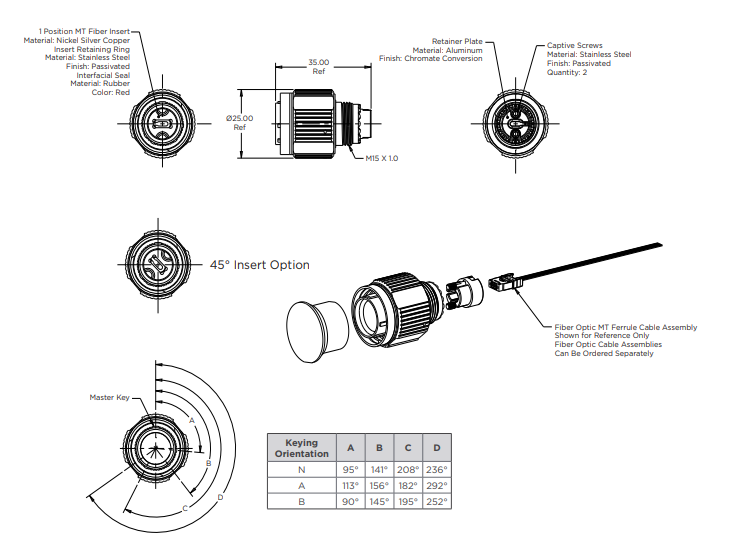

TF-047 微同轴电缆:高密度应用的理想之选

Amphenol FCI Basics DensiStak™ 板对板连接器:高速高密度连接解决方案

高密度光纤布线:未来的数据通信解决方案

哪种工艺更适合高密度PCB?

基于TE Connectivity VITA 87高密度圆形MT连接器的技术解析与应用指南

高密度配线架和中密度的区别

高密度配线架和中密度的区别

评论