共读好书

翟培卓,洪根深,王印权,李守委,陈鹏,邵文韬,柏鑫鑫

(中国电子科技集团公司第五十八研究所)

摘要:

倒装焊封装过程中,底部填充胶的流动性决定了填充效率,进而影响生产效率及成本。通过对比接触角和底部填充胶流动时间,研究了等离子清洗及点胶轨迹对底部填充胶流动性的影响。结果表明:经微波等离子清洗后,水及底部填充胶在陶瓷基板表面的浸润性均有所提高;微波等离子清洗还能促进底部填充胶在芯片和陶瓷基板之间的流动。I形点胶轨迹对应的流动时间最长,而U形点胶轨迹的流动时间最短。因此适当增加点胶轨迹的总长度,可以有效提高底部填充胶的填充效率。

0引言

倒装焊封装技术以倒装芯片的凸点作为连接媒介,采用回流焊、热压焊等实现芯片与基板的电路互连,是高速、高密度的主流封装技术之一[1-2]。在倒装焊封装过程中,由于芯片与基板的热膨胀系数不匹配,在温度变化时会出现较大的热应力,所以往往需要在芯片与基板之间填充底部填充胶来起到加固的作用[3]。

底部填充的方式一般分为两种:流动底部填充和非流动底部填充[4-5]。前者是在凸点回流后将底部填充胶注到芯片边缘,借助液体的毛细作用将芯片与基板之间填满;而后者是先将底部填充胶涂在基板表面适当位置,再安装倒装芯片。由于流动底部填充对于设备的要求不高且操作简单,被广泛应用于倒装焊封装。

等离子清洗是半导体行业中常用的表面处理手段,进行等离子清洗可直接改变基板表面状态,进而影响底部填充胶的流动性[6]。同时,不同点胶轨迹会影响底部填充胶注入位置的初始条件,从而也会对底部填充胶在芯片底部的流动性造成影响[7-8]。底部填充胶在基板上的流动性决定了填充效率,进而关系到工程生产效率及成本。因此,研究等离子清洗及点胶轨迹对底部填充胶流动性的影响具有重要意义。

1实验材料及方法

1. 1实验材料

选用Al2O3陶瓷基板,实验前基板表面不经任何处理,保持原始素面;陶瓷基板存储环境温度为20~26 ℃,存储环境湿度为40%~60%。选用的底部填充胶在25℃下黏度为50 Pa·s,填充料为SiO2颗粒,填充颗粒尺寸为2~10 μm,填充颗粒质量分数为60%,在-40 ℃下存储。

1. 2实验方法

首先采用回流焊的方式,将倒装芯片贴装在基板焊盘区(图1)。倒装芯片尺寸为10. 3 mm ×10. 3 mm×0. 5 mm,对应的凸点直径为160 μm,节距250 μm,凸点总数为1 296个。首个样品经破坏性拉脱芯片实验后,在显微镜下观察确认:采用离心清洗机在转速800 r /min、水温50 ℃下清洗20min,可以洗净残留助焊剂。后续样品均采用上述参数进行助焊剂清洗。

然后将陶瓷基板分为两组:一组不经任何表面处理,保持原始素面;另一组进行微波等离子清洗。微波等离子清洗的功率为800 W,先用O2清洗5 min,再用体积分数为90%N2+10%H2的混合气清洗5 min,气体流量均为300 mL/min。接着对两组基板样品用接触角测量仪分别测量水和底部填充胶对应的接触角,并采用I形、L形和U形3种轨迹在芯片边缘位置进行点胶实验,每项实验均采用3个样品,记录底部填充胶填满芯片底部所用的流动时间。

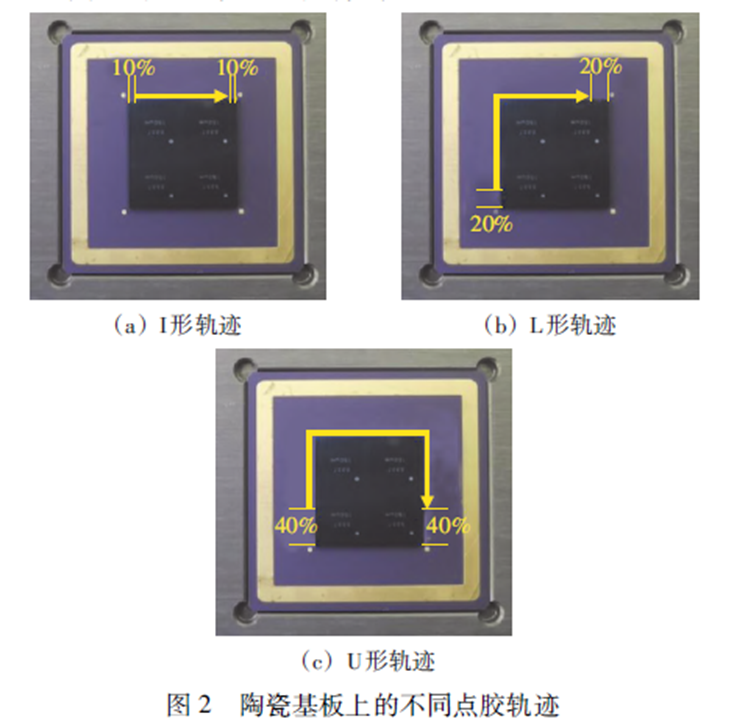

I形、L形和U形3种点胶轨迹均一次性完成,点胶量为19 mg。基于工程经验,为了缓解底部填充胶在芯片边缘填充速度过快的现象以实现较好的底部填充效果,3种轨迹头尾分别空出单边长度的10%、20%和40%,如图2所示。在点胶过程中,底部填充加热平台温度保持在110 ℃。

2分析与讨论

2. 1等离子清洗对陶瓷基板浸润性的影响

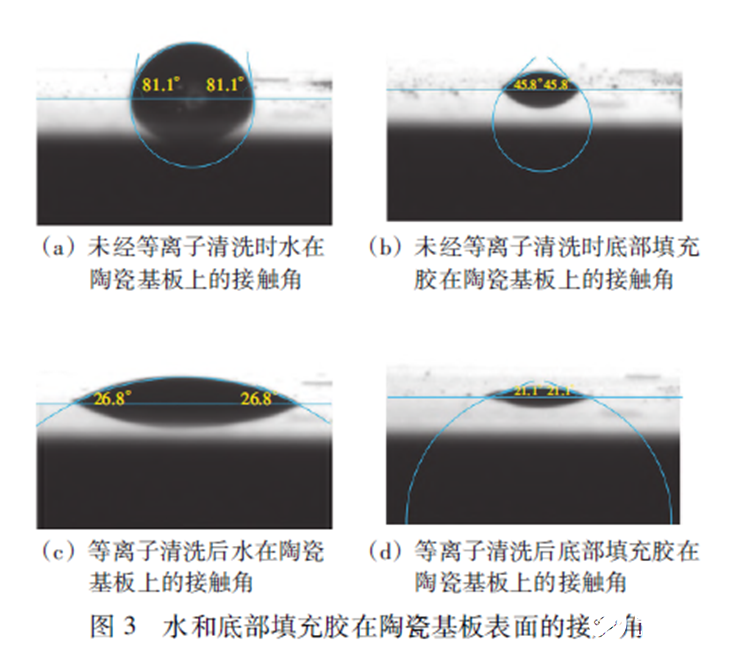

为了确认不同表面处理的陶瓷基板表面的浸润性,分别对未经等离子清洗和等离子清洗后的陶瓷基板进行接触角测量实验。图3所示分别为未经等离子清洗和等离子清洗后,水和底部填充胶在陶瓷基板表面接触瞬间的接触角照片。可以看出未经等离子清洗时,水和底部填充胶在陶瓷基板表面的接触角分别为81. 1°和45. 8°;在等离子清洗后,水和底部填充胶在陶瓷基板表面的接触角均有所减小,分别变为26. 8°和21. 1°。这一方面是由于经等离子清洗后陶瓷基板表面的亲水基增多、憎水基减少,另一方面是由于等离子清洗在一定程度上减少了陶瓷表面的残留污染物,最终提高了水和底部填充胶在陶瓷表面的浸润性[9-10]。

2. 2底部填充胶的流动性对比

经实验测得,在采用I形、L形和U形点胶轨迹情况下,未经等离子清洗时的底部填充胶平均流动时间分别为23、21和18 s;而在等离子清洗后分别为21、16和14 s。

可见,陶瓷基板经等离子清洗之后,不论是I形、L形还是U形点胶轨迹,底部填充胶的流动时间明显减少。另外,I形点胶轨迹对应的流动时间最长,L形轨迹的流动时间稍短,而U形点胶轨迹的流动时间最短。对于等离子清洗之后的陶瓷基板,L形轨迹和U形轨迹比I形轨迹的流动时间分别缩短了23%和33%。换算成单位小时产能,L形轨迹和U形轨迹对应的填充效率相比于I形轨迹分别提高了31%和50%。

底部填充胶主要依靠毛细作用深入到芯片与基板之间的缝隙处。若采用Washburn模型[11],假设底部填充胶为不可压缩的牛顿流体,且底部填充胶在芯片和基板之间的流动为稳定的二维层流流动,那么底部填充胶的流动可以等效为芯片与基板间的压力差Vp的作用[12],即

式中: σ为底部填充胶前端与空气的表面张力; θ为底部填充胶与基板形成的接触角; h为芯片与基板间的缝隙宽度。

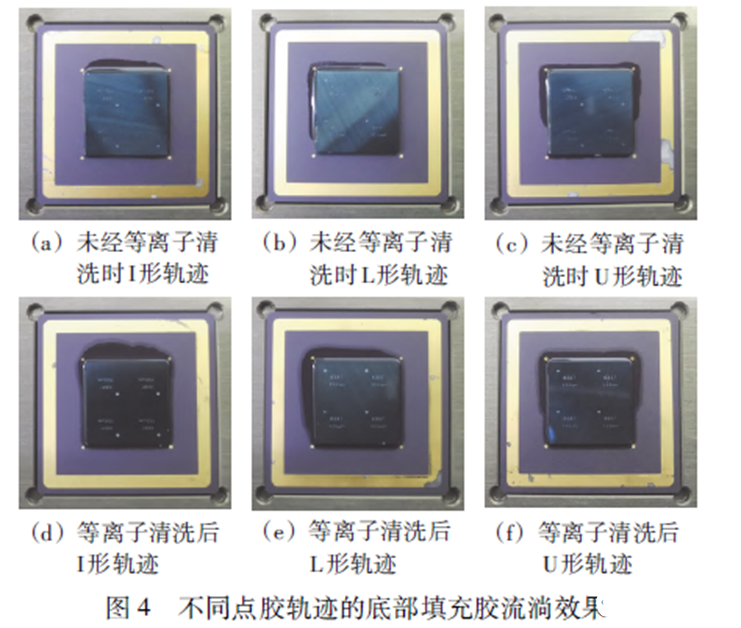

由图3可知等离子清洗可减小底部填充胶在陶瓷基板上的接触角,所以等离子清洗之后可以获得更大的压力差,即底部填充胶获得的推力变大,从而促进底部填充胶在芯片底部的流动,在同样点胶轨迹下减少流动时间。而基板在未经等离子清洗时和等离子清洗后的不同点胶轨迹的流淌效果如图4所示。

从图4中可以看出,在陶瓷基板进行等离子清洗之后,无论何种点胶轨迹,底部填充胶在陶瓷基板上的扩散宽度均偏大,这也是由于等离子清洗可减小底部填充胶在陶瓷基板上的接触角导致。此外,从点胶轨迹的总长度上看,U形轨迹最长,其次是L形轨迹,最短的是I形轨迹。轨迹总长度越长,相当于增大了底部填充胶的入口,在相同的压力差下可以更快地流满芯片底部,所以U形轨迹的流动时间最短。

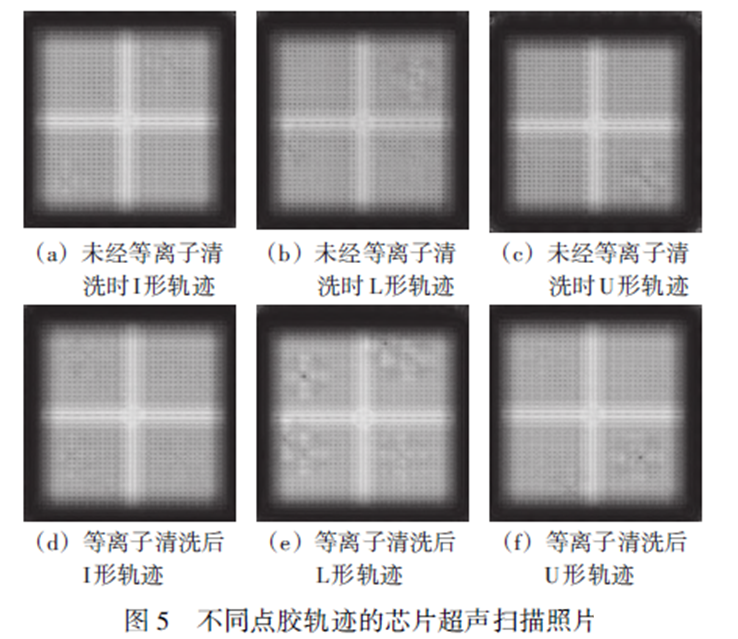

2. 3超声扫描结果对比

为了检验底部填充胶的填充效果,对基板在未经等离子清洗和等离子清洗后的不同点胶轨迹的芯片进行了超声扫描检测。超声扫描采用反射模式( C扫描模式),对芯片附近的底部填充层进行逐行扫描,得到超声扫描照片如图5所示。从图5中可以看出,对于本文所采用的芯片,无论是否进行了等离子清洗,采用I形、L形和U形点胶轨迹的底部填充胶与芯片或陶瓷基板均未发生分层和孔洞缺陷。

3结论

陶瓷基板经微波等离子清洗后,水及底部填充胶在其表面的接触角均有减小,浸润性均有所提高。从而,微波等离子清洗可以促进底部填充胶在芯片和陶瓷基板之间的流动,减少流动时间。另外,I形点胶轨迹对应的流动时间最长,L形轨迹的流动时间稍短,而U形点胶轨迹的流动时间最短。适当增加点胶轨迹的总长度,可以有效减少底部填充胶的流动时间,提高填充效率,从而提升工程生产效率并降低生产成本。

审核编辑 黄宇

-

等离子

+关注

关注

2文章

276浏览量

31599 -

倒装芯片

+关注

关注

1文章

124浏览量

16873 -

陶瓷基板

+关注

关注

5文章

275浏览量

12434

发布评论请先 登录

超细间距倒装芯片灌封胶渗透与空洞控制 |铬锐特实业

汉思新材料获得芯片底部填充胶及其制备方法的专利

如何提高光刻胶残留清洗的效率

汉思新材料:底部填充胶可靠性不足如开裂脱落原因分析及解决方案

汉思新材料|芯片级底部填充胶守护你的智能清洁机器人

等离子清洗及点胶轨迹对底部填充胶流动性的影响

等离子清洗及点胶轨迹对底部填充胶流动性的影响

评论