5月6日,负责制定PCle与相关标准的组织PCI-SIG正式发布PCIe 8.0 规格的 0.5 草案版本。根据 0.5 版规格,PCIe 8.0 将维持 256 GT/s 传输速率目标,在 x16 配置下可提供最高 1TB/s 的双向带宽。

PCIe 8.0 规范的目标,是为人工智能、数据中心、高速网络、边缘计算、量子计算等数据密集型应用市场,提供所需的高带宽与低时延能力。

PCIe 8.0 规范目标已锁定核心概念与主要机制,并涵盖电气、逻辑、兼容性与软件等架构层面,PCI-SIG 成员也能开始进行原型开发并提交最终提案。根据规格,PCIe 0.5 版草案将维持 256 GT/s 传输速率、采用 PAM4 讯号技术、搭配前向错误修正(FEC)、使用 Flit Mode 编码、导入提升带宽效率的协议优化、保持向下兼容性,并采用目前正在评估中的新型连接器技术。

PCIe 8.0 规范目标有六项主要内容:

1、实现256.0GT/s原始比特速率,x16 通道配置下双向带宽最高达 1.0TB/s

2、评估新一代连接器技术

3、确保达成延迟、前向纠错(FEC)及可靠性指标

4、保持与历代 PCIe 技术向后兼容

5、通过协议优化进一步提升带宽

6、采用多项新技术方案降低功耗

值得关注的是,PCI-SIG 持续评估新型连接器技术,意味着现有铜线物理层技术已逐渐逼近极。。早在 PCIe 5.0 与 PCIe 6.0 时代,讯号损耗(loss budget)、串扰(crosstalk)与反射(reflection)就已成为重大挑战。而到了 PCIe 8.0 的 256 GT/s 传输速度后,这些问题可能进一步恶化。

在此情况下,传统 PCIe 插槽与主板走线可能无法在可接受的功耗与延迟下维持良好讯号完整性,因此 PCI-SIG 可能考虑重新设计 PCIe 插槽,如使用更高级材料与更严格公差或再次缩短电气传输路径,同时增加 redriver 数量以维持讯号质量。

这是该规范的首个正式草案,吸纳了 2025 年 9 月0.3 版本草案发布后收到的所有会员反馈意见。据悉,目前 AMD、英特尔、NVIDIA 等大型硬件厂商及 IP 与 PHY 供货商,已开始开发早期原型设计与架构,虽然仍需预留部分规格变动空间,但整体规格已成熟到足以正式启动研发工作。

本次草案发布后,PCIe 8.0 规范仍按原计划推进,预计将于 2028 年正式完整版发布。

-

人工智能

+关注

关注

1821文章

50385浏览量

267109

发布评论请先 登录

智能手机存储迈入2TB时代

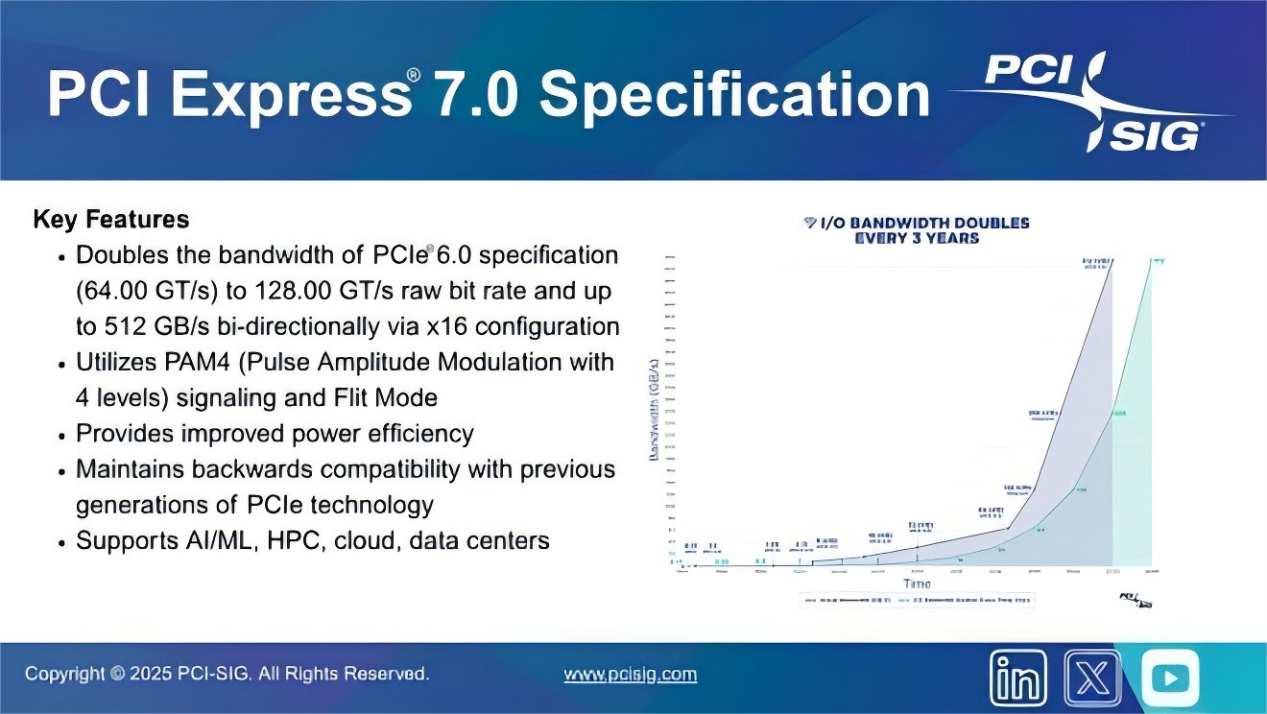

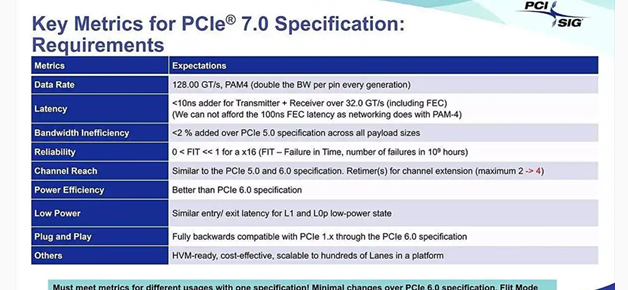

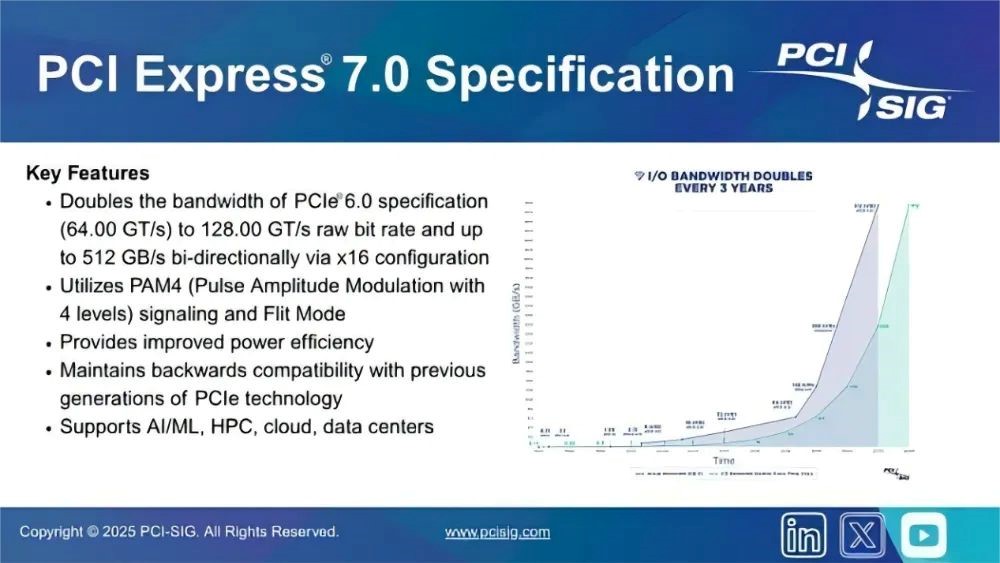

PCIe 7.0发布:16通道双向512GB/s,拥抱光纤未来

【PCIe 6.0 连载 · 下篇】测试才是关键:PCIe 6.0 如何保证稳定量产?(行业干货)

今日看点:铠侠:300元1TB SSD时代结束;苏大维格:常州维普产品已进入头部晶圆厂和掩膜版厂商量产线

简单认识Metorage 1TB MicroSD工业级存储卡

PCIe 5.0 8TB SSD挺进消费级市场

Xilinx高性能NVMe Host控制器IP+PCIe 3.0软核控制器IP,纯逻辑实现,AXI4和AXI4-Stream DMA接口,支持PCIe 3.0和4.0

PCIe 7.0技术细节曝光

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

PCIe 8.0 规范公布:1TB/s 带宽、256GT/s 速率

PCIe 4.0/5.0仍是主流!三家SSD企业抢滩高性能存储市场,新品相继亮相

频宽飙升到1TB/s! PCIe 8.0规范0.5版正式发布,2028年最终定案

频宽飙升到1TB/s! PCIe 8.0规范0.5版正式发布,2028年最终定案

评论