昨日,据报道日月光半导体公布了VIPack先进封装平台的重要进展——微间距芯粒互连技术。这一技术旨在满足AI应用对Chiplet集成不断增长的需求,相比传统实现更大创新性及微缩价值。

这项技术采用新型金属叠层于微凸块之上,达成20μm(2*10-5米)芯片与晶圆之间的极致间距,较从前方案减少了一半。此举大幅度增强了硅-硅互连能力,对其它开发过程大有裨益。

随着Chiplet设计趋势不断演进,半导体互连带宽呈爆炸式增加,使以往难以想象的IP模块分割成为可能。

该项微间距互连技术使3D整合及更高I/O密度的存储器耦合0成为可能。这一技术的推广拓宽了Chiplet的应用领域,包括AI、移动处理器以及MCU等关键产品。

日月光集团研发处长李长祺总结道:“硅与硅互连已经经历了焊锡凸块向微凸块的升级。随着人工智,能时代的来临,对更高级别的互连技术的需求也愈发迫切。借助新的微间距互连技术,我们正致力突破chiplet整合壁垒,并将持续挑战技术极限以满足市场需求。”

-

半导体

+关注

关注

336文章

30034浏览量

258685 -

日月光

+关注

关注

0文章

157浏览量

20090 -

先进封装

+关注

关注

2文章

521浏览量

974

发布评论请先 登录

Chiplet核心挑战破解之道:瑞沃微先进封装技术新思路

强强合作 西门子与日月光合作开发 VIPack 先进封装平台工作流程

借助Arm芯粒技术构建计算未来

台积电日月光主导,3DIC先进封装联盟正式成立

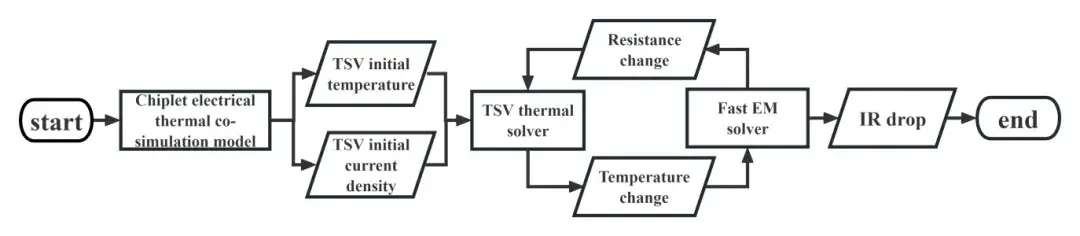

微电子所在芯粒集成电迁移EDA工具研究方向取得重要进展

华大九天推出芯粒(Chiplet)与2.5D/3D先进封装版图设计解决方案Empyrean Storm

日月光推出先进封装平台新技术:微间距芯粒互连技术

日月光推出先进封装平台新技术:微间距芯粒互连技术

评论