首先哪些因此会导致时钟skew过大呢?

不合理的时钟结构

时钟同时驱动I/O资源和Slice资源

时钟跨die

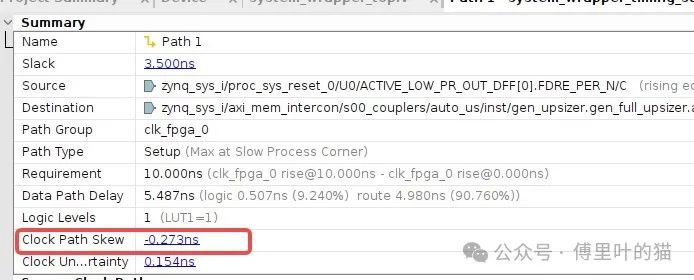

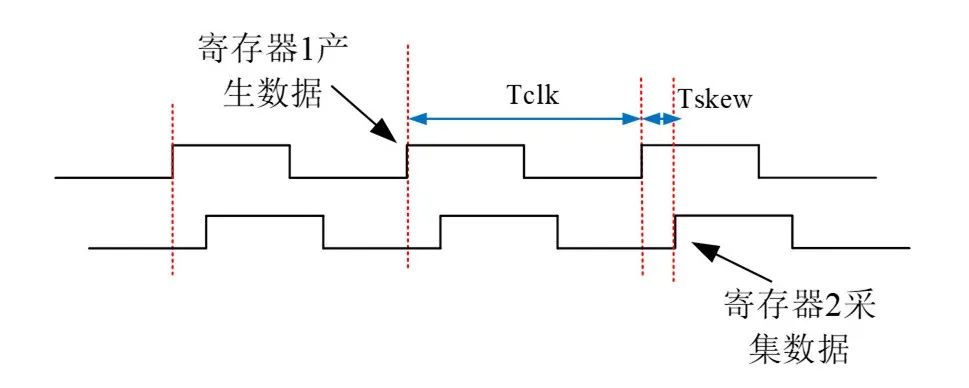

在时序报告中,会显示出clock path skew,如果时钟偏移超过0.5ns,就需要额外关注了。

书中列举了几个优化skew的方法:

移除时钟路径上多余的时钟buffer,如果出现了级联时钟Buffer,势必会导致时钟路径上的延迟增大。

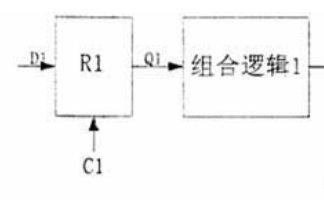

移除时钟路径上的组合逻辑,一旦时钟路径上出现了组合逻辑,就意味着时钟布线采用了“常规布线资源+专用布线资源”的组合形式,从而显著增大了时钟延迟且时钟skew无法预测。同时,相比于专用时钟布线资源,常规布线资源对噪声更加敏感,这会使时钟质量下降。

输入时钟从clock capable的管脚输入,否则还是会出现“常规布线资源+专用布线资源”的组合形式。

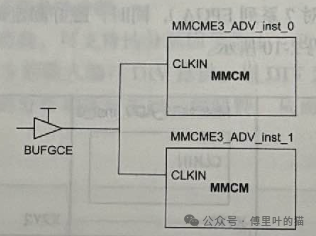

如果设计中出现并行的MMCM/PLL时,应合理设置CLOCK_DEDICATED_ROUTE的值。

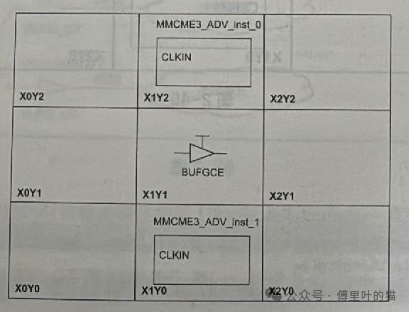

如果BUFGCE和两个MMCM位于同列相邻的时钟区域,那么应为约束为SAME_CMT_COLUMN或BACKBONE,同时将MMCM的位置固定下来:

#FORUltraScale/UltraScale+ set_propertyCLOCK_DEDICATED_ROUTESAME_CMT_COLUMN[get_nets-of[get_pinsBUFG_inst/O]] #FOR7series set_propertyCLOCK_DEDICATED_ROUTEBACKBONE[get_nets-of[get_pinsBUFG_inst/O]] set_propertyLOCMMCM3_ADV_X1Y2[get_cellsMMCM3_ADV_inst_0] set_propertyLOCMMCM3_ADV_X1Y0[get_cellsMMCM3_ADV_inst_1]

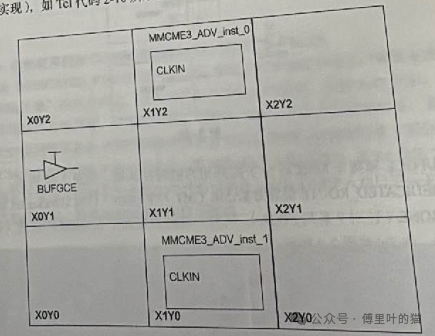

如果BUFGCE和两个MMCM位于不同列但相邻的时钟区域,那么应该设为ANY_CMT_COLUMN和FALSE。

#FORUltraScale/UltraScale+ set_propertyCLOCK_DEDICATED_ROUTEANY_CMT_COLUMN[get_nets-of[get_pinsBUFG_inst/O]] #FOR7series set_propertyCLOCK_DEDICATED_ROUTEFALSE[get_nets-of[get_pinsBUFG_inst/O]] set_propertyLOCMMCM3_ADV_X1Y2[get_cellsMMCM3_ADV_inst_0] set_propertyLOCMMCM3_ADV_X1Y0[get_cellsMMCM3_ADV_inst_1]

对于7系列FPGA,避免使用BUFIO/BUFR/BUFH来驱动分散在不同时钟域内的逻辑。要评估设计中区域时钟缓冲器负载的个数,以保证这些负载可以被放置在一个时钟区域内。

对于UltraScale/UltraScale+和Versal的FPGA,避免使用MMCM/PLL对来自BUFG_GT的输出时钟执行简单的分频,可以使用BUFGCE_DIV、MBUFG这些带有分频功能的时钟BUFFER来代替。

对于UltraScale/UltraScale+和Versal的FPGA,对关键的同步跨时钟域路径添加CLOCK_DELAY_GROUP约束。什么是同步跨时钟域路径呢,比如MMCM输出的两个同步时钟。

对于UltraScale/UltraScale+的FPGA,修改时钟根节点的位置。Vivado在布局阶段会自动给每个时钟分配根节点的位置,以获取最佳的时序性能。通常情况下,时钟根节点位于其驱动负载的中心位置,如果不是,可以使用USER_CLOCK_ROOT调整。

避免关键路径穿越SLR或输入输出列。

对于UltraScale/UltraScale+的FPGA,使用CLOCK_LOW_FANOUT属性使时钟网线驱动的负载位于同一个时钟区域内。

-

FPGA

+关注

关注

1655文章

22283浏览量

630289 -

时钟缓冲器

+关注

关注

2文章

221浏览量

51786 -

Vivado

+关注

关注

19文章

846浏览量

70474

原文标题:FPGA中降低时钟skew的几种方法

文章出处:【微信号:傅里叶的猫,微信公众号:傅里叶的猫】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Skew definitions

Skew Correction Using Delay Li

时序分析之useful skew的作用分析

同步电路设计中CLOCK SKEW的分析说明

哪些因此会导致时钟skew过大呢?FPGA中降低时钟skew的几种方法

哪些因此会导致时钟skew过大呢?FPGA中降低时钟skew的几种方法

评论