FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据不同需要编程,实现不同的功能。在FPGA中,时钟是很重要的一个因素,而时钟配置芯片则是为了提供时钟信号而存在。

时钟是FPGA中非常重要的因素,因为FPGA必须在时钟边沿上完成一次操作。时钟信号决定了FPGA内部计算和通讯的速度,因此时钟信号的稳定性和精度至关重要。

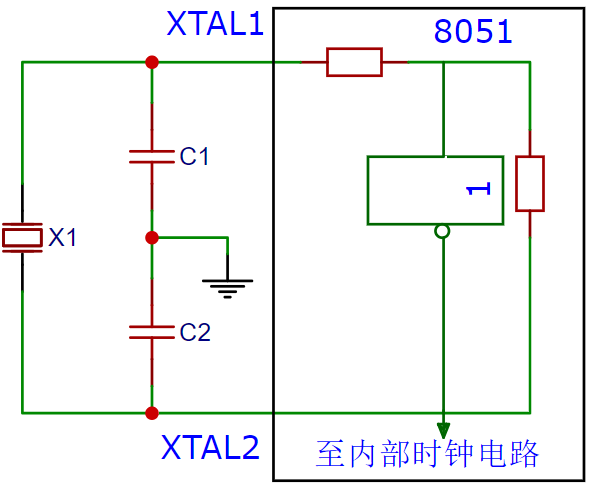

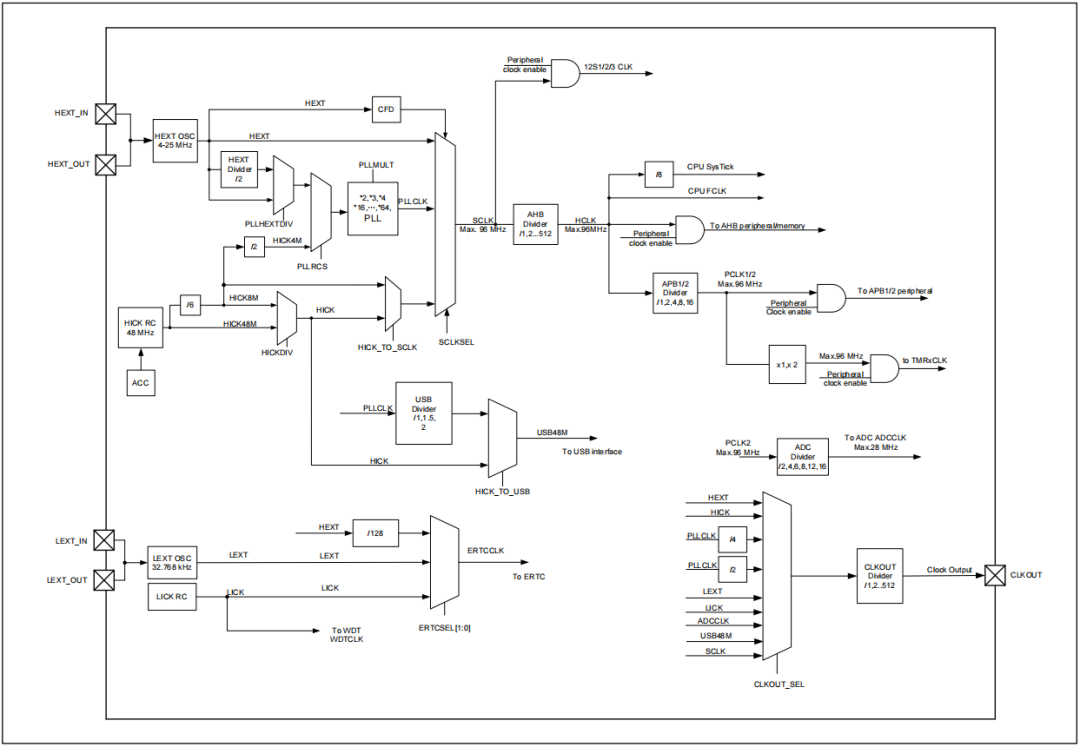

FPGA实现时钟同步通常有两种方式:一种是通过外部时钟输入,即将外部稳定的时钟信号输入FPGA内部;另一种是通过FPGA内部生成时钟信号。对于外部时钟信号输入的FPGA,需要一个时钟配置芯片来提供稳定的时钟信号。时钟配置芯片也称为时钟管理器,主要作用是提供稳定和精准的时钟信号,以确保FPGA内部的逻辑电路能够正常工作。

时钟配置芯片与FPGA的关系非常类似于电池与电路板的关系。电路板需要电池提供电能,而时钟配置芯片则需要提供时钟信号,这样FPGA才能正常工作。时钟配置芯片中包含一个稳定高精度的振荡器,利用这个振荡器提供的时钟信号对FPGA进行时钟同步。

时钟配置芯片与FPGA之间的通信主要是通过可编程晶体管(FPGA在内部是由大量的可编程晶体管构成)进行的。时钟配置芯片对FPGA的时钟信号进行控制和管理,从而确保FPGA内部的逻辑电路与时钟信号同步。

在FPGA内部,由于逻辑电路较多,每个逻辑部件都需要时钟信号进行同步。如果时钟信号不稳定或精度不够,就会导致FPGA内部的逻辑部件工作不正常。而使用时钟配置芯片可以提供稳定的同步时钟信号,从而确保FPGA内部的逻辑电路正常工作。

时钟配置芯片还能对时钟信号的频率进行控制,例如提供多路时钟输出,并可以对时钟频率进行分频。通过时钟配置芯片的控制,可充分利用FPGA内部的逻辑电路资源,更合理地分配逻辑资源。

总之,FPGA与时钟配置芯片之间的关系是密不可分的。时钟配置芯片的存在可以提供稳定和精准的时钟信号,确保FPGA内部逻辑部件同步正常。在FPGA系统设计中,时钟配置芯片和FPGA的选择配套是非常关键的,必须根据具体应用场景进行选择,来保证FPGA系统的稳定性和可靠性。

-

FPGA

+关注

关注

1603文章

21328浏览量

593251 -

晶体管

+关注

关注

76文章

9056浏览量

135230 -

时钟芯片

+关注

关注

2文章

229浏览量

39577

发布评论请先 登录

相关推荐

为什么AD7606有时候读的数据全为0,有时候正常采集?

AD9266的内部时钟分配关系是什么样的?它的SPI接口和内部寄存器是不是也要有了参考时钟之后才能正常工作?

用FPGA的锁相环PLL给外围芯片提供时钟

菱沃铂MCU的时钟配置

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?

评论