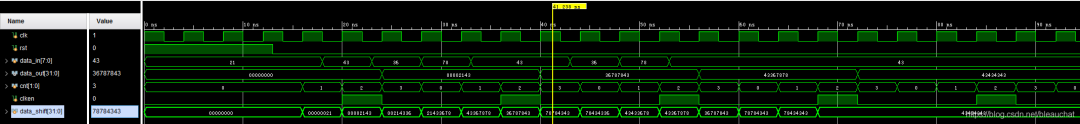

verilog模型举例

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:verilog的时钟分频与时钟使能

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22504浏览量

639341

原文标题:verilog的时钟分频与时钟使能

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

AT32F011时钟配置说明

_conf.h 文件来进行使用)。

5. hext bypass:高速外部时钟的旁路使能。

6. pllhextdiv:点选框,当 HEXT 作为 PLL 时钟源时,可配置输入频率为

发表于 03-29 10:34

CDC5801A:低抖动时钟倍频器与分频器的卓越之选

CDC5801A:低抖动时钟倍频器与分频器的卓越之选 在电子工程师的日常设计工作中,时钟信号的稳定性和精准度至关重要。今天,我们就来详细探讨一款功能强大的时钟芯片——CDC5801A,

深入剖析LMK01000:高性能时钟缓冲、分频与分配器

GHz高性能时钟缓冲、分频与分配器,能为系统提供出色的时钟解决方案。 文件下载: lmk01020.pdf 一、产品特性亮点 低抖动性能 LMK01000系列具有仅30 fs的附加抖动(100 Hz到20 MHz),这一特性使

LMK01801双时钟分频缓冲器:高精度时钟解决方案

LMK01801双时钟分频缓冲器:高精度时钟解决方案 引言 在电子设计领域,时钟信号的精准分配和分频对于系统的稳定运行至关重要。今天要给大家

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析 在电子设计领域,时钟信号的处理至关重要,它直接影响着整个系统的性能和稳定性。今天,我们就来深入探讨一款高性能的时钟缓冲及

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析 在电子设计领域,时钟信号的处理至关重要,它直接影响着系统的性能和稳定性。TI推出的LMX1214低噪声、高频时钟缓冲器和

验证CW32各时钟频率输出方法

/RC10K 时钟信号,时钟输出到 MCO_OUT 引脚前可通过预分频器进行分频(有效分频系数为 1、2、8、64、128、256、512、

发表于 12-12 06:11

CDC5801A低抖动时钟倍频/分频器技术文档总结

CDC5801A器件提供从单端参考时钟 (REFCLK) 到差分输出对 (CLKOUT/CLKOUTB) 的时钟乘法和分频。乘法和分频端子 (MULT/DIV0:1) 提供倍频比和

第三十一章 MCO——PA8从主频分频输出

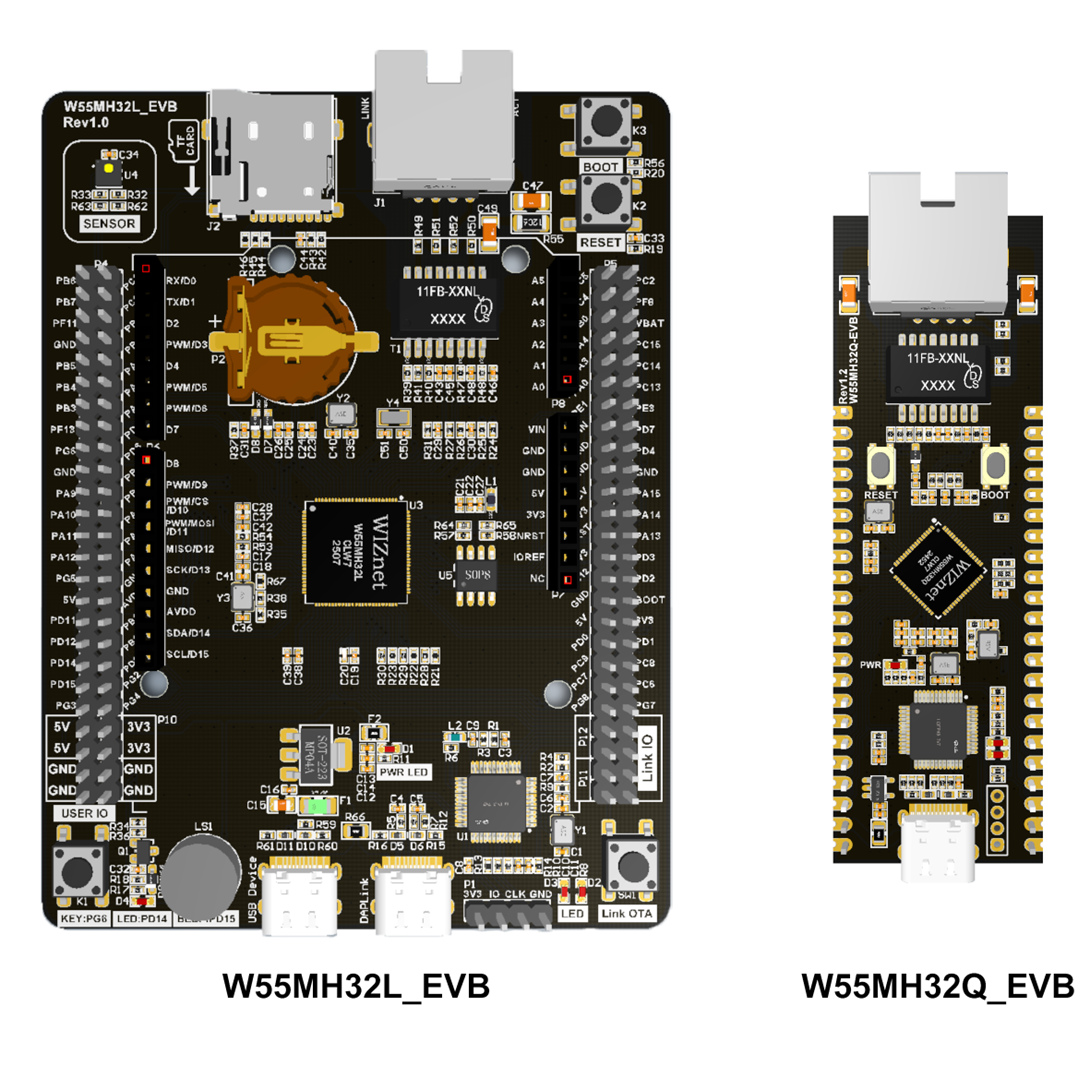

本篇文章介绍了W55MH32 的 MCO 从 PA8 输出内部时钟,时钟源有 HSI、HSE 等,经分频后输出。其用于为外部设备供时钟、多芯片同步等,配置需

时钟电路的组成与设计要点介绍

在数字电子系统的运行中,时钟电路掌控着各部件协同工作的节奏。它通常由时钟发生器、时钟分频器、时钟缓冲器等核心部分构成,这些组件各司其职,共同

verilog的时钟分频与时钟使能

verilog的时钟分频与时钟使能

评论