时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在FPGA的设计中,分频时钟和源时钟的skew不容易控制,难以保证分频时钟和源时钟同相。故此推荐采用使用时钟使能的方法,通过使用时钟使能可以避免时钟“满天飞”的情况,进而避免了不必要的亚稳态发生,在降低设计复杂度的同时也提高了设计的可靠性。

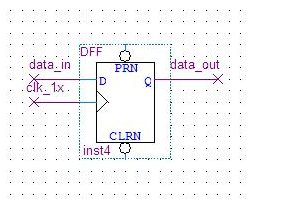

我们可以利用带有使能端的D触发器来实现时钟使能的功能。

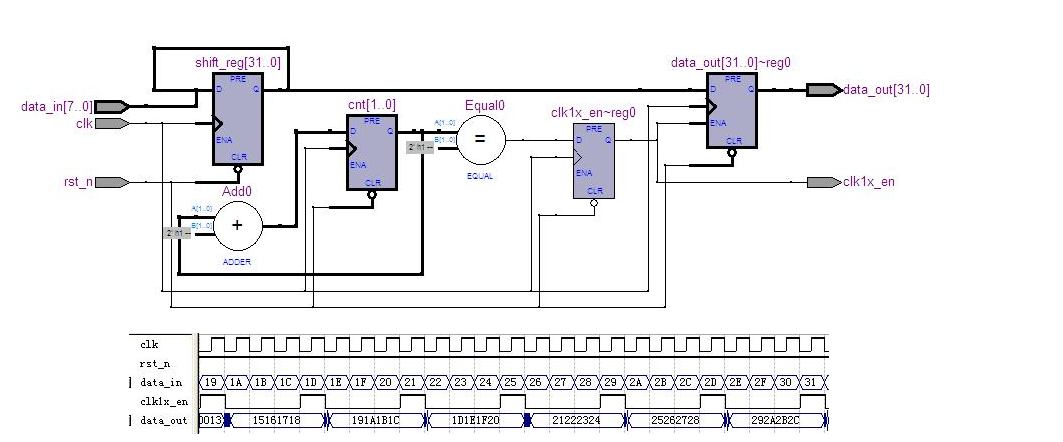

在上图中clk1x是CLK的四分频后产生的时钟,clk1x_en是与clk1x同频的时钟使能信号,用clk1x_en作为DFF的使能端,D端的数据只有在clk1x_en有效地时候才能打入D触发器,从而在不引入新时钟的前提,完成了下图电路一致的逻辑功能。

在某系统中,前级数据输入位宽为8,而后级的数据输出位宽32,我们需要将8bit的数据转换成32bit的数据,因此后级处理的时钟频率为前级的1/4,若不使用时钟时能,则就要将前级时钟进行4分频来作为后级处理的时钟,这种设计方法会引入新的时钟域,为了避免这种情况,我们采用了时钟时能的方法来减少设计的复杂度。

module gray

(

input clk,

input rst_n,

input [7:0] data_in,

output reg [31:0] data_out,

output reg clk1x_en

);

reg [1:0] cnt;

reg [31:0] shift_reg;

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

cnt <= 2'b0;

else

cnt <= cnt +1'b1;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

clk1x_en <= 1'b0;

else if(cnt ==2'b01)

clk1x_en <= 1'b1;

else

clk1x_en <= 1'b0;

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

shift_reg <= 32'b0;

else

shift_reg <= {shift_reg[23:0],data_in};

end

always @ (posedge clk,negedge rst_n)

begin

if(!rst_n)

data_out<= 32'b0;

else if(clk1x_en==1'b1)//仅在clk1x_en为1时才将shift_reg的值赋给data_out

data_out<=shift_reg;

end

endmodule

编辑:hfy

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22508浏览量

639481 -

D触发器

+关注

关注

3文章

181浏览量

49908 -

时钟电路

+关注

关注

10文章

247浏览量

53954

发布评论请先 登录

相关推荐

热点推荐

Xilinx FPGA中的混合模式时钟管理器MMCME2_ADV详解

在 FPGA 的浩瀚宇宙中,时钟系统不仅是驱动逻辑运转的“心脏”,更是决定系统稳定性与性能上限的“指挥棒”。对于 Xilinx 7 系列 FPGA 开发者而言,如果仅满足于使用 Clo

浅谈FPGA的时钟输入要求

Virtex-7 FPGA的时钟输入主要通过其全局时钟缓冲器(BUFG、BUFH等)和时钟管理模块(MMCM、PLL)来处理。对输入时钟的要

Xilinx FPGA中IDELAYCTRL参考时钟控制模块的使用

IDELAYCTRL 是 Xilinx FPGA(特别是支持高速 I/O 的系列,如 Virtex-5/6/7、Kintex-7、Artix-7、Spartan-6/7 等)中用于管理和校准输入延迟模块(IDELAYE2/IDELAYE3)的必须存在的参考时钟控制模块。

如何使能cw32f030看门狗复位?

= 0xFFF;

IWDT_Init( IWDT_InitStruct);

IWDT_Cmd();

while(!CW_IWDT->SR_f.RUN);

IWDT_Refresh();

还需要使能时钟信号

__RCC_IWDT_CLK_ENABLE();

发表于 01-23 07:01

数字IC/FPGA设计中的时序优化方法

在数字IC/FPGA设计的过程中,对PPA的优化是无处不在的,也是芯片设计工程师的使命所在。此节主要将介绍performance性能的优化,如何对时序路径进行优化,提高工作时钟频率。

NVIC中断使能与禁止使能

ARM®Cortex-M0+ 处理器支持最多 32 个外部中断源,分别对应中断使能设置寄存器 NIVC_ISER 的 32 个使能位,和中断使

发表于 11-13 07:14

求助,关于全局中断使能的问题求解

各位朋友大家好,我最近在使用蜂鸟的板子进行开发时,遇到了这样的问题:我的程序每次运行到使能全局中断的时候,就像进入了死循环一样,出不去了,如上图,首先先打印“GI_EN begin!”这里是可以

发表于 11-07 06:37

时钟移项电路加速模块的设计

FPGA引脚中,在基于逻辑的边沿变化采集时并不能对准数据稳定的时刻,而不能正确采集到数据。为了在时钟跳变时能对准数据的稳定时刻,通常在设计时可以采用以下方法:专用IP核延迟、锁相环移相和门电路

发表于 10-29 07:38

PLL技术在FPGA中的动态调频与展频功能应用

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在

Leadway电源模块的使能信号是如何作用的

在电机控制系统中,Leadway电源模块的使能信号(Enable Signal)是协调电源启停与电机驱动的核心控制逻辑之一。其作用不仅限于简单的通断控制,更涉及系统安全、能耗管理及多设备协同。

发表于 05-15 09:38

电容在时钟电路中的应用有哪些

在时钟电路精密的运行体系中,电容器扮演着不可或缺的角色。从净化信号到稳定传输,从调节频率到优化电源,电容以其独特的电气特性,在不同环节发挥关键作用。本文将深入解析电容在时钟

时钟电路与晶振电路两者的区别有哪些

在数字电子系统设计中,时钟电路与晶振电路是两个高频出现的概念。虽然二者紧密相关且常被协同讨论,但从功能定位、电路构成到应用场景都存在本质差异

FPGA的设计中的时钟使能电路

FPGA的设计中的时钟使能电路

评论