电子发烧友网报道(文/李宁远)提及芯片制造,首先想到的自然是光刻机和光刻技术。而众所周知,EUV光刻机产能有限而且成本高昂,业界一直都在探索不完全依赖于EUV光刻机来生产高端芯片的技术和工艺。纳米压印光刻技术NIL在这条赛道上备受关注,是最有机会率先应用落地的技术路线。

今年早些时候,根据英国金融时报的报道,负责监督新型光刻机开发的佳能高管武石洋明在接受采访时称,采用纳米压印技术的佳能光刻设备FPA-1200NZ2C目标最快在今年开始交付,这一设备的交付将为小型半导体制造商生产先进芯片开辟了一条新的途径。

与此同时,3月5日美光科技公司在一场举办的演讲中表示,将率先支持佳能的纳米压印技术,从而进一步降低生产DRAM存储芯片的单层成本。

从存储芯片开始,纳米压印搅动芯片制造格局

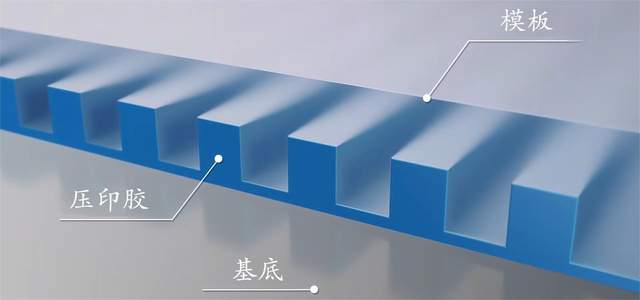

纳米压印,一种新型的微纳加工技术。纳米压印技术通过光刻胶辅助,将模板上的微纳结构转移到待加工材料上的技术,其最早在20世纪90年代中期由华裔科学家周郁发明。单从EUV光刻技术原理来看,想要实现更高的分辨率,无外乎从三个层面着手。一是选用更小波长的光源,二是通过界面材料提高数值孔径NA值,三是获取更低的工艺因子,其中主要的实现手段是缩短光源波长。

但是光学光刻是存在分辨率极限的,缩小波长的每一次实现都伴随技术难度和成本倍增,所以EUV光刻机不仅产能有限而且成本极其高昂。而纳米压印的加工过程不使用可见光或紫外光加工图案,而是使用机械手段进行图案转移,所以能实现的分辨率完全不会受到光学光刻最短曝光波长的物理限制,也不会像EUV需要如此高昂的成本。

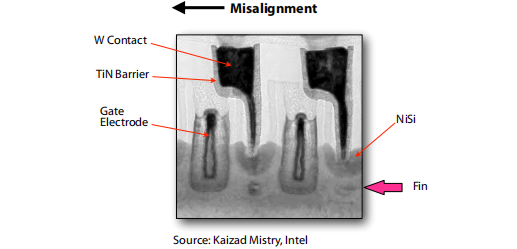

在美光科技公司近期的演讲中,也提到了DRAM节点和沉浸式光刻分辨率的问题,“Chop层数量不断增加,这就意味着添加更多的曝光步骤,来取出密集存储器阵列外围的dummy structures。”在光学系统下,受限于技术本身的限制,DRAM层图案已经很难用光刻技术来进行印刷。

“纳米打印方式可以用更精细的方式打印出来,且鉴于纳米压印技术应用成本是沉浸式光刻技术的五分之一,因此是非常不错的解决方案”,美光科技公司坦言。纳米压印分辨率只与模板图案的尺寸相关,已经能做到高于传统光刻的分辨率。

虽然生产速度上会慢上一些,但是用于压印的模板可以反复使用,大大降低了加工成本也方便进行量产。因此美光计划率先支持佳能的纳米压印技术,从而进一步降低生产DRAM存储芯片的单层成本。

存储芯片,的确是目前最契合纳米压印技术的。存储厂商在芯片制造上会更偏重对成本的把控,会放宽对缺陷的要求给予一定的设计余量,可以承受一定的缺陷只要不影响成品率就行。佳能规划的纳米压印设备路线图也是从3D NAND存储芯片开始,逐渐过渡到DRAM,最终实现CPU等逻辑芯片的制造。

凯侠与佳能在纳米压印上的合作也已有多年,SK海力士也从Canon引进纳米压印设备计划在2025年左右使用该设备开始量产3D NAND闪存。三星同样开发了包括纳米压印技术在内多种方案以解决多图案工艺导致的成本上升问题。

佳能社长御手洗富士夫也曾在去年表示,纳米压印光刻技术面世为半导体制造商生产先进芯片开辟了一条新的途径。

随着佳能光刻设备最快今年开始交付,存储芯片与纳米压印技术相结合,该技术能否降低存储厂商对芯片代工厂的依赖,能否在存储芯片的批量生产上大幅提高效率并降低成本,这一问题的答案最早在今年就能看到。

降低芯片制造成本,纳米压印给国产先进芯片发展带来新思路

此前佳能公布FPA-1200NZ2C纳米压印光刻半导体设备社长御手洗富士夫表示,纳米压印光刻半导体设备比ASML的EUV少1位数,而且这种机器所需功率只有EUV同类产品的十分之一。

从目前公布的进展看,FPA-1200NZ2C已经能够胜任5nm节点芯片的制造。此前还有佳能高管表示只需要不断改进掩模,FPA-1200NZ2C甚至能生产2nm芯片。

除了制程节点上的适配,据日经中文网报道,纳米压印能与极紫外光刻相比能将该工序的制造成本降低四成,耗电量降低九成。佳能此前公布的研究结果中,纳米压印光刻在吞吐量为80片时相对ArF光刻工艺可降低28%的成本,随着吞吐量增加成本降低幅度可达到50%以上。

虽然纳米压印技术不会也不可能完全取代EUV,但是它如果能成功应用,将打开芯片先进制程制造的新思路。

众所周知,目前我国半导体产业正受到多方围堵,国内半导体制造商获取先进半导体制造设备受到了不小的限制,尤其是在先进制程上。不例外的是佳能的纳米压印设备同样是限制出口的,日本的出口管制清单中就有“可实现45nm以下线宽的压印光刻装置”。

当前,纳米压印市场正在逐渐壮大,TechNavio数据显示,2026年纳米压印市场有望达到33亿美元,年复合增长率可达17.74%。已有不少国内厂商和科研机构在纳米压印赛道上布局,如青岛天仁微纳、苏州苏大维格、美迪凯、水晶光电、炬光科技、苏州光舵微纳、昇印光电、新维度微纳、歌尔股份等,助力国内半导体制造进一步突破。

在纳米压印市场打磨多年的天仁微纳已经在微纳光学市场占据了技术和市场领先地位,现在除了继续迭代纳米压印光刻在晶圆级光学加工领域的拓展,还在持续加码拓展纳米压印在半导体集成电路、平板显示、生物芯片等其他领域的应用,助力国产纳米压印设备打破进口垄断。

不久前炬光科技成功并购瑞士SMO,SMO拥有纳米压印精密微纳光学设计与加工制造技术,即结合微纳光学设计目标进行母版的设计与制造,在8英寸晶圆基板上进行精密压印,8英寸晶圆处于成熟量产阶段。

光舵微纳经过多年的研发及市场应用推广,已制造出多款研发型纳米压印设备及全自动量产型纳米压印设备,在LED图形化衬底产业实现了对尼康光刻机的产业化替代。目前也在积极拓展纳米压印技术在高端半导体领域的产业化应用。

如果纳米压印设备在实际量产中真的取得了如预期中的效果,这对国内纳米压印行业无疑将是一针强心剂,也将为国内先进芯片制造发展带来新的思路。

小结

随着半导体行业的快速发展,芯片越来越紧凑集成度越来越高,对芯片制造技术提出了越来越高的要求,行业渴求更低成本的制造技术。纳米压印能否如预期中掀起先进制程芯片制造的革命,不久之后就能在存储领域见分晓。

-

光刻技术

+关注

关注

1文章

151浏览量

16572

发布评论请先 登录

中国打造自己的EUV光刻胶标准!

台阶仪在集成电路制造中的应用:高端光刻胶材料纯化研究进展

纳米压印的光栅图形形貌3D测量-3D白光干涉仪应用

纳米压印光刻技术应用在即,能否掀起芯片制造革命?

纳米压印光刻技术应用在即,能否掀起芯片制造革命?

评论