概述

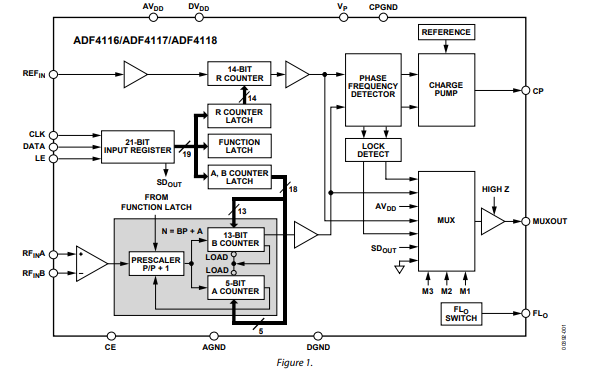

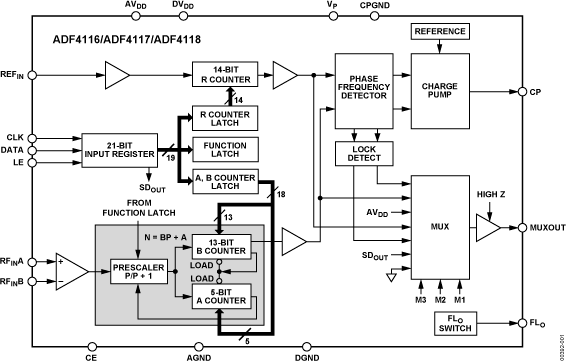

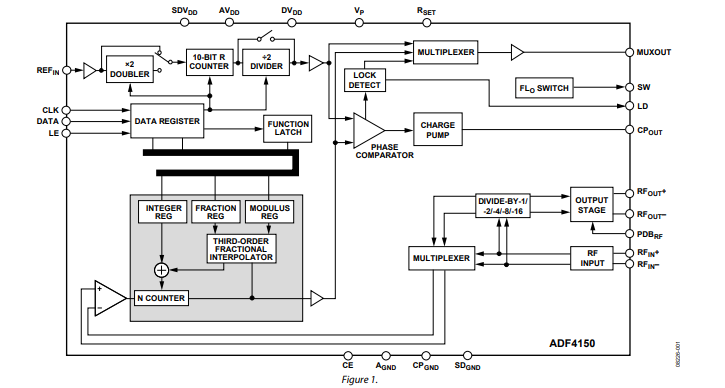

ADF4116/ADF4117/ADF4118均为频率合成器,可以用来在无线接收机和发射机的上变频和下变频部分实现本振。上述器件由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器、可编程A和B计数器以及双模预分频器(P/P+1)组成。A(5位)、B(13位)计数器与双模预分频器(P/P+1)配合,可实现N分频器(N = BP+A)。此外,14位参考分频器(R分频器)允许PFD输入端的REFIN 频率为可选值。如果频率合成器与外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(PLL)。

这些器件采用2.7 V (±10%)或5 V (±10%)电源供电,不用时可以关断。

数据表:*附件:ADF4116 ADF4117 ADF4118单通道、整数N分频550MHz PLL技术手册.pdf

特性

- ADF4116: 550 MHz

- ADF4117: 1.2 GHz

- ADF4118: 3.0 GHz

- +2.7 V至+5.5 V电源供电

- 双模预分频器

ADF4116: 8/9

ADF4117/ADF4118: 32/33 - 独立的电荷泵电源(V

P)可在3 V系统中提供扩展的调谐电压 - 三线式串行接口

- 数字锁定检测

- 省电模式

- 快速锁定模式

框图

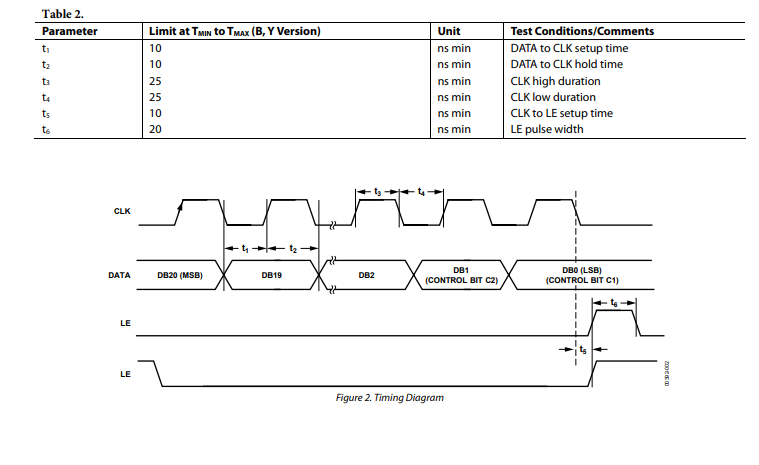

时序特征

引脚配置描述

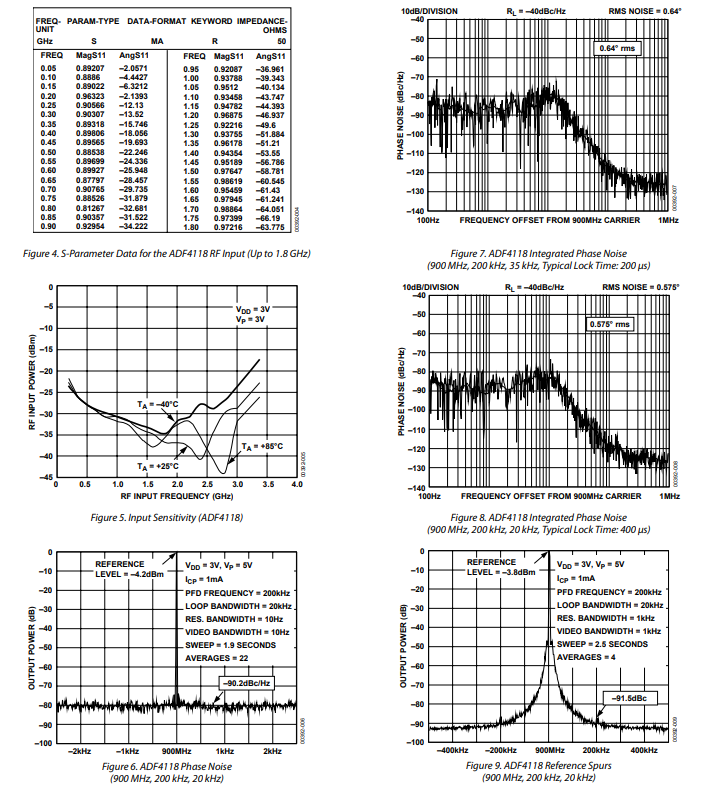

典型性能特征

电路说明

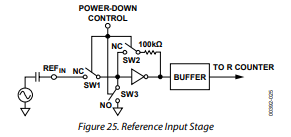

参考输入部分

参考输入级如图25所示。SW1和SW2通常为闭合开关,SW3通常断开。当启动掉电模式时,SW3闭合,SW1和SW2断开。这确保了在掉电时参考引脚((REF_{IN}))不会有负载。

射频输入部分

射频输入级如图26所示。其后接一个两级限幅放大器,以生成预分频器所需的电流模式逻辑(CML)时钟电平。

预分频器(P/P + 1)

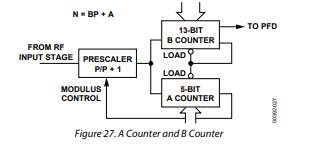

双模数预分频器(P/P + 1)与A计数器和B计数器配合,可实现较大的分频比N((N = PB + A) )。双模数预分频器以CML电平工作,它从射频输入级获取CML时钟信号,并将其分频到适合CMOS A计数器和B计数器处理的频率。预分频器是可编程的,对于ADF4116,可在软件中设置为8/9;对于ADF4117和ADF4118,可设置为32/33 。它基于同步4/5核心。

A计数器和B计数器

A CMOS计数器和B CMOS计数器与双模数预分频器配合,可在锁相环(PLL)反馈回路中实现较宽范围的分频比。当预分频器的输出为200 MHz或更低时,这些计数器可正常工作。

脉冲吞咽功能

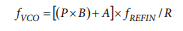

A计数器和B计数器与双模数预分频器配合,能够生成间隔仅为参考频率除以R的输出频率。压控振荡器(VCO)频率的计算公式为:

其中:

- (f_{VCO})是外部压控振荡器(VCO)的输出频率。

- (P)是双模数预分频器的模数。

- (B)是13位二进制计数器的预设分频比(3到8191)。

- (A)是6位吞咽计数器的预设分频比(0到31)。

- (f_{REFIN})是外部参考频率振荡器的频率。

- (R)是14位二进制可编程参考计数器的预设分频比(1到16,383)。

R计数器

14位R计数器可对输入参考频率进行分频,以产生送往鉴频鉴相器(PFD)的参考时钟。允许的分频比范围是1到16,383 。

-

频率合成器

+关注

关注

5文章

368浏览量

33880 -

pll

+关注

关注

6文章

990浏览量

138378 -

变频

+关注

关注

2文章

471浏览量

35380

发布评论请先 登录

ADF4118无法锁定

ADF4116/ADF4117/ADF4118,pdf da

ADF4118 单通道、整数N分频3.0 GHz PLL

ADF4116 单通道、整数N分频550 MHz PLL

ADF4117 单通道、整数N分频1.2 GHz PLL

ADF4216/ADF4217/ADF4218:双射频PLL频率合成器550 MHz/1.2/2.0/2.5 GHz数据表

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

ADF4116/ADF4117/ADF4118单通道、整数N分频550MHz PLL技术手册

评论