LMX2487器件是一款低功耗、高性能的 Delta-Sigma 小数 N 分频 PLL,具有 辅助整数-N PLL。它是使用 TI 的先进工艺制造的。

*附件:lmx2487.pdf

通过 delta-sigma 架构,在较低失调频率下推动分数杂散 到环路带宽之外的更高频率。能够接近杂散噪声和相位噪声 能量到更高频率是调制器阶数的直接函数。与模拟不同 补偿,LMX2487中使用的数字反馈技术对变化具有很强的抵抗力 晶圆加工中的温度和变化。LMX2487 Delta-Σ 调制器是可编程的 高达四阶,允许设计人员选择最佳调制器阶数以适应 系统的相位噪声、杂散和锁定时间要求。

用于对LMX2487进行编程的串行数据通过三线高速传输 (20 兆赫)MICROWIRE接口。该LMX2487提供高频率分辨率、低杂散、快速 编程速度,以及更改频率的单字写入。这使其成为直接 数字调制应用,其中 N 计数器直接用信息进行调制。这 LMX2487采用 24 引脚 4.0 × 4.0 × 0.8 mm WQFN 封装。

特性

- 四重模量预分频器,用于降低分频

- 射频 PLL:16/17/20/21 或 32/33/36/37

- IF PLL:8/9 或 16/17

- 高级 Delta Sigma 分数补偿

- 12 位或 22 位可选分数模量

- 高达4阶可编程Δ-Σ

调制器

- 改进的锁定时间

- 快速锁定/周期滑移减少,单

字写入以改变频率 - 集成超时计数器

- 快速锁定/周期滑移减少,单

- 工作范围广

- LMX2487 RF PLL:1.0 GHz 至 6.0 GHz

- 有用的功能

- 数字锁检测输出

- 硬件和软件断电控制

- 片内输入倍频器

- 高达 50 MHz 的射频相位比较检测器

- 2.5V 至 3.6V 工作电压,带 I

CC= 8.5 毫安

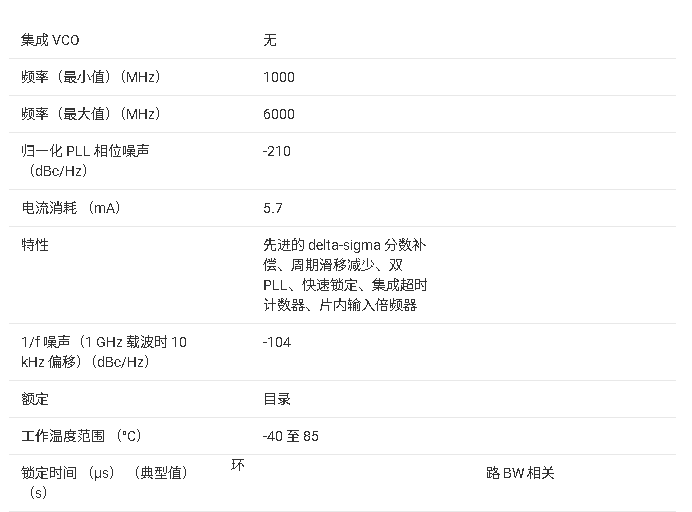

参数

方框图

1. 产品概述

LMX2487是德州仪器(TI)推出的高性能低功耗双锁相环频率合成器,集成Δ-Σ分数分频(RF PLL)和整数分频(IF PLL)功能,工作频率覆盖1 GHz至6 GHz(RF PLL)及250 MHz至3 GHz(IF PLL)。采用24引脚WQFN封装(4.0×4.0 mm),适用于蜂窝基站、卫星调谐器等高频应用。

2. 核心特性

- RF PLL

- 支持16/17/20/21或32/33/36/37分频比的可编程预分频器。

- 12/22位可选分数模数,最高4阶Δ-Σ调制器,降低近端杂散。

- 快速锁定技术(Fastlock)和周期滑移抑制(CSR)。

- IF PLL

- 8/9或16/17预分频器,整数分频架构。

- 通用功能

- 三线高速MICROWIRE接口(20 MHz),支持单次写入频率切换。

- 数字锁定检测、硬件/软件断电控制。

- 宽电压范围(2.5 V至3.6 V),典型功耗8.5 mA。

3. 电气参数

- RF PLL:电荷泵电流可编程(0至15级,最高1.52 mA),相位噪声优化至-210 dBc/Hz(归一化)。

- IF PLL:固定电荷泵电流(3.5 mA),输入灵敏度低至-30 dBm。

- 温度范围:-40°C至85°C,ESD防护达2 kV(HBM)。

4. 应用设计

- 匹配网络:FinRF/FinIF需通过电阻衰减和隔直电容连接,阻抗实部16-508 Ω(随频率变化)。

- 环路滤波器:建议阶数比Δ-Σ调制器高一阶,以抑制高频噪声。

- 参考输入:OSCin支持5-110 MHz,内置2倍频选项。

5. 封装与文档

-

锁相环

+关注

关注

36文章

633浏览量

90801 -

频率合成器

+关注

关注

5文章

305浏览量

33410 -

可编程

+关注

关注

2文章

1307浏览量

41318 -

pll

+关注

关注

6文章

976浏览量

137567

发布评论请先 登录

一种基于ADF4106的锁相环频率合成器应用实例介绍

基于ADF4106的锁相环频率合成器

快速了解Pasternack推出的高性能USB控制锁相环频率合成器

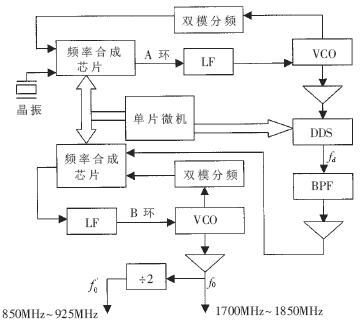

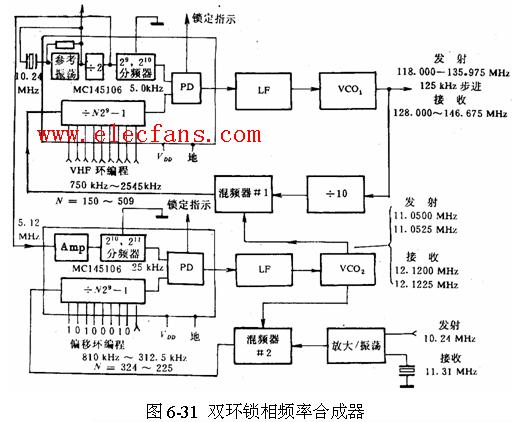

基于DDS和双锁相环频率合成器实现双环数字调谐系统的设计

LMX2487 高频双锁相环频率合成器技术文档总结

LMX2487 高频双锁相环频率合成器技术文档总结

评论