高性能低噪声锁相环LTC6948:设计与应用全解析

在电子工程师的日常工作中,高性能的锁相环(PLL)器件是实现精确频率控制和低噪声信号合成的关键。今天,我们就来深入探讨一款名为LTC6948的高性能、低噪声的6.39GHz锁相环,看看它究竟有何独特之处,以及在实际设计中如何发挥其优势。

文件下载:LTC6948.pdf

一、LTC6948概述

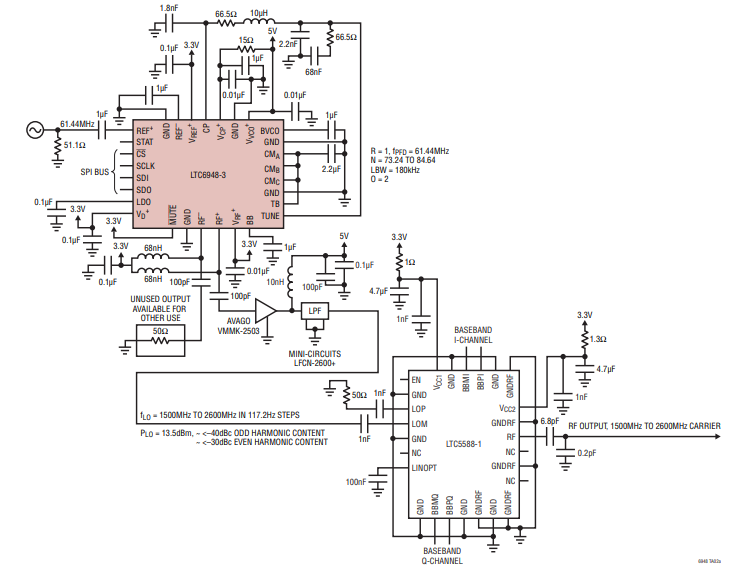

LTC6948是一款集成了VCO的高性能低噪声锁相环,它内部包含参考分频器、相位频率检测器(PFD)、超低噪声电荷泵、分数反馈分频器和VCO输出分频器等关键组件。其分数分频器采用了先进的四阶Δ∑调制器,可提供极低的杂散电平,从而允许使用较宽的环路带宽,产生极低的积分相位噪声值。而且,可编程的VCO输出分频器范围为1到6,进一步扩展了输出频率范围。

二、特性亮点

(一)超低噪声性能

LTC6948具有出色的噪声特性,归一化带内相位噪声地板低至 -226 dBc/Hz,归一化带内1/f噪声为 -274 dBc/Hz,宽带输出相位噪声地板为 -157 dBc/Hz。这种超低噪声性能使得它在对噪声敏感的应用中表现出色,例如无线基站、微波数据链路等。

(二)灵活的输出频率选项

LTC6948有四种不同的输出频率范围可供选择,分别为LTC6948 - 1(2.240 to 3.740GHz)、LTC6948 - 2(3.080 to 4.910GHz)、LTC6948 - 3(3.840 to 5.790GHz)和LTC6948 - 4(4.200 to 6.390GHz)。并且通过输出分频器(O_DIV)的设置(范围为1到6),可以进一步调整输出频率,满足不同应用的需求。

(三)快速频率切换

在一些需要快速改变输出频率的应用中,LTC6948能够实现快速频率切换,提高系统的响应速度。

(四)软件设计工具支持

它还支持FracNWizard™软件设计工具,方便工程师进行设计和调试,减少开发时间和成本。

三、电气特性分析

(一)参考输入

参考输入(REF+,REF -)具有较宽的输入频率范围(10 to 425MHz),输入信号电平单端时为0.5 to 2.7VP - P,输入阻抗较高,差分输入电阻为5.8 to 11.6kΩ,输入电容为14pF。同时,通过设置FILT[1:0]和BST位,可以优化参考输入的性能。

(二)VCO

VCO的频率范围根据不同型号有所不同,如LTC6948 - 1为2.24 to 3.74GHz。其调谐灵敏度也在一定范围内变化,例如LTC6948 - 1的调谐灵敏度为4.7 to 7.2 %Hz/V。

(三)RF输出

RF输出(RF+,RF -)的频率范围为0.373 to 6.39GHz,输出分频器范围为1到6,输出占空比为50%。输出功率可根据不同的设置进行调整,最大可达0.1dBm,并且具有快速的静音使能和禁用时间。

(四)电荷泵

电荷泵的输出电流范围为1到11.2mA,有8种设置选项。其输出电流源/吸收精度高,在不同设置下的误差在±2%到±6%之间,同时输出电流与输出电压和温度的灵敏度较低。

四、引脚配置与功能

LTC6948采用28引脚(4mm × 5mm)塑料QFN封装,每个引脚都有其特定的功能:

- 参考输入引脚(REF+,REF -):用于输入参考频率信号,需AC耦合1µF电容。

- 状态输出引脚(STAT):可通过状态寄存器配置为多种状态位的逻辑或输出。

- 串行端口相关引脚(CS,SCLK,SDI,SDO):用于实现串行通信,方便对器件进行配置和控制。

- 电源引脚(VREF +,VD +,VRF +,VVCO +,VCP +):提供不同部分的电源,需要旁路相应电容以保证电源稳定性。

- RF输出引脚(RF+,RF -):输出VCO分频后的信号,可单端或差分使用。

- 其他引脚:如TUNE用于VCO调谐输入,CP为电荷泵输出等,它们在电路中都起着关键作用。

五、实际应用与注意事项

(一)应用领域

LTC6948广泛应用于无线基站(如LTE、WiMAX、W - CDMA、PCS)、微波数据链路、军事和安全无线电以及测试和测量等领域。

(二)注意事项

- 在使用过程中,要注意各个电源引脚的电压范围和旁路电容的选择,确保电源的稳定性。

- 对于参考输入信号,要根据实际情况合理设置FILT[1:0]和BST位,以达到最佳的噪声性能。

- 在进行PCB布局时,要注意引脚的接地处理,尤其是暴露焊盘(PIN 29)必须焊接到PCB上,且要通过多个过孔连接到地平面,以降低接地电感和热阻。

六、总结与展望

总的来说,LTC6948以其超低噪声、灵活的频率选项和丰富的功能特性,成为了电子工程师在设计高性能锁相环电路时的理想选择。在未来的电子系统设计中,随着对信号质量和频率控制要求的不断提高,像LTC6948这样的高性能器件必将发挥更加重要的作用。

各位工程师在实际应用中,是否遇到过类似器件的调试难题?你们又是如何解决的呢?欢迎在评论区分享你们的经验和见解。

-

锁相环

+关注

关注

36文章

636浏览量

91288 -

低噪声

+关注

关注

0文章

510浏览量

24684 -

LTC6948

+关注

关注

0文章

11浏览量

1205

发布评论请先 登录

深入剖析LTC1748:高性能14位、80Msps低噪声ADC

LTC1742:高性能14位、65Msps低噪声ADC的深度解析

Altera公司锁相环IP核介绍

探索CDC516:高性能3.3V锁相环时钟驱动器

CDC2516:高性能锁相环时钟驱动器的深度解析

CDC509:高性能3.3V锁相环时钟驱动器

CDCVF25081:高性能锁相环时钟驱动器深度解析

TLC2932A高性能锁相环芯片详解:设计与应用指南

探索TLC2933A高性能锁相环:特性、应用与设计要点

TI CDCU877和CDCU877A:高性能1.8V锁相环时钟驱动器深度解析

高性能低噪声四运放OP470:特性、测量及应用全解析

深入解析LTC6404:高性能全差分输入/输出放大器的卓越之选

高性能LTC6406:3GHz低噪声差分放大器深度剖析

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册

LTC6948具集成型VCO的超低噪声0.37GHz至6.39GHz分数N合成器技术手册

高性能低噪声锁相环LTC6948:设计与应用全解析

高性能低噪声锁相环LTC6948:设计与应用全解析

评论