(一)单bit信号同步器

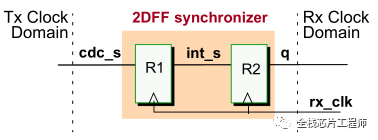

最经典的2DFF 1-bit同步器如下,下图结构通常用于单bit控制信号的异步处理:

绝大数情况下,当第一个寄存器R1进入亚稳态后,在第二级寄存器R2采样R1的输出前,R1的输出已经能稳定在0或1。

注意:

cdc_s信号必须做到glitch free,也就是我们通常说的寄存输出;

int_s信号链路禁止组合逻辑,其本质也是杜绝glitch的出现。

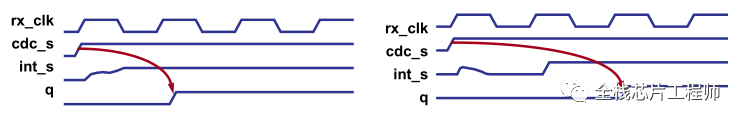

偏执狂的IC designer肯定会问,第一级寄存器R1的行为到底是啥样子的?由于cdc_s信号是Tx clock Domain,而R1寄存器的采用时钟是Rx clock Domain,当Rx clock采样时,若cdc_s正好跳变(不满足setup/hold),那么就会出现如下两种情况,而前仿真是无法仿真出下图2种行为的(具体见芯片设计之CDC异步电路(一)一文)。

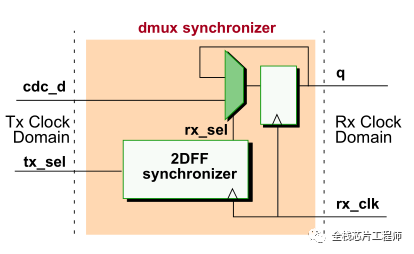

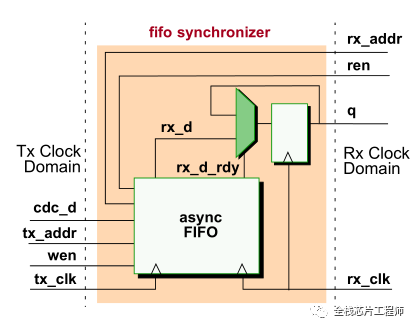

(二)DMUX同步器 两级寄存器(先进工艺要求三级)的同步器通常用于控制信号的异步处理,但是data bus的异步处理呢?我们可以采用DMUX结构。

注意:

tx_sel、rx_sel有效时,cdc_d数据总线必须保持稳定;

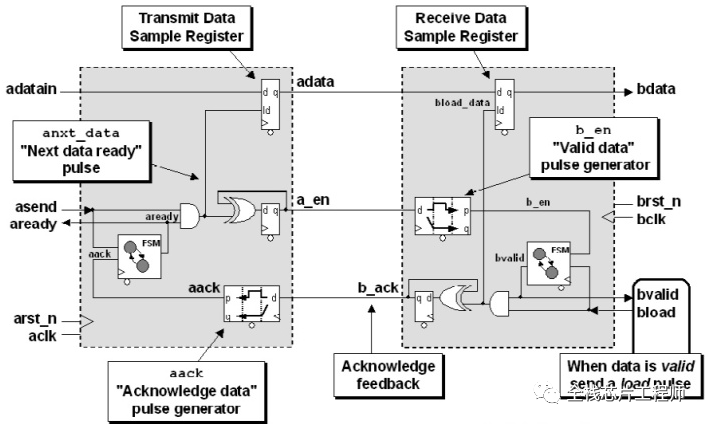

(三)握手处理

源时钟域先将数据发送到总线上,并给出一个valid信号,而目标时钟域同步valid信号后,若valid信号为高电平则采样总线数据,并返回一个ready信号给源时钟域。源时钟域再次同步该ready信号,若ready信号为高,则代表一次握手成功,数据传输完毕,开始进行下一次数据传输。

采用握手机制可以保证异步multi-bit数据传输不出现错误,但由于需要等待握手的完成再传输数据,因此传输效率较低。

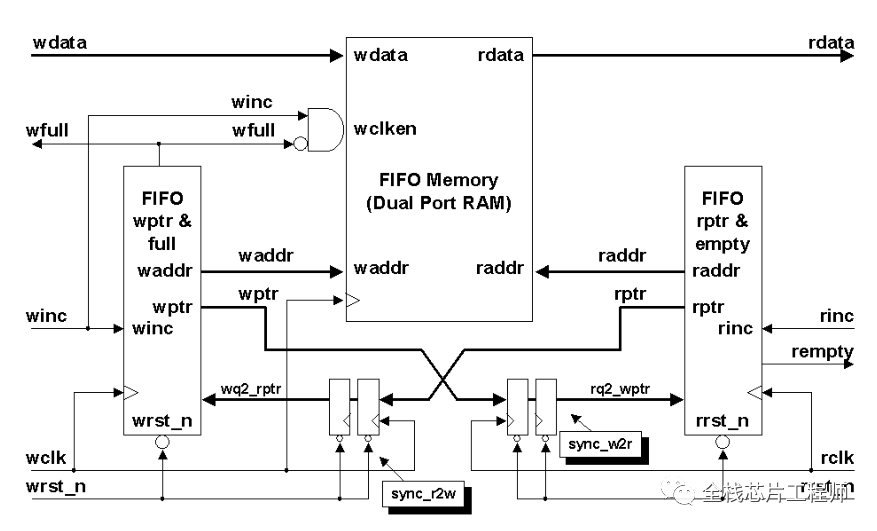

(四)异步FIFO

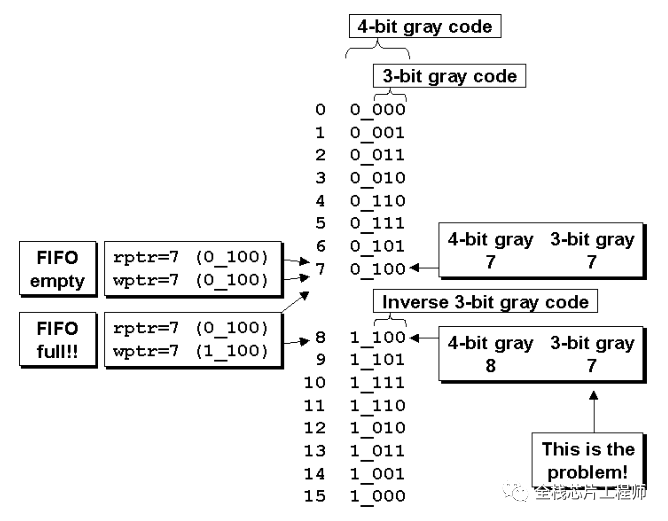

老生常谈的异步FIFO,其本质是采用格雷码,在地址连续的情况下,其对应格雷码每个周期只变化1bit,因此可以直接异步采样。

注意:

FIFO的overflow、underflow问题;

tx_addr是连续的,即地址hamming distance是1;

FIFO深度须2^n;

经典的FIFO结构如下:

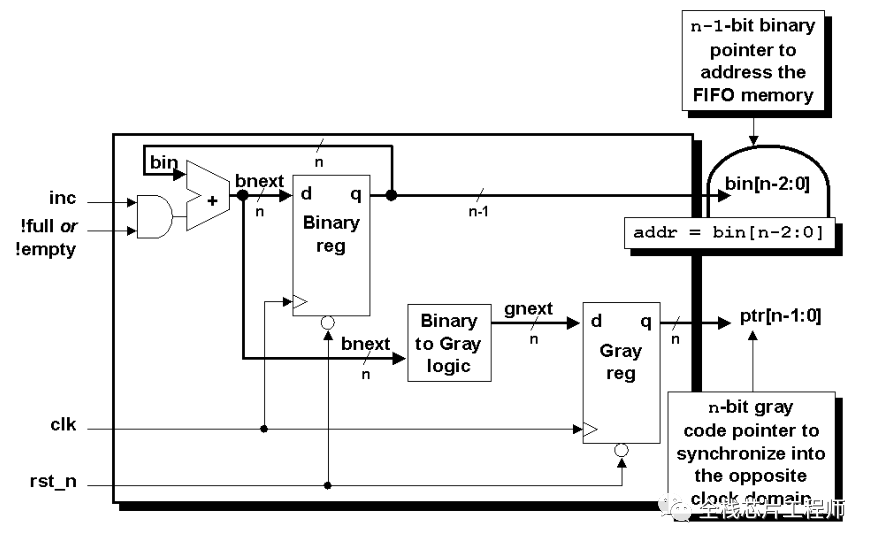

核心电路:是将FIFO读写地址指针的二进制码转成格雷码,方便同步器打两拍传递到对向时钟域去做空满判断。

空满判断:为了区别空满,我们增加1bit的地址(MSB),我习惯直接用Gray码比较读写指针判定空满:

当Gray码读写指针完全相等时,FIFO空;

当Gray码读写指针最高2bit相反,其余bit相同时,FIFO满; 通常二进制码比较空满是:最高bit不同,其余bit相同,则FIFO满,而格雷码则不同哈。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5619浏览量

130398 -

CDC

+关注

关注

0文章

58浏览量

18594 -

同步器

+关注

关注

1文章

117浏览量

15698 -

FIFO存储

+关注

关注

0文章

103浏览量

6344 -

异步处理

+关注

关注

0文章

7浏览量

6661

原文标题:芯片跨时钟域设计(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

两级DFF同步器跨时钟域处理简析

如何利用FPGA设计一个跨时钟域的同步策略?

芯片跨时钟域设计案例简析(一)

芯片跨时钟域设计案例简析(一)

评论