一、产品简述

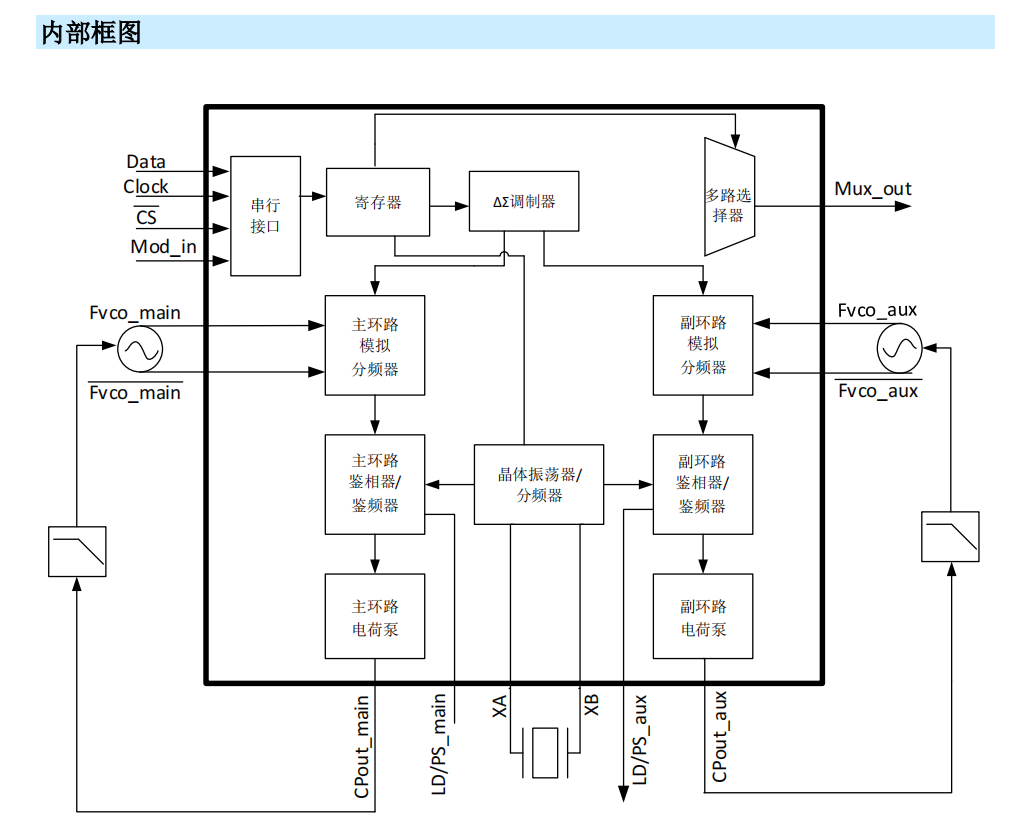

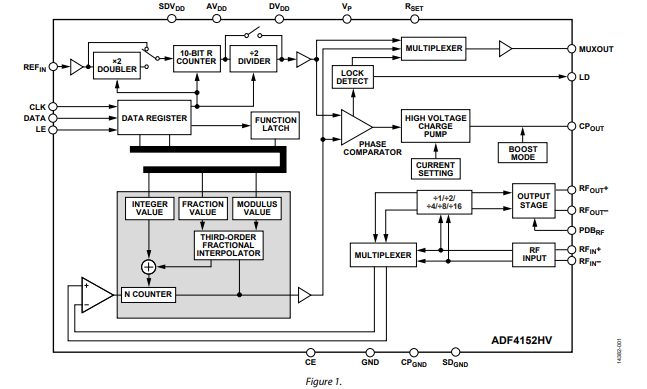

MS72300 是一款双环路、小数 N 分频频率综合器。包含主环路和副环路锁相环。它提供了极高的频率分辨率、快的输出频率切换速度和低相位噪声性能。芯片须使用外部压控振荡器,主环路最大工作频率 2.1GHz,适合应用于无线通信系统中。副环路适合于低于 500MHz以下的频率应用。MS72300 采用三线高速串行接口,结合芯片大的环路带宽、高的频率分辨率,三线接口允许直接对主环路 VCO 进行频率调制。这支持任何相位连续、恒定包络的调制方案。

二、主要特点

无杂散工作

最大工作频率:主环路 2.1GHz,副环路 0.5GHz

高频率分辨率:低于 100Hz

高的内部参考频率实现了大的环路带宽

快速的输出频率切换:小于 100μs

主环路滤波器带宽内相位噪声-91dBc/Hz@1800MHz

软件可编程掉电模式

高速串行接口:100Mbps

三线编程

可编程参考频率分频比

增益可编程的鉴相器提供了可编程的环路带宽

频率动力操控进一步缩短捕获时间

片上晶体振荡器

温度补偿频率校准

3V 工作

5V 输出到环路滤波器

三、应用

t替代兼容SKY72300,适用于对讲机

通用 RF 系统

2.5G/3G 无线架构

宽带无线访问

低比特率无线遥测

L 波段接收机

卫星通信

r瑞 盟 代 理 1 5 9 2 6 4 8 1 7 1 0

深圳市三亚微科技有限公司——瑞盟代理商

主要产品:运算放大器、ADC/DAC、马达驱动(直流,步进,BLDC)霍尔电路、MBUS仪表总线、HBUS、485/422/232接口,LVDS

驱动器/接收器,串化/解串,TDC,NFC,射频电路,时钟发生器,射频功率检测,MCU,开关电路,电平转换,基准,电池管理芯片等。

审核编辑:汤梓红

-

振荡器

+关注

关注

28文章

4155浏览量

142324 -

pll

+关注

关注

6文章

976浏览量

137589

发布评论请先 登录

无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器 skyworksinc

ADF4158直接调制/波形产生6.1GHz小数N分频频率合成器技术手册

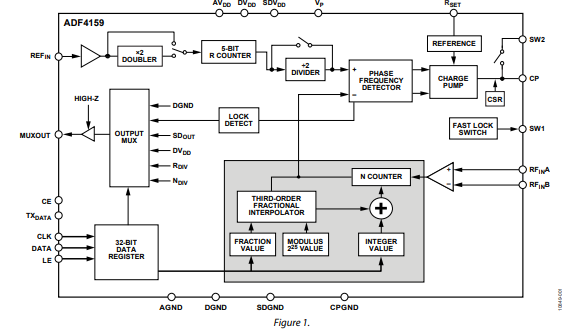

ADF4159直接调制/快速波形产生13GHz小数N分频频率合成器技术手册

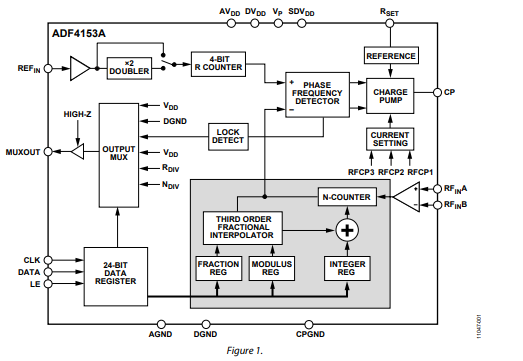

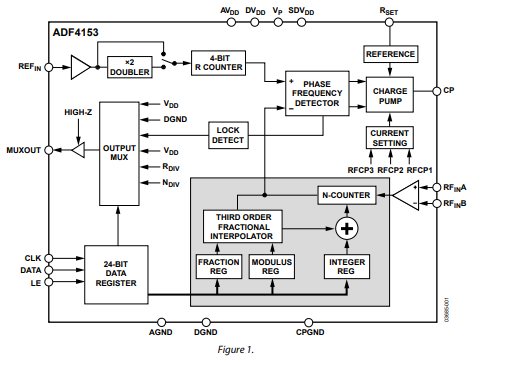

ADF4153A小数N分频频率合成器技术手册

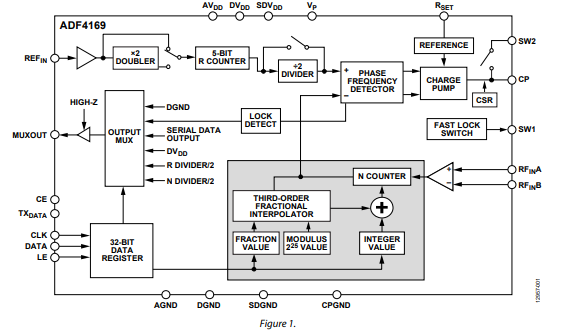

ADF4169直接调制/快速波形产生13.5 GHz小数N分频频率合成器技术手册

无杂散、2.1GHz、双环路小数N分频频率综合器MS72300

无杂散、2.1GHz、双环路小数N分频频率综合器MS72300

评论