| 做芯片流片前的“最后一米”

6月17日-18日,芯谋研究承办以“南沙芯声 聚势未来”为主题的2023中国·南沙国际集成电路产业论坛在广州南沙盛大召开。秉承高端、全产业链、国际化的特色,本次峰会吸引了来自半导体产业的500多位嘉宾齐聚一堂,共襄盛会。

广东省委常委、副省长王曦,广东省政府副秘书长许典辉,广州市委常委、南沙区委书记卢一先,广州市委常委、常务副市长陈勇等政府领导;中国科学院院士许宁生,国家重大专项02专项总师、中国集成电路创新联盟秘书长叶甜春,清华大学教授魏少军,复旦大学微电子学院院长张卫等学术专家;恩智浦半导体大中华区主席李廷伟,高通公司中国区董事长孟樸,博世(中国)投资有限公司执行副总裁徐大全,东电电子中国区总裁陈捷,西门子EDA 全球资深副总裁、亚太区总裁彭启煌,泛林集团副总裁兼中国区总裁汪挺等国际企业代表;中芯国际董事长高永岗,广发证券党委书记葛长伟,华为科学家咨询委员会主任徐文伟,浙江吉利控股集团CEO李东辉,华润微电子总裁李虹,芯原股份创始人、董事长兼总裁戴伟民,国家智能传感器创新中心董事长杨潇,广东省集成电路行业协会会长陈卫等国内企业代表出席了本次活动。

国微芯执行总裁兼CTO白耿在会上以《助力先进工艺芯片设计安全》为主题发表主题演讲。

EDA(电子设计自动化)是贯穿芯片设计、制造、封装整条产业链环节的一系列工业软件的总称,其行业特点是“小而精”,全球市场规模约115亿美元,倘若不计入IP销售,EDA工具或许仅有70、80亿美元的市场空间,但这样小的市场却托起了千亿规模的集成电路行业,以至于影响上万亿规模的电子系统产业。

国内将近85%的市场份额由新思科技(Synopsys)、楷登电子(Cadence)和西门子EDA(Mentor Graphics)三大EDA公司所占据,其中西门子EDA在国内影响尤为深厚,反观国产EDA则只占约11%,因此国产EDA产业有巨大成长空间。纵览过去几年,国产EDA呈现良好成长态势,每年约有10%复合增长率,西门子EDA的增速则超过12%。

国际巨头为何拥有如此强大的统治力?首先,历史上EDA三巨头拥有超过240次并购,使得三大公司都具有提供全流程的EDA解决方案的能力,除了EDA工具外,三大公司也提供IP设计、设计服务以及一体化解决方案。以新思科技2020年收入来看,57%集中在EDA销售,1/3的收入来自于IP设计。

其次,三大公司在EDA上每年的投入都超过10亿美金,加起来每年超过30亿美金,国内EDA企业与之相比,投入资金水平远远低于三大公司。

在政府重视和市场资本的追捧之下,国内目前已有大量EDA公司,但总的来说,以做点工具开发为主,且多数为设计前端点工具,缺乏与工艺厂关联度更高、复杂度更高的设计后端及制造端的工具。

DFT工具:为车规芯片保驾护航

近年来,车规芯片兴起带动行业对DFT(可测试性设计)的重视,但反过来,车规芯片拥有更为严苛的标准,比如,安全性认证ISO26262、质量管理体系ISO/TS16949、AEC-Q100等,这些都为DFT工具提出了一系列要求。

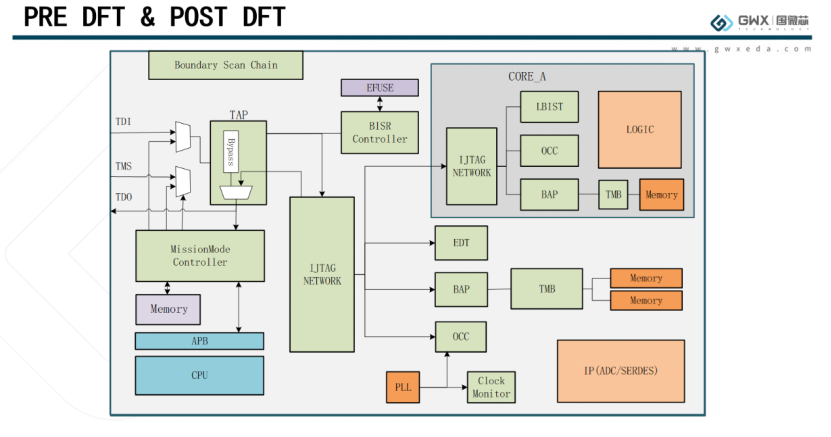

对车规芯片来说,必须用DFT工具并加入BIST模块,例如在逻辑单元加入LBIST模块、内存单元加入MBIST模块。对于生产过程中可能产生的缺陷,要具备筛查,诊断和溯源能力,包括支持Stuck-at或Transition 等缺陷诊断以及插入MBIST/LBIST/BSCAN/IP Test等DFT功能模块。此外,为在使用环境中动态检测芯片,还需要在DFT设计模块中加入控制模块。

举例来说,芯片设计中,刚开始输入的都是芯片功能模块,只有当加入了DFT相关模块设计,从底层到顶层都加入DFT设计模块和控制模块,才称得上完整的芯片设计。

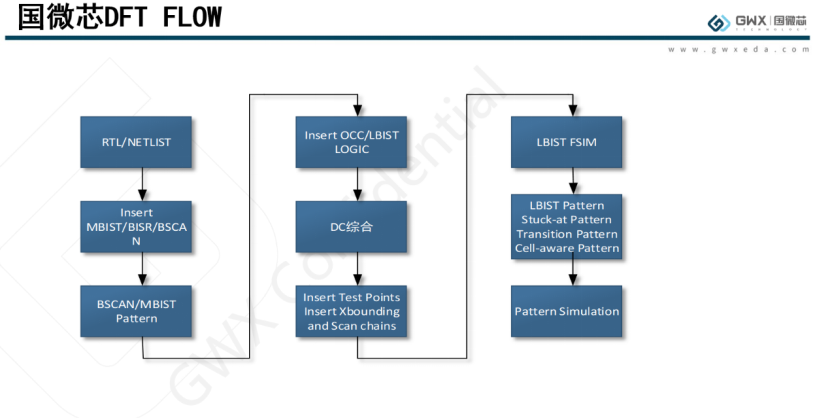

在国微芯DFT设计流程中,针对用户提供的RTL,可以自动给芯片加入MBIST/BISR/BSCAN功能模块,产生BSCAN/MBIST所需测试向量,加入DFT相关测试模块、功能模块、LBIST并进行DC综合,加入可测试的点,加入扫描链,之后对LBIST进行故障仿真,用自动测试向量的工具产生芯片测试所需向量,最后进行向量仿真。

制造车规芯片时,需要经历封装前的探针测试和封装后的机台测试,筛选早期出现问题的芯片,再对合格的芯片进行不同温度的测试,整个测试流程非常严格。

制造车规芯片后,也需经历一系列测试,以满足AEC-Q100的标准规范,包括模拟芯片使用环境的测试(压力、温度、化学环境等)、模拟芯片使用生命周期的测试(车规芯片要求周期较长,一般为10年~15年)、芯片可靠性电迁移测试、HCI和BTI等可靠性测试。

DFT测试的目的就是针对芯片使用过程中不同频率、不同电压,验证出芯片应用条件的边界,利用探明的边界条件,对芯片筛查,控制发货质量。与此同时,DFT积累的测试数据可为将来流片成品率提升提供建议和参考。

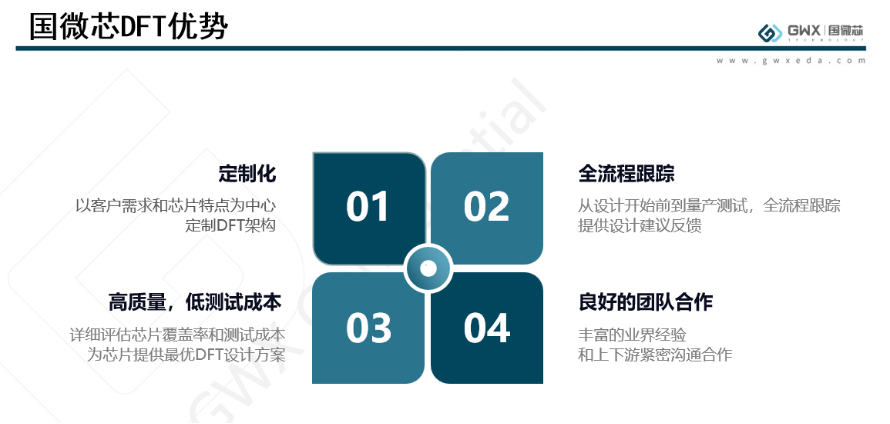

国微芯在DFT上的优势是可为用户提供定制化需求的DFT设计,从设计开始到流片后的测试都能为客户提供一系列反馈和建议,除此之外还可定制提高测试覆盖率和有效降低测试成本的DFT方案。目前国微芯的DFT设计已与国内很多高端芯片设计厂家合作,包括CPU、FPGA、DSP等各种芯片。

DFR:芯片“不老”的药

芯片也会变老,当芯片使用过程中,MOS管的阈值电压和饱和电流会出现漂移,导致晶体管变慢,进一步引起标准逻辑单元门变慢,从而导致整个芯片变慢,久而久之芯片还会失效。

DFR(可靠性工具)就是为了解决这种问题而生,在设计时能够预测芯片使用过程中可能产生衰退及失效的现象,并对这种现象预测仿真,针对性地找到老化发生点进行相应优化。晶体层面来看,DFR就是晶体管的SPICE仿真器,这种仿真器必须支持老化模型。

仅仅在晶体管级做完衰退分析还不够,为了能在芯片级考虑到衰退效应,进行Aging-Aware时序分析,必须要在特征化工具上提供解决方案。

EsseSim是国微芯自主研发的新一代电路仿真工具,是高性能、大容量并基于并行的SPICE仿真工具,可以为STA、EMIR等工具提供晶体管级数据支撑。此外,国微芯的特征化工具可以提取包含衰退效应的标准逻辑单元门时序库,支持Aging-Aware的时序分析。

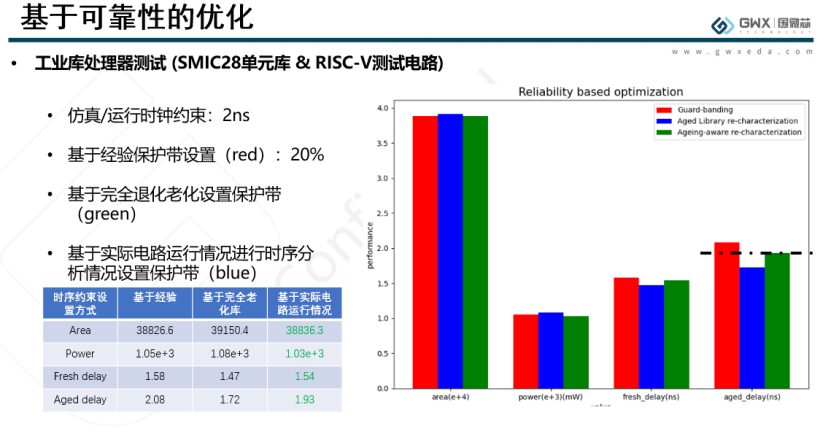

传统方法中,可靠性预估是基于经验对所有延迟设置20%的保护带(20% clk),使用这种完全凭经验值的方法进行可靠性Aging-Aware时序分析,会出现太乐观或太悲观的结果,要么没法保证在实际的工作年限正常运行,要么可能造成面积和功耗资源浪费。

另一个方法是假设电路中所有节点的电压受应几率(SP)都是固定的值,使用保守的退化老化库对电路进行时序分析,但这也不能保证时序分析考虑可靠性衰退的精准度,相对电路实际运行情况可能过于悲观,会造成芯片面积和功耗资源浪费。

国微芯实际采用的方法是基于电路实际运行情况,根据每个节点实际的受应几率,计算时序分析中关键路径延迟的衰退。从实际电路运行情况来看,最终考虑到衰退的最长关键路径非常接近设计实际时序约束,证明了我们芯片级可靠性设计方法的实用性和先进性。

国微芯:着重于后端和制造端EDA工具的开发

国微芯是由国微集团的EDA基础上发展而来。自2018年起,国微集团便承接科技部重大专项及各级政府若干重大专项项目,2022年10月国微芯从国微集团剥离出来独立运营。

迄今为止,国微芯前期资金投入已达近20亿元人民币,研发团队规模已超过300人,其中30人是由国外引进的高端EDA领军人才,研发团队硕博人员比例超75%,申请专利和软著共计超过150项。此外,公司已与西电、华科、南科大、东南大学、广工大建立5所校级EDA研究院,联合培养国家内部高校EDA后备人才。

根据国微芯执行总裁兼首席技术官白耿博士介绍,国微芯着重于后端和制造端的EDA工具开发,同时提供后端设计服务、DFT设计服务、IP设计业务,国微芯将它们叫做芯片流片前的“最后一米”,同时布局以开发数字全流程EDA工具链为目标。

国微芯有两大事业板块:“国微福芯”负责国产EDA工具开发工作,开发工具大类包括物理验证、形式验证、OPC(光学临近校正)、DFT(可测试性设计)、DFR(可靠性工具),“国微芯芯”注重后端设计、DFT设计服务以及IP设计。

国微芯EDA工具软件构架设计直接针对先进工艺、高端芯片设计面临的痛点,采用最先进的设计思路,主要包括三个关键点。

首先,是共性技术开发。物理验证工具和OPC工具都拥有共享统一的数据底座,在读取版图、解析版图数据时有高速运行读取的能力,同时可以形成自己smDB版图格式的文件,之后通过读取自己版图格式,比读取GDS/OASIS的速度可以提高上百倍,可以大大提升流片前物理证验及OPC效率。

其次,是在不同EDA工具中复用源代码级别底层功能模块。我们对这样一些功能模块在源代码级别进行定义,形成了通用服务引擎的概念,在开发不同EDA工具时进行源代码级别的复用,使开发EDA工具的速度、效率大大提升,同时在后期维护工具的时候所要投入的研发量也可以大大减少。

最后,是针对先进工艺、复杂工艺、先进SoC芯片设计规模版图越来越大,加快物理验证或加快OPC速度。如何充分利用大量CPU并行运算环境建立工具的软件架构,适合大规模CPU运算环境下并行加速。国微芯的物理验证和OPC工具可在5000甚至上万核的环境里进行验证工作,且拥有较好的加速性能。

2022年底国微芯已推出五大系列平台14款工具,2023年商用级工具又增加了DFT的ATPG、MBIST等多款工具,今年产业化的产品有17款之多。另外还有17款在研的工具,预计2024、2025年推出,至2025年国微芯总体工具量可达34款左右。

-

eda

+关注

关注

72文章

3061浏览量

181546 -

功能模块

+关注

关注

0文章

19浏览量

2930 -

车规芯片

+关注

关注

0文章

239浏览量

8001

原文标题:国微芯执行总裁兼CTO白耿:国产EDA设计后端及制造端参与者寥寥无几

文章出处:【微信号:icwise,微信公众号:芯谋研究】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

润芯微科技亮相2025荣耀全球开发者大会

ADI电源产品副总裁兼院士Robert Reay:ADI Power Studio工具突破电源系统设计效率

全球氮化镓巨头纳微半导体更换CEO

苏州市汽车电子及零部件产业商会到访润芯微科技

智算芯生 · 迭代无界 | 国微芯五款产品焕新发布,破“芯”局

紫光国芯亮相瑞芯微第九届开发者大会

2025 RISC-V中国峰会|思尔芯以数字EDA赋能产业生态,加速商业创新

国微芯执行总裁兼CTO白耿:国产EDA设计后端及制造端参与者寥寥无几

国微芯执行总裁兼CTO白耿:国产EDA设计后端及制造端参与者寥寥无几

评论