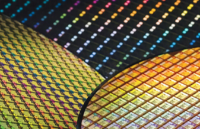

随着半导体工艺的不断进步,封装技术也在逐渐演变。晶圆级封装(Wafer-Level Packaging,WLP)和传统封装技术之间的差异,以及这两种技术在半导体行业的发展趋势和应用领域,值得我们深入了解。

一、晶圆级封装与传统封装的概述

晶圆级封装

晶圆级封装是一种直接在晶圆上进行封装的技术,将封装过程与生产过程融为一体。晶圆级封装在很大程度上减小了封装尺寸,降低了封装成本,并提高了生产效率。由于其具有较高的集成度、较低的功耗和较小的尺寸等优点,因此在高性能计算、物联网、移动通信等领域得到了广泛应用。

传统封装

传统封装技术是将芯片从晶圆中切割下来,然后通过封装将其与外部电路连接。这类封装技术包括:球栅阵列封装(Ball Grid Array,BGA)、塑料封装微型电路(Plastic Encapsulated Microcircuit,PEM)封装直接在晶圆上进行封装,因此可以实现更高的集成度。高集成度有助于减小信号传输延迟、降低功耗,同时提高芯片的性能。相反,传统封装技术由于其结构和连接方式的限制,很难实现更高的集成度。

成本

晶圆级封装由于减少了工艺流程,降低了封装材料的使用,因此在很大程度上降低了封装成本。而传统封装技术由于其复杂的工艺流程和额外的连接方式,使得成本相对较高。

热性能

晶圆级封装由于其较小的尺寸和较高的集成度,热阻相对较低,有助于提高热性能。而传统封装技术由于其较大的尺寸和较低的集成度,热性能相对较差。

可靠性

晶圆级封装在一定程度上提高了芯片的可靠性。传统封装技术由于其封装过程中多次切割和焊接,可能会导致封装内部的缺陷和应力,从而影响芯片的可靠性。

三、发展趋势与技术挑战

发展趋势

随着半导体行业对高性能、低功耗、小尺寸等需求的不断提高,晶圆级封装技术的发展趋势更加明显。特别是在高性能计算、物联网、移动通信等领域,晶圆级封装技术得到了广泛的应用。然而,传统封装技术在一些特定领域,如功率器件、光电器件等,仍具有一定的优势。

技术挑战

尽管晶圆级封装技术在很多方面具有优势,但其在实际应用中仍面临一些技术挑战。例如,晶圆级封装在尺寸缩小的同时,对晶圆的平整度和缺陷控制要求更高;同时,高集成度使得芯片内部的热管理和信号传输更为复杂。此外,由于晶圆级封装技术相对较新,行业内对于这一技术的经验和技术积累相对较少,这也给晶圆级封装的推广和应用带来了一定的挑战。

四、结论

晶圆级封装与传统封装技术在封装过程、尺寸、集成度、成本、热性能和可靠性等方面存在较大差异。随着半导体行业对高性能、低功耗、小尺寸等需求的不断提高,晶圆级封装技术日益受到关注,并在诸多领域得到广泛应用。然而,晶圆级封装在实际应用中仍面临诸多技术挑战,需要行业不断努力、探索和创新,以充分发挥其潜力。

未来,随着封装技术的不断发展,我们有理由相信,晶圆级封装技术将在各个领域取得更多突破,进一步推动半导体行业的繁荣发展。与此同时,传统封装技术在某些特定领域仍具有一定的优势,将继续为半导体行业的发展做出贡献。晶圆级封装与传统封装技术各有优缺点,两者在未来的发展中将相互补充、共同进步。

-

SMT设备

+关注

关注

2文章

33浏览量

9484 -

贴片机

+关注

关注

10文章

672浏览量

24592 -

回流焊

+关注

关注

14文章

541浏览量

18615

发布评论请先 登录

什么是晶圆级扇入封装技术

半导体封装新纪元:晶圆级封装掀起技术革命狂潮

半导体封装新纪元:晶圆级封装掀起技术革命狂潮

评论