继续讲解!通过最近两篇文章的程序就可以来验证下图中的文字!这也是经验获取的过程!那我的经验又是怎么获取的呢?主要是靠看大量的论文和书籍。在我们那个年代,互联网已经开始展现出它的魅力。我从互联网上下载了很多论文。现在的时代不一样了,不仅有文章,还会有视频讲解课程。我相信这些内容会对大家的学习有更大的帮助。

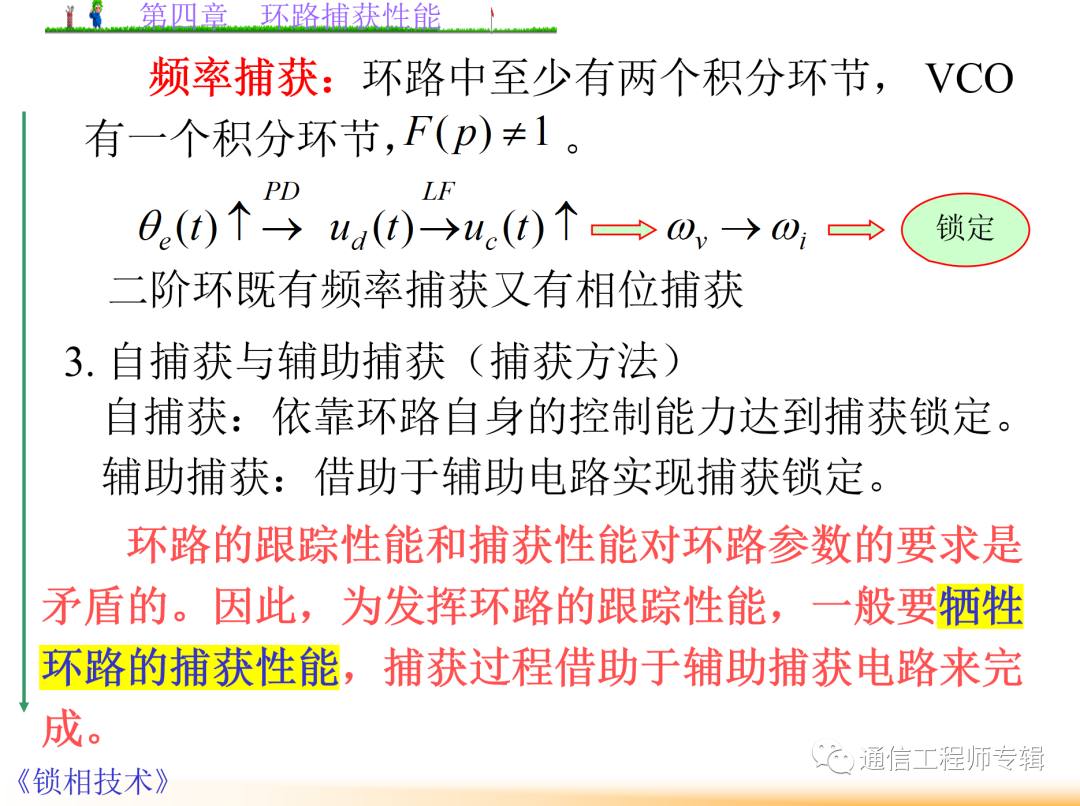

怎么理解牺牲环路的捕获性能!

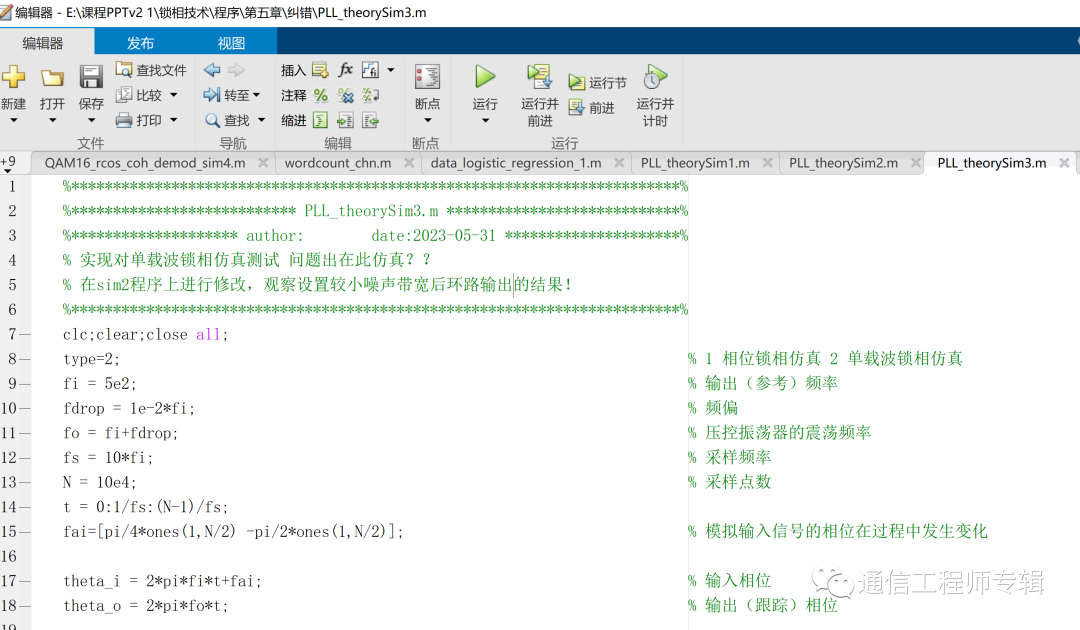

这就是环路中噪声带宽设置的折衷。设置的值大了,捕获带增加,捕获速度加快。但跟踪时残留的噪声大,不稳定性也增加。下面用仿真程序来说明这个概念!

% 二阶环路滤波系数

原文标题:大学毕业设计一席谈v2之十六 锁相环(12)代码分析加经验总结

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

通信网络

+关注

关注

22文章

2113浏览量

54462

原文标题:大学毕业设计一席谈v2之十六 锁相环(12) 代码分析加经验总结

文章出处:【微信号:gh_30373fc74387,微信公众号:通信工程师专辑】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

热点推荐

高性能低噪声锁相环LTC6948:设计与应用全解析

高性能低噪声锁相环LTC6948:设计与应用全解析 在电子工程师的日常工作中,高性能的锁相环(PLL)器件是实现精确频率控制和低噪声信号合成的关键。今天,我们就来深入探讨一款名为LTC6948

Altera公司锁相环IP核介绍

锁相环(PLL,Phase Lock Loop)的主要作用是实现输出时钟对输入参考时钟的相位与频率的精确跟踪和同步。锁相环(PLL)的主要模块包括相位频率检测器(PFD)、电荷泵、环路滤波器

探索CDC516:高性能3.3V锁相环时钟驱动器

探索CDC516:高性能3.3V锁相环时钟驱动器 在电子设计领域,时钟驱动器对于确保系统的稳定运行至关重要。今天我们要深入探讨的是德州仪器(Texas Instruments)的CDC516,一

CDC2516:高性能锁相环时钟驱动器的深度解析

: cdc2516.pdf 一、CDC2516概述 CDC2516是一款高性能、低偏斜、低抖动的锁相环(PLL)时钟驱动器,专为同步DRAM应用而设计。它工作在3.3V的VCC电压下,

CDC509:高性能3.3V锁相环时钟驱动器

CDC509:高性能3.3V锁相环时钟驱动器 在电子设计领域,时钟驱动是一项关键技术,尤其是在同步DRAM应用中,需要高精度、低抖动的时钟信号来确保数据的准确传输。德州仪器(Texas

CDCVF2505 3.3 - V 时钟锁相环时钟驱动器:设计与应用指南

的 CDCVF2505 3.3 - V 时钟锁相环时钟驱动器,看看它在同步 DRAM 和通用应用中能发挥怎样的作用。 文件下载: cdcvf2505.pdf 一、产品特性亮点 宽频率范围与低抖动

CDCVF25081:高性能锁相环时钟驱动器深度解析

,一款高性能、低偏斜、低抖动的锁相环(PLL)时钟驱动器。 文件下载: cdcvf25081.pdf 一、产品特性亮点 1. 架构与输出 CDCVF25081基于锁相环技术,是零延迟缓

TLC2932A高性能锁相环芯片详解:设计与应用指南

TLC2932A高性能锁相环芯片详解:设计与应用指南 在电子设计领域,锁相环(PLL)是一种至关重要的电路,它能够实现信号的相位同步和频率合成,广泛应用于通信、雷达、仪器仪表等众多领域。今天要给大家

探索TLC2933A高性能锁相环:特性、应用与设计要点

,了解其特性、工作原理及应用中的设计要点。 文件下载: tlc2933a.pdf 一、TLC2933A概述 TLC2933A专为锁相环系统设计,主要由电压控制振荡器(VCO)和边缘触发型相位频率检测器

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

该CDCVF2510是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用锁相环 (PLL) 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为

CDCVF2509 3.3V锁相环时钟驱动器技术文档总结

该CDCVF2509是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。该器件使用 PLL 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对齐。该器件专为与同步

CDCVF25081 3.3-V 锁相环时钟驱动器技术文档总结

CDCVF25081是一款高性能、低偏斜、低抖动、锁相环时钟驱动器。它使用 PLL 将输出时钟在频率和相位上精确对齐输入时钟信号。输出分为 2 个组,总共 8 个缓冲 CLKIN 输出。当不存在 CLKIN 信号时,该器件会自动

CDCVF2510A 3.3V锁相环时钟驱动器技术文档总结

该CDCVF2510A是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。该CDCVF2510A使用锁相环 (PLL) 将反馈 (FBOUT) 输出在频率和相位上精确对齐到时钟 (CLK

高压放大器在锁相环稳定重复频率研究中的应用

实验名称: 锁相环稳定重复频率的系统分析 实验内容: 针对重复频率的漂移,引入两套锁相环系统反馈控制两个激光器的重复频率,将其锁定在同一个稳定的时钟源上。本章主要阐述了经典

大学毕业设计一席谈v2之十六 锁相环(12) 代码分析加经验总结

大学毕业设计一席谈v2之十六 锁相环(12) 代码分析加经验总结

评论