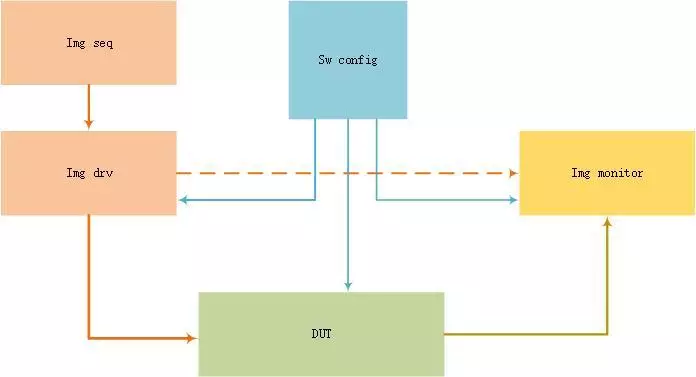

设计码完代码后,有时候想简单调试一下基本的通路,此时还没有验证资源进来,可以仿照modesim仿真的方法,创建一个.v/.sv的顶层,里面例化DUT,里面加预期激励;

下面是VCS/XRUN两种仿真工具最简单的demo,spi_slv.v是待测dut,tb_top.sv为顶层top,例化dut, 里面添加对应的激励;

1.VCSdemo:

步骤一:c bash下设置工具对应的环境变量(如果已经设置好,则忽略)

|

setenvNOVAS_HOME $ENVDIR/apps/synopsys/verdi/2017.03 setenvVERDI_HOME $ENVDIR/apps/synopsys/verdi/2017.03 setenvLD_LIBRARY_PATH$VERDI_HOME/share/PLI/lib/LINUX64:$VERDI_HOME/share/PLI/IUS/LINUX64/boot:$LD_LIBRARY_PATH |

步骤二:编译运行对应的.v/.sv 文件 + dumpfsdb所需要的pli

| vcs -full64 -R spi_master.v tb_top.sv +time_scale=1ns -debug_pp -LDFLAGS -rdynamic-P ${NOVAS_HOME}/share/PLI/VCS/LINUX64/novas.tab |

步骤三:例化顶层,添加fsdb dump 的系统函数, 添加激励

|

moduletb_top; wire SDO; wire SDI; wireSCLK; wireCS; spi_slv m_spi( .CS(CS), .SDO(SDI), .SDI(SDO), .SCLK(SCLK) ); initial begin #10000;// simulation time //TODO ADD code here $finish(); end initial begin $fsdbDumpfile("test.fsdb"); $fsdbDumpvars(0,tb_top); end endmodule |

步骤四:打开波形: verdi -f filelist.f -ssf test.fsdb

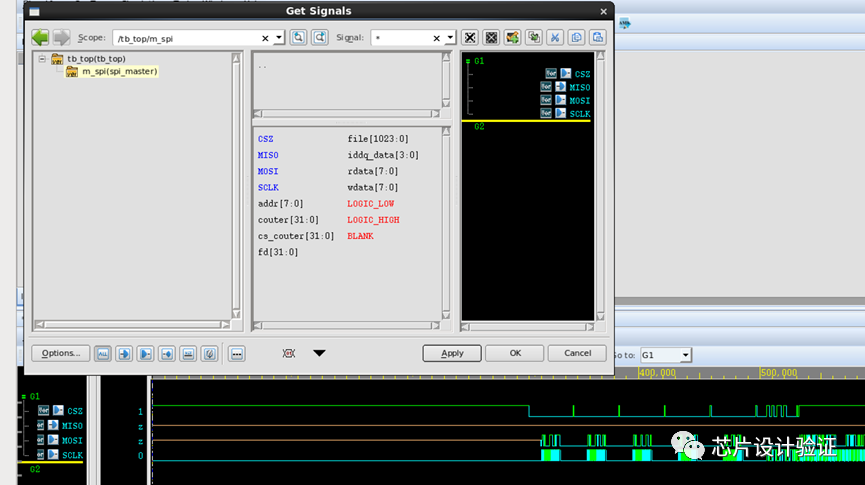

波形效果如下

2.XRUN demo:

步骤一:设置运行XRUN工具对应的环境变量

| 略 |

步骤二:编译运行对应的.v/.sv 文件 + dump shm 波形

| xrun-sv-c-elaboratespi_master.vtb_top.sv-accessrwc&&xrun-R-inputwave_dump.tcl |

wave_dump.tcl 文件:

|

database-open waves -into test.shm -default -event probetb_top -all -dynamic -depth all -tasks -functions -all -memories -variablestb_top run exit |

步骤三:例化顶层,添加激励

|

moduletb_top; wireSDO; wireSDI; wire SCLK; wireCS; spi_slv m_spi( .CS(CS), .SDO(SDI), .SDI(SDO), .SCLK(SCLK) ); initial begin #10000; //TODO ADD code here $finish(); end endmodule |

步骤四:打开波形:simvision test.shm

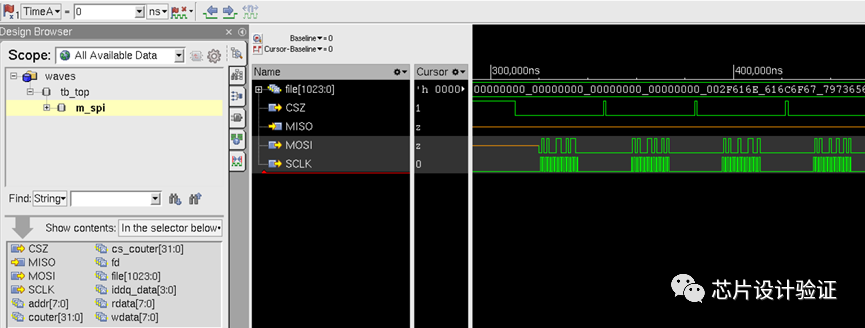

波形效果如下:

审核编辑:汤梓红

-

仿真

+关注

关注

53文章

4404浏览量

137644 -

UVM

+关注

关注

0文章

183浏览量

19938 -

VCS

+关注

关注

0文章

80浏览量

10232 -

编译

+关注

关注

0文章

687浏览量

34935 -

仿真环境

+关注

关注

0文章

4浏览量

5328

原文标题:VCS/XRUN如何创建一个非UVM的简单仿真环境?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

vcs和xrun搭配uvm1.1/uvm1.2版本库的使用情况

IC验证之UVM常用宏汇总分析(四)

IC验证"一个简单的UVM验证平台"是如何搭建的(六)

请问一下在UVM中的UVMsequences是什么意思啊

使用VCS仿真Vivado IP核时遇到的问题及解决方案

浅谈VCS的两种仿真flow

VCS独立仿真Vivado IP核的一些方法总结

VCS/XRUN如何创建一个非UVM的简单仿真环境?

VCS/XRUN如何创建一个非UVM的简单仿真环境?

评论